US5S106一款高性能、低偏斜时钟扇出缓冲器,此缓冲器可将一路单端输入分配到6路低抖动LVCMOS时钟输出。上电后,输出默认状态为低。当控制引脚(1G)保持低电平并且在CLK输入上检测到负时钟边沿时,将输出置于低位状态;当控制引脚(1G)保持高电平且CLK输入上检测到负时钟边沿时,可以将输出切换到缓冲模式。该产品完全兼容LMK1C1106/CDCLVC1106/5PB1106PPG。

特性

单端LVCMOS输出

LVCMOS频率高达200MHz

附加抖动:25fs(10kHz-20MHz@156.25MHz )

输出间偏斜:10ps

器件间偏斜:30ps(最大值)

输入输出延迟:低于2ns(典型值)

单端LVCMOS/LVTTL/HSTL输入

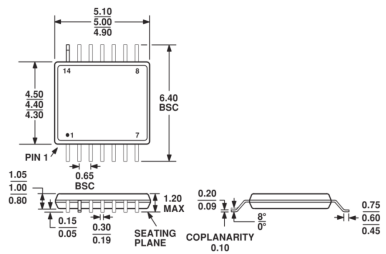

14-Pin TSSOP封装尺寸图(单位:mm)