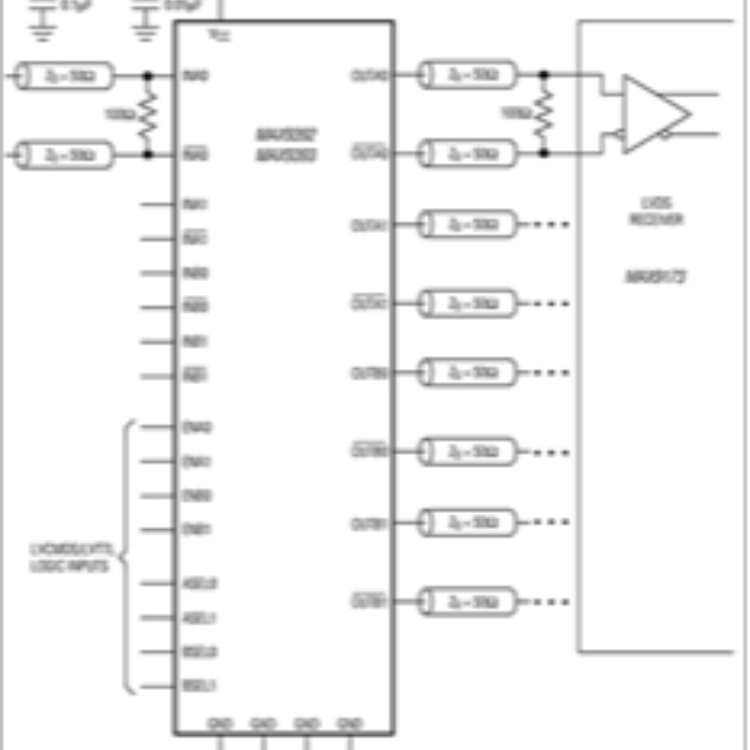

MAX9392/MAX9393双2 x 2交叉点开关能够实现高速、低功耗、低噪声信号切换。MAX9392/MAX9393将两路差分输入中的一路复用到一路或两路低压差分信号(LVDS)输出。独立的使能输入对每路差分信号进行通、断控制。

4路 LVCMOS/LVTTL逻辑输入(每通道两个)控制输入与输出之间的内部连接。可灵活实现以下配置:2 x 2交叉开关、2:1复用器、1:2分配器或双转发器,从而使MAX9392/MAX9393可理想用作故障容错系统中的保护开关、诊断器中的环回开关、时钟/数据分配中的扇出缓冲器和信号恢复。

当输入未被驱动或共模电压超出指定范围时,故障保护电路将输出拉至差分低电平。MAX9392为LVDS、HSTL和其它以GND为参考的差分输入提供高电平输入失效检测;MAX9393为LVPECL、CML和其它以VCC为参考的差分输入提供低电平输入失效检测。

具有98ps(P-P) (最大值)超低抖动的伪随机序列(PRBS)能够在对定时误差高度敏感的高速链路中保证可靠通信,特别适合需要时钟和数据恢复的应用,或串行器和解串器应用。高速开关性能确保工作在1.5GHz,并保证小于67ps (最大值)的通道间偏差。

LVDS输入、输出兼容于TIA/EIA-644 LVDS标准,LVDS输出可驱动100Ω负载。MAX9392/MAX9393提供32引脚TQFP封装,工作在-40°C至+85°C扩展级温度范围。

交叉切换产品请参考MAX9390/MAX9391。

应用

- 局端背板时钟分配

- DSLAM

- 故障容错系统

- 高速电信/数据通信设备

- 保护开关

- 250mV差分输出摆幅,可工作在1.5GHz

- 2psRMS (最大)随机抖动

- 交流指标保证接受150mV差分输入

- 信号输入可接受任何差分信号标准

- 用于时钟或高速数据的LVDS输出

- 高电平输入失效检测(MAX9392)

- 低电平输入失效检测(MAX9393)

- 3.0V至3.6V供电范围

- LVCMOS/LVTTL逻辑输入控制信号切换

ADCLK954

ADCLK914

ADCLK905

ADCLK907

ADCLK925

AD9513

AD9515

AD9514

MAX3841

MAX9392

MAX9393

MAX9394

MAX9390

MAX9176

MAX9389

MAX9388

MAX9321

MAX9321B

MAX9180

MAX3783

MAX9155

MAX9152

MAX3840