verilog adder

在 Verilog 中,加法器(Adder)是实现二进制加法的基本电路单元。以下是不同类型的加法器实现及其特点:

1. 半加器(Half Adder)

处理 1 位二进制加法,不考虑进位输入:

module half_adder(

input a, b,

output sum, cout

);

assign sum = a ^ b; // 异或:和输出

assign cout = a & b; // 与:进位输出

endmodule2. 全加器(Full Adder)

处理 1 位加法,支持进位输入:

module full_adder(

input a, b, cin,

output sum, cout

);

assign sum = a ^ b ^ cin;

assign cout = (a & b) | (b & cin) | (a & cin);

endmodule3. 行波进位加法器(Ripple Carry Adder)

级联全加器实现多位加法,结构简单但延迟较高:

module ripple_adder #(parameter N=4)(

input [N-1:0] a, b,

input cin,

output [N-1:0] sum,

output cout

);

wire [N:0] carry;

assign carry[0] = cin;

genvar i;

generate

for (i=0; i<N; i=i+1) begin: adder_chain

full_adder fa(

.a(a[i]),

.b(b[i]),

.cin(carry[i]),

.sum(sum[i]),

.cout(carry[i+1])

);

end

endgenerate

assign cout = carry[N];

endmodule4. 行为级加法器(Behavioral Adder)

直接使用 + 运算符,由综合工具自动优化:

module behavioral_adder #(parameter N=4)(

input [N-1:0] a, b,

input cin,

output [N-1:0] sum,

output cout

);

assign {cout, sum} = a + b + cin;

endmodule关键区别

| 类型 | 延迟特性 | 硬件开销 | 代码复杂度 | 适用场景 |

|---|---|---|---|---|

| 行波进位加法器 | 高(O(N)) | 低 | 中 | 低速小位宽设计 |

| 超前进位加法器 | 低(O(log N)) | 高 | 高 | 高速设计 |

| 行为级加法器 | 工具自动优化 | 可变 | 低 | 通用场景 |

建议:实际开发中优先使用行为级描述(

a + b),综合工具会自动选择最优结构(如超前进位加法器)。如需手动控制电路结构(如低功耗设计),再考虑结构化实现。

通过以上代码示例,您可以根据需求选择适合的加法器实现方式。

Verilog 与 ASIC 设计的关系 Verilog 代码优化技巧

Verilog与ASIC设计的关系 Verilog作为一种硬件描述语言(HDL),在ASIC设计中扮演着至关重要的角色。ASIC(Application Specific Integrated

2024-12-17 09:52:26

Verilog 测试平台设计方法 Verilog FPGA开发指南

Verilog测试平台设计方法是Verilog FPGA开发中的重要环节,它用于验证Verilog设计的正确性和性能。以下是一个详细的

2024-12-17 09:50:06

Verilog与VHDL的比较 Verilog HDL编程技巧

Verilog 与 VHDL 比较 1. 语法和风格 Verilog :Verilog 的语法更接近于 C 语言,对于有 C 语言背景的工程师来

2024-12-17 09:44:44

Verilog黄金参考指南资料免费下载

Verilog黄金参考指南是一个紧凑的快速参考指南Verilog硬件描述语言,其语法,语义,综合和应用程序的硬件设计。

资料下载

佚名

2021-02-01 15:37:00

Verilog教程之Verilog HDL程序设计语句和描述方式

本文档的主要内容详细介绍的是Verilog教程之Verilog HDL程序设计语句和描述方式。

资料下载

佚名

2020-12-09 11:24:23

Verilog HDL的基础知识详细说明

硬件描述语言基本语法和实践 (1)VHDL 和Verilog HDL的各自特点和应用范围 (2)Verilog HDL基本结构语言要素与语法规则 (3)

资料下载

佚名

2019-07-03 17:36:00

verilog function函数的用法

Verilog 是一种硬件描述语言 (HDL),主要用于描述数字电子电路的行为和结构。在 Verilog 中,函数 (Function) 是一种用于执行特定任务并返回一个值的可重用代码块。函数在

2024-02-22 15:49:27

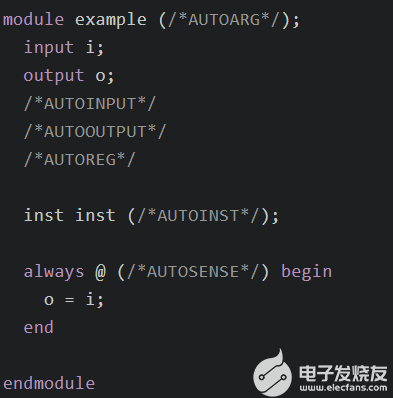

Emacs的verilog-mode介绍

Verilog-mode是由Michael McNamara mac@verilog.com和Wilson Snyder wsnyder@wsnyder.org编写。难能可贵的是,这个

2023-01-24 17:01:00

FPGA中如何使用Verilog处理图像

该FPGA项目旨在详细展示如何使用Verilog处理图像,从Verilog中读取输入位图图像(.bmp),处理并将处理结果写入Verilog中的

2021-09-23 15:50:21

如何使用Icarus Verilog+GTKWave来进行verilog文件的编译和仿真

本文将介绍如何使用Icarus Verilog+GTKWave来进行verilog文件的编译和仿真。 Icarus Verilog Icarus

2021-07-27 09:16:50

如何用参数化加法器树编写Verilog

on how to write Verilog for parameterized adder tree with the input parameter being the number of operands?

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 芯片的工作原理是什么?

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- ssd是什么意思

- 什么是蓝牙?它的主要作用是什么?

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- dtmb信号覆盖城市查询

- 中科院研发成功2nm光刻机

- 苹果手机哪几个支持无线充电的?

- type-c四根线接法图解

- 华为芯片为什么受制于美国?

- 怎样挑选路由器?

- 元宇宙概念股龙头一览

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- 复位电路的原理及作用

- BLDC电机技术分析

- dsp是什么意思?有什么作用?

- 苹果无线充电器怎么使用?

- iphone13promax电池容量是多少毫安

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 传感器常见类型有哪些?

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机