如何实现锁相环电源管理与环路滤波器的设计?有何要求?

锁相环最初用于改善电视接收机的行同步和帧同步,以提高抗干扰能力。20世纪50年代后期随着空间技术的发展,锁相环用于对宇宙飞行目标的跟踪、遥测和遥控。

好的,我们来详细探讨一下锁相环中的电源管理和环路滤波器设计的实现方法和关键要求。这两个部分是高性能PLL设计的关键,直接影响锁定时间、相位噪声、杂散抑制和整体稳定性。

第一部分:锁相环电源管理

电源管理是保证PLL性能,尤其是相位噪声和杂散性能的核心。PLL中的关键模拟模块(如VCO、电荷泵、压控振荡器缓冲器、分频器核心等)对电源噪声极其敏感。

实现方法

-

关键模块独立供电:

- 分区供电: 将PLL的关键模拟模块的电源与数字电路(如分频器逻辑部分、锁存器)、以及其他大电流负载的电源分离。

- 专用电源引脚: 在芯片设计或PCB设计中,为VCO、CP等关键模块提供专用的电源引脚

(AVDD_PLL, VCO_VDD, CP_VDD)。这样可以将外部噪声和内部数字噪声有效隔离。

-

低噪声电源源:

- 高质量LDO(低压差稳压器): 使用超低噪声、高PSRR的LDO为PLL关键模块供电。这是最常见和有效的方法。

- 要求: LDO的噪声密度要极低(如<10μVrms/√Hz或更低,具体由系统噪声要求决定),并且在目标频率范围内(通常是数kHz到数十MHz)具有高PSRR。PSRR需要在VCO振荡频率和边带偏移频率(如100kHz, 1MHz, 10MHz)处足够高,才能有效抑制开关电源的噪声和纹波。

- 旁路电容: LDO输入输出都需要高质量的去耦电容。输出端通常需要不同容值的组合(如10μF + 100nF + 1nF)。

- 电池供电/线性调节器: 对于对噪声极度敏感的应用(如高速串行链路SerDes时钟或射频本振),有时会直接使用电池供电或低噪声的线性调节器。

- 避免开关电源直连: 严禁将开关电源(SMPS)的输出直接连接到PLL模拟关键模块的电源上。如果需要使用SMPS,必须在其输出后级联一个高PSRR的LDO。

- 高质量LDO(低压差稳压器): 使用超低噪声、高PSRR的LDO为PLL关键模块供电。这是最常见和有效的方法。

-

有效的电源去耦:

- 多层板设计(PCB): 使用专门的电源层和接地层,提供低阻抗的电源和地回路。

- 精心选择去耦电容:

- 类型: 优选低ESR(等效串联电阻)、低ESL(等效串联电感)的陶瓷电容(如X7R, X5R)。高频去耦可考虑C0G/NP0电容。钽电容可用于低频段的大容量滤波。

- 多容值组合: 在不同位置放置不同容值的电容组(如1μF, 100nF, 10nF, 1nF,100pF)。目的是在宽频率范围内提供低阻抗路径(抑制不同频率的噪声)。

- 摆放位置: 极尽靠近芯片的电源和地引脚,最小化环路面积(减小寄生电感)。连接线应短而宽。

- 过孔: 连接去耦电容到电源/地层时,使用足够的过孔以降低阻抗。

-

接地策略:

- 模拟地/数字地分离与单点连接(Star Point):

- 分离PLL的模拟地

(AGND_PLL, VCO_GND, CP_GND)和数字地(DGND)。 - 在PCB或封装上的一个特定点(通常在芯片电源地引脚附近)实现两者的连接。

- 分离PLL的模拟地

- 连续接地平面: 为AGND提供完整的、低阻抗的接地面。

- 避免地环路: 防止接地路径形成大环路,这容易引入噪声。

- 模拟地/数字地分离与单点连接(Star Point):

关键要求

- 低电源噪声: PLL关键模拟模块供电轨上的噪声(RMS值或PSD谱密度)必须足够低,以满足系统对相位噪声和杂散的严格要求。

- 高PSRR: 无论是LDO还是整个电源树,都需要在关注的频率范围内(特别是VCO振荡频率及其周围的偏移频率)具有高电源抑制比。

- 低阻抗电源通路: 去耦网络和电源平面设计要确保电源回路的阻抗在目标频率下足够低。

- 噪声隔离: 有效隔离高噪声的数字电源和开关电源对PLL关键模拟模块电源的干扰。

- 稳定性: LDO本身在其工作点必须是稳定的(无振荡)。

第二部分:环路滤波器设计

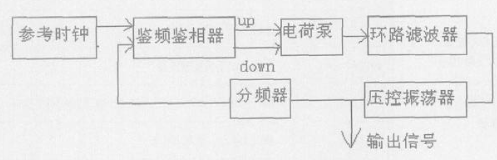

环路滤波器位于电荷泵输出端和VCO输入端之间,是PLL反馈回路的“大脑”。它将电荷泵输出的电流脉冲平滑为驱动VCO的控制电压,并决定环路的稳定性、带宽、瞬态响应和噪声性能。

实现方法(以典型二阶/三阶无源滤波器为例)

-

定义关键目标参数:

- 环路带宽(ω_c / f_c): 通常以Hz或rad/s表示。决定了环路的跟踪速度和噪声带宽。需要权衡:带宽越宽,锁定时间越快,但对VCO噪声抑制越好;带宽越窄,对参考/分频/CP噪声抑制越好,但锁定时间越慢。典型值从几百Hz到几MHz不等。

- 相位裕度(PM): 系统稳定性的度量,通常设计在45° - 65°之间(50° - 60°是比较稳健的选择)。过低的PM会导致过冲大、锁定时间长甚至不稳定;过高的PM会使系统响应变慢。

- 阻尼因子(ζ): 对于二阶系统,ζ 决定瞬态响应的特性(欠阻尼有振荡,过阻尼响应慢),通常选择 0.707(Butterworth响应)左右以达到合理的响应速度和过冲的平衡。

-

确定元器件值(经典二阶无源滤波器):

- 结构:

C1并联在CP输出(到地),串联电阻R1接C2到地。Vctrl取自R1和C2的连接点。 - 设计方程 (基于类型2 PLL):

ω_n² = (I_cp * K_vco) / (C2 * N)(自然角频率平方)ζ = (ω_n * C1 * R1) / 2(阻尼因子)- 环路带宽

ω_c ≈ ω_n * (2ζ + 1/(2ζ))^(1/2)(对于设计在45° - 60° PM的系统,ω_c ≈ ω_n * (2ζ)) - 相位裕度

PM ≈ arctan(ω_c R1 C1) - arctan(ω_c R1 * [C1 C2 / (C1 + C2)])

- 设计步骤:

- 确定

I_cp(电荷泵电流),K_vco(VCO增益,Hz/V),N(分频比)。 - 选择目标环路带宽

f_c(或ω_c) 和相位裕度PM(或阻尼因子ζ)。 - 计算所需的

C1,C2,R1值以满足ω_c和PM。可以借助软件工具(Matlab, Python, PLLWizard等)求解方程。

- 确定

- 高阶滤波器(三阶): 为了抑制CP产生的纹波在高频产生的杂散(参考杂散的谐波),需要在

C2两端再并联一个电容C3。C3的值通常远小于C2(例如C2/10到C2/20)。C3引入的极点为f_p = 1 / (2π R1 C3),应设置在环路带宽的3-5倍以外(例如,f_c = 100kHz,f_p ≈ 300kHz)。设计三阶滤波器时还需保证足够的PM。

- 结构:

-

元器件选择要求:

- 电阻: 优选低温度系数(如<100ppm/℃)的薄膜电阻(如Thin Film),以减少参数漂移。阻值通常在几KΩ到几十KΩ范围。

- 电容: 首选高质量、低损耗、低漏电流(high leakage causes ripple and drifting)、低电压系数的电容。

- C1/C2/C3: 首选 C0G(NP0) 陶瓷电容(非常好的温度稳定性和低损耗)。在要求稍低或低频时可用X7R/X5R,但它们有明显电压系数和温度漂移。钽电容漏电流较大,一般不推荐。避免使用Y5V电容。

- 布局布线:

- 滤波器电阻电容应尽量靠近芯片的CP输出和VCO输入引脚放置。

Vctrl走线要短、直、宽,避免耦合噪声或引入寄生。必要时可用保护走线(Guard Trace)。- 避免CP输出到VCO输入附近放置大电流或高速数字信号线。

关键要求

- 稳定性: 保证在PVT(工艺、电压、温度)变化范围内有足够的相位裕度(>45°是基本要求)。

- 抑制噪声和杂散:

- 低通特性抑制来自参考源、分频器、电荷泵的高频噪声。

- 高阶滤波(三阶)有效抑制电荷泵输出纹波(开关动作和电流失配引起),减少参考杂散(Reference Spurious)。

- 低控制电压纹波: 滤波器应有效平滑CP脉冲电流,使

Vctrl电压尽可能稳定(低纹波),降低VCO输出相位噪声和调制。 - 设定环路带宽和动态性能: 精准控制环路带宽和瞬态响应(锁定时间、过冲、阻尼)。

- 对PVT变化的鲁棒性: 电阻电容值的变化(尤其是温度变化)不应导致环路变得不稳定或性能急剧下降(如过冲过大或锁定时间太长)。选择稳定的元器件(低TC)有助于此。

总结

- 电源管理: 核心是降噪和隔离。使用LDO、分区供电、多层板、精细的去耦电容选择和布局,最大化PSRR,最小化关键点的噪声电压。

- 环路滤波器: 核心是调谐动态响应(带宽、稳定性)和滤除噪声/杂散。准确计算并选择合适的器件值,使用高质量的电阻和C0G电容,并进行优化的布局布线。

这两方面紧密相关:即使是最好的环路滤波器设计,如果电源噪声很大,最终PLL的相位噪声和杂散性能也难以达标。同样,电源很干净,但滤波器设计错误导致不稳定或带宽不对,环路也无法正常工作。高性能PLL设计必须同时精心优化这两者,并进行广泛的仿真和测试验证(尤其是在不同PVT条件下)。

锁相环CD4046原理及应用

锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

资料下载

![]() 姚小熊27

2021-06-21 15:13:55

姚小熊27

2021-06-21 15:13:55

使用MC145170锁相环实现调频锁相环收音机的PCB原理图免费下载

本文档的主要内容详细介绍的是使用MC145170锁相环实现调频锁相环收音机的PCB原理图免费下载。

资料下载

佚名

2020-11-02 17:15:00

关于锁相环的组成你了解多少?

锁相环路是一种反馈控制电路,简称锁相环(PLL)。许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 芯片的工作原理是什么?

- ssd是什么意思

- 什么是蓝牙?它的主要作用是什么?

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- 中科院研发成功2nm光刻机

- 苹果手机哪几个支持无线充电的?

- dtmb信号覆盖城市查询

- 怎样挑选路由器?

- 华为芯片为什么受制于美国?

- 元宇宙概念股龙头一览

- type-c四根线接法图解

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- BLDC电机技术分析

- 复位电路的原理及作用

- dsp是什么意思?有什么作用?

- iphone13promax电池容量是多少毫安

- 苹果无线充电器怎么使用?

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 传感器常见类型有哪些?

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机