Verilog HDL语言与VHDL语言在设计程序编写中有哪些区别之处?

Verilog HDL语言提供了编程语言接口,通过该接口可以在模拟、验证期间从设计外部访问设计,包括模拟的具体控制和运行。

好的,Verilog HDL 和 VHDL 是两种最主流的硬件描述语言(HDL),它们在设计程序编写中存在诸多区别,主要体现在以下几个方面:

-

语言风格与根源:

- Verilog: 语法更接近 C 语言,风格相对自由简洁,对于有软件编程背景(尤其是 C)的工程师来说,更容易上手和阅读。它的设计初衷是用于仿真和测试。

- VHDL: 语法源于 Ada 和 Pascal 语言,风格非常严谨、冗长(Verbose),强制性强类型系统,更像是强类型的过程化语言。它最初是为美国国防部(DoD)设计规范而开发的,强调设计的精确描述和文档化。

-

数据类型系统:

- Verilog: 内置数据类型相对简单,基本类型是

reg和wire(四值逻辑:0, 1, X, Z)。reg不直接等同于硬件寄存器,它在过程块中被赋值。组合逻辑通常用wire(连续赋值)或reg(在always @*块中)。整数类型(integer,int)、实数、时间等比较直接。类型检查较宽松(弱类型),易发生意外类型转换。SystemVerilog 大幅增强了类型系统(枚举、结构体、联合、logic类型等)。 - VHDL: 非常强大的强类型系统 (Strongly Typed)。基本物理类型是

std_logic(九值逻辑:’U’, ‘X’, ‘0’, ‘1’, ‘Z’, ‘W’, ‘L’, ‘H’, ‘-‘)和std_logic_vector(位矢量)。提供了丰富的预定义类型:整数(有范围)、枚举、浮点数、物理量(带单位的时间、电压等)。允许用户自定义类型(枚举、数组、记录(结构体)、子类型),这有助于构建抽象层次更高、更不易出错、可读性更强的模型。对类型匹配要求极其严格,赋值、比较、运算等都必须在匹配的类型间进行,编译时就能捕获很多低级错误。

- Verilog: 内置数据类型相对简单,基本类型是

-

层次化结构与描述方法:

- Verilog: 模块(

module)是其基本构建单元。实例化模块用模块名加实例名列表(顺序关联)或端口名显式关联(.端口名(信号名))。过程块(always,initial)和连续赋值(assign)是主要描述手段。initial块主要用于仿真测试台。always块用于描述时序逻辑(always @(posedge clk))和组合逻辑(always @*或always @(敏感列表))。描述层次主要通过模块实例化实现。支持generate块进行参数化建模。 - VHDL: 实体-结构体(

entity-architecture)是基本构建单位。实体定义端口,结构体定义内部实现。实例化组件(component)通常在结构体声明部分声明(虽然也支持直接实例化库中的实体),然后在结构体主体中使用port map(端口映射,显式关联)进行实例化。行为描述主要通过进程(process) 块(内部顺序执行,外部并行执行)和并发信号赋值(concurrent signal assignment)语句实现。支持配置声明(configuration) 来显式绑定实体和特定的结构体实现,这在管理复杂的层次结构或替换不同实现时很有用。支持generate语句进行参数化建模。

- Verilog: 模块(

-

行为描述(时序模型):

- Verilog: 时间模型基于离散事件仿真(Discrete Event Simulation)。

begin...end块内是顺序执行,不同块之间是并行执行(并发)。对阻塞赋值(=)和非阻塞赋值(<=)的选择至关重要:- 阻塞赋值: 在过程块内立即生效,顺序执行,常用于组合逻辑建模。

- 非阻塞赋值: 在过程块结束时才更新目标变量,所有右边的表达式在赋值前被计算,避免竞争冒险,必须用于时序逻辑建模。

- VHDL: 同样基于离散事件仿真。在同一个进程(

process)内,信号赋值不会立即生效,而是在进程挂起(运行到wait或遇到敏感信号列表末尾)并且所有活跃的进程都执行完当前模拟周期后才会更新(δ delay后)。变量赋值(variable :=)是立即生效的。信号赋值(signal <=)是计划在下一个模拟周期(即当前模拟时间点上δ delay之后)执行。精确的时序模型(包括δ delay概念)对于理解信号行为非常重要。

- Verilog: 时间模型基于离散事件仿真(Discrete Event Simulation)。

-

并发与顺序性:

- Verilog:

initial块只在仿真开始时执行一次(主要用于测试台)。always块根据敏感列表变化反复执行。连续赋值(assign)描述并发逻辑。模块实例化是并发执行的。 - VHDL: 结构体内部的语句是并发(Concurrent)的,它们之间没有隐含的顺序。进程(

process)本身是一个并发语句。进程内部的语句是顺序(Sequential) 执行的(类似软件程序)。进程只在遇到它的敏感列表(process(sensitivity_list))或显式的wait语句时暂停。没有敏感列表的进程必须包含一个wait语句以防止无限循环。

- Verilog:

-

测试平台支持:

- Verilog: 原生测试平台功能较弱(主要靠

initial,$display,$monitor,$stop等)。SystemVerilog 的出现极大地改变了这一点,它引入了强大的面向对象编程(OOP)、约束随机测试、功能覆盖、断言(SVA)等高级验证特性,使其在现代验证流程中成为主导。 - VHDL: 标准包含测试平台的构造(

assert,report),配合文件操作、过程/函数等可以构建复杂测试台。但对于高级验证方法学(如约束随机、覆盖率驱动),需要额外库支持(如OSVVL - Open Source VHDL Verification Methodology)。

- Verilog: 原生测试平台功能较弱(主要靠

-

复杂性与学习曲线:

- Verilog: 语法简洁直观,入门相对容易(尤其对C/C++程序员)。但要真正掌握硬件设计精髓(尤其是正确处理阻塞/非阻塞赋值)需要深入理解。

- VHDL: 入门门槛较高,语法冗长且规则更严格(强类型),学习曲线较陡峭。但其严谨性常常能在早期捕获错误,编写的代码结构往往更清晰(在大型项目中优势更明显)。

-

库与工具支持:

- Verilog (特别是 SystemVerilog): 广泛的业界支持,是大多数EDA工具链(仿真、综合、形式验证)的首要或并行支持语言。在ASIC设计和大型FPGA设计中非常流行。IP核生态系统中 SystemVerilog 越来越普遍。

- VHDL: 在国防、航空航天、特定FPGA供应商(如 Intel/Altera 的部分遗留设计)、欧洲学术界和部分工业领域有深厚基础。EDA工具普遍支持,但其高级验证特性依赖OSVVL等额外库。IEEE预定义库(如

std_logic_1164,numeric_std)非常成熟和标准。

总结关键区别:

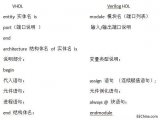

| 特征 | Verilog / SystemVerilog | VHDL |

|---|---|---|

| 语言风格 | 类C,较简洁自由 | 类Ada/Pascal,非常严谨冗长 |

| 类型系统 | 弱类型(原生Verilog), 强类型(SystemVerilog) | 极其强类型 |

| 基本结构 | module |

entity + architecture |

| 实例化方式 | 直接实例化(module_name inst_name(...)或.port(connect)) |

component声明 + port map (或直接实例化库实体) + configuration (可选) |

| 组合逻辑建模 | assign / always @* + =(阻塞) |

并发信号赋值 / process (敏感所有输入) + 变量/信号赋值(变量通常更好) |

| 时序逻辑建模 | always @(posedge clk) + <=(非阻塞) |

process(clk) + if rising_edge(clk) + <= |

| 仿真行为块 | initial, always |

process |

| 赋值行为 | 阻塞(=) & 非阻塞(<=) 非常关键 |

信号赋值(<=)计划在下一个δ生效 / 变量赋值(:=)立即生效 |

| 测试平台/验证 | 基本能力(SystemVerilog 非常强大) | 基本能力 + 需OSVVL等库支持 |

| 学习曲线 | 入门较易,掌握时序逻辑赋值需理解 | 入门门槛较高,需理解类型和信号更新机制 |

| 主要优势/场景 | 简洁流行(特别SystemVerilog),IP丰富,业界主流 | 严谨精确、文档化强、类型安全、航空航天/国防/部分FPGA/学术 |

简单来说:

- 想尽快上手,尤其有C背景的:从Verilog入门。

- 做严谨规范的大型项目或系统设计,注重强类型安全和前期错误捕获:VHDL可能是好选择。

- 现代复杂验证驱动设计:SystemVerilog几乎是(尤其是ASIC)业界验证事实标准。

- 具体设计领域(国防、航天):可能更常用VHDL。

- FPGA设计/IP使用:通常两种都需要掌握,很多公司或IP同时提供两种接口。

实际选择常取决于公司历史、项目要求、目标平台和个人/团队熟悉程度。掌握两者的基本概念对理解HDL设计和工具行为非常有帮助。越来越多的工程师倾向于学习 SystemVerilog(作为Verilog的超集) 来覆盖RTL设计和验证的大部分需求,同时根据项目需要掌握VHDL知识。

Verilog与VHDL的比较 Verilog HDL编程技巧

:由于其类似于 C 语言的语法,Verilog 代码通常更易于阅读和维护,尤其是在处理复杂逻辑时。

2024-12-17 09:44:44

Verilog HDL verilog hdl和vhdl的区别

Verilog HDL是一种以文本形式描述数字系统硬件的结构和行为的硬件描述语言,也可描述逻辑电路图、逻辑表达式等。

2021-07-23 14:36:55

Verilog HDL语言的发展历史和主要能力

和VHDL是世界上最流行的两种硬件描述语言,都是在20世纪80年代中期开发出来的。前者由Gateway Design Automation公司(

资料下载

![]() 中书省

2023-08-29 15:58:29

中书省

2023-08-29 15:58:29

三态门原理HDL语言DSP和ARM总线的仿真及Modelsim使用教程资料

本文档的主要内容详细介绍的是三态门原理HDL语言DSP和ARM总线的仿真及Modelsim使用教程资料主要内容包括了:1 ModelSimSE的使用流程,2 一个

资料下载

佚名

2019-07-09 16:49:27

Verilog HDL和VHDL的区别

和VHDL是世界上最流行的两种硬件描述语言,都是在20世纪80年代中期开发出来的。前者由Gateway Design Automation公司(

2020-06-17 16:13:11

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 芯片的工作原理是什么?

- ssd是什么意思

- 什么是蓝牙?它的主要作用是什么?

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- 中科院研发成功2nm光刻机

- 苹果手机哪几个支持无线充电的?

- dtmb信号覆盖城市查询

- 怎样挑选路由器?

- 华为芯片为什么受制于美国?

- 元宇宙概念股龙头一览

- type-c四根线接法图解

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- BLDC电机技术分析

- 复位电路的原理及作用

- dsp是什么意思?有什么作用?

- iphone13promax电池容量是多少毫安

- 苹果无线充电器怎么使用?

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 传感器常见类型有哪些?

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机