ad pcb重叠式封装

更多

在 Altium Designer (AD) 的 PCB 设计语境中,“重叠式封装” 通常指以下几种情况及其解决方法:

-

布局时元件物理重叠:

- 含义: 两个或多个元件的物理轮廓(边界框)在 PCB 板面上占据了相同的空间区域。这在制造和装配上是绝对不允许的,会导致元件无法放置或短路。

- 解决方法:

- 移动元件: 这是最直接的解决方法。选中重叠的元件,将它们拖拽到板面上合适的位置,确保它们之间有足够的间距满足设计规则。

- 检查设计规则 (DRC): Altium Designer 的 设计规则检查器 (Design Rule Checker, DRC) 是防止和检测重叠的关键工具。确保启用并正确配置了

Component Clearance(元件间距) 规则。- 快捷键

T->D(Tools -> Design Rule Check...)。 - 在

Rules To Check中,找到并勾选Component Clearance类别下的规则(通常默认已启用)。 - 运行 DRC (

Run Design Rule Check)。任何重叠的元件都会被标记为冲突(通常在Messages面板和板面上以绿色波浪线/高亮显示)。

- 快捷键

- 查看冲突报告: 运行 DRC 后,仔细查看

Messages面板中的冲突详情,它会列出哪些元件发生了重叠或间距违规。双击消息可以定位到具体位置。 - 对齐和排列工具: 使用 AD 提供的对齐 (

A) 和排列工具来整齐摆放元件,避免无意识的重叠。

-

3D 模型重叠 (机械冲突):

- 含义: 元件的 STEP 3D 模型在三维空间上发生了穿透或重叠。这发生在较高元件(如高电容、散热器、连接器)放置在较低元件(如电阻、芯片)上方,或者元件离外壳/结构件太近时。可能导致组装干涉。

- 解决方法:

- 启用 3D DRC: AD 具有强大的 3D 设计规则检查功能。

- 确保在

Tools->Preferences->PCB Editor->General中勾选了Allow 3D View to lock objects(通常默认勾选)。 - 在 PCB 编辑器中,按快捷键

3切换到 3D 视图。 - 在

Tools->Preferences->PCB Editor->3D Models中,确保启用了Perform Collision Detection。 - 在

Design->Rules...中,检查并配置Placement->Component Body 3D规则。这个规则定义了元件 3D 体之间的最小允许间隙。 - 运行 DRC (包括 3D 检查)。任何 3D 冲突也会被报告。

- 确保在

- 调整元件位置: 在 3D 视图中 (

3) 直观地检查是否有重叠。发现重叠后,切换回 2D 视图 (2) 或在 3D 视图中直接移动元件,调整它们的位置或方向,消除干涉。 - 检查元件高度: 确认重叠元件的封装定义中(在 PCB 库中),

Height属性设置正确,这直接影响其 3D 模型的碰撞检测范围。 - 考虑垂直空间: 在布局时,特别是双层板或有高度限制的板子,要有意识地将高元件和低元件分开区域放置。

- 启用 3D DRC: AD 具有强大的 3D 设计规则检查功能。

-

封装内部元素重叠 (库设计错误):

- 含义: 在创建或编辑 PCB 封装库 (*.PcbLib) 时,构成封装的元素(如焊盘、丝印线、区域填充、3D 体)在二维或三维上重叠。例如:

- 两个焊盘放置位置重叠(极其严重错误)。

- 丝印标识线画在了焊盘上(可能导致组装或焊接问题)。

- 多个 3D 模型体定义错误导致自相交或重叠。

- 解决方法:

- 仔细检查封装设计: 在封装库编辑器中,仔细检查各层 (

Top Layer,Top Overlay丝印,Mechanical层,3D Bodies等) 上的图形元素是否放置在正确位置且没有不必要的重叠。 - 使用 DRC 检查封装: 在 PCB 库编辑器中,也可以运行 Tools -> Component Rule Check... 来检查封装内部的常见错误,包括焊盘间距、丝印与焊盘间距等(通过设置合适的规则)。

- 参考 IPC 标准和数据手册: 严格按照器件的数据手册尺寸和标准的 IPC 封装规范绘制封装,避免主观臆断导致内部重叠。

- 仔细检查封装设计: 在封装库编辑器中,仔细检查各层 (

- 含义: 在创建或编辑 PCB 封装库 (*.PcbLib) 时,构成封装的元素(如焊盘、丝印线、区域填充、3D 体)在二维或三维上重叠。例如:

-

丝印与焊盘/过孔重叠:

- 含义: 虽然不算严格意义上的“封装”重叠,但

Top Overlay/Bottom Overlay(丝印层) 上的文字、线条或图形绘制在了Top Layer/Bottom Layer(焊盘)或Multi-Layer(过孔) 上。 - 解决方法:

- 调整丝印位置: 在布局后期或最终检查时,移动丝印文本或图形,避开焊盘和过孔区域。保持丝印清晰可辨且不影响焊接是关键。

- 检查丝印规则: 在

Design -> Rules...中,Manufacturing类别下有Silkscreen Over Component Pads规则,可以用来约束丝印与焊盘的最小距离或在焊盘上是否允许存在丝印(通常设为不允许或有最小间距)。

- 含义: 虽然不算严格意义上的“封装”重叠,但

-

拼板设计中的重叠:

- 含义: 在制作拼板 (Panelization) 时,各个 PCB 小板 (Board Array) 的边框或元件放置区域发生了重叠。

- 解决方法:

- 精确设置阵列间距: 在使用

Place -> Embedded Board Array / Panelize或直接在板外放置多个板轮廓时,确保设置足够的Spacing(间距)值,使各单板之间留有工艺边(通常 2mm 以上)且元件区域无任何重叠。 - 视觉检查和 DRC: 在拼板完成后,务必放大检查板边缘和元件密集区域是否有重叠风险,并运行整体 DRC。

- 精确设置阵列间距: 在使用

总结与建议:

- 明确问题: 首先确定你指的是哪种“重叠式封装”?

- DRC 是核心工具: 无论是 2D 物理重叠还是 3D 机械碰撞,设计规则检查器 (DRC) 是 Altium Designer 中检测和预防重叠的最强大、最可靠的工具。务必配置好相关规则(尤其是

Component Clearance和Component Body 3D)并养成在关键阶段运行 DRC 的习惯。 - 利用 3D 视图: 对于空间布局和高度相关的重叠问题,切换到 3D 视图 (

3) 进行直观检查是不可或缺的步骤。 - 封装库准确性: 确保你的封装库设计正确,内部元素没有冲突重叠。

- 间距意识: 在布局时始终保持元件间距意识,考虑元件在 X, Y, Z 三个维度的空间占用。

处理 PCB 上元件或封装的重叠问题,是保证设计可制造性和可装配性的基本要求。Altium Designer 提供了完善的工具帮助你发现和解决这些问题。

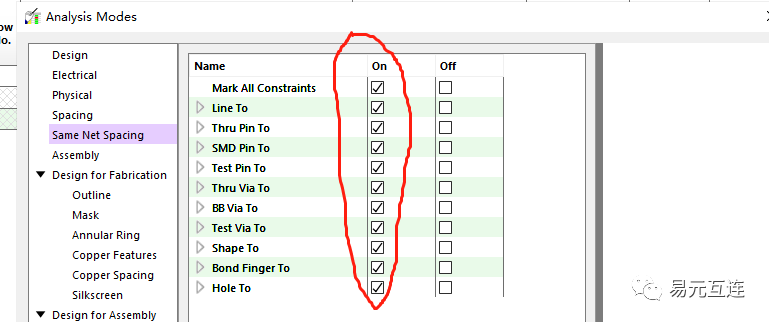

请问在Cadence中钻孔重叠如何检查呢?

使用Cadence Allegro进行PCB设计时,经常用到Subdrawing功能进行走线和孔的复用,Subdrawing的孔和线避免不了与原用的线和孔进行重叠。

2023-09-22 10:45:20

PCB设计与封装指导白皮书合集

资料简介: 本书内容为规定公司所有设计PCB板器件封装的命名与设计规范度,保证公司设计的PCB板器件使用的统一性,便于对所有设计的

资料下载

![]() elecfans小能手

2022-09-23 16:00:42

elecfans小能手

2022-09-23 16:00:42

多层PCB铺铜时模拟地和数字地在不同地层上可以上下重叠吗?

有两个问题(1):在地层铺设了模拟地,在电源层上铺设了数字电源,不在同一层上,但是上下是重叠的,可以吗?(2):多层PCB有两个地层,模拟地和数字地不在同一层上可以上下是

2023-04-10 14:45:09

allegro不同封装place_bound_top重叠不报DRC错误

如题:allegro相同封装place_bound_top重叠会报DRC错误,但是不同封装不报DRC错误,是什么原因?请教大佬们不吝赐教!

2019-09-24 16:28:43

7天热门专题

换一换

换一换

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 芯片的工作原理是什么?

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 什么是蓝牙?它的主要作用是什么?

- ssd是什么意思

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- dtmb信号覆盖城市查询

- 苹果手机哪几个支持无线充电的?

- type-c四根线接法图解

- 华为芯片为什么受制于美国?

- 怎样挑选路由器?

- 元宇宙概念股龙头一览

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- 复位电路的原理及作用

- BLDC电机技术分析

- dsp是什么意思?有什么作用?

- 苹果无线充电器怎么使用?

- iphone13promax电池容量是多少毫安

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 传感器常见类型有哪些?

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机

- 元宇宙概念龙头股一览