资料下载

SAT分析中Setup 和Hold建立时间和保持时间的详解析

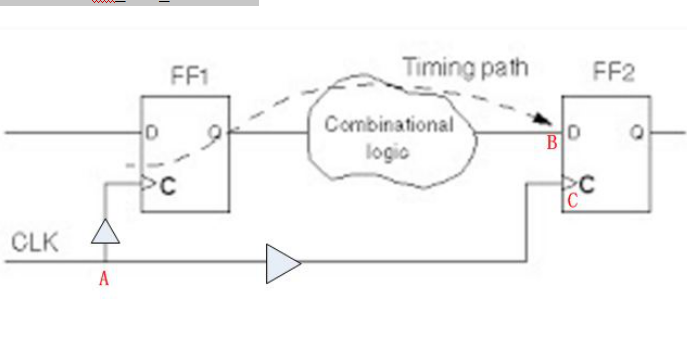

STA分析是基于同步电路设计模型的,在数据输入端,假设外部也是同时钟的寄存器的输出并且经过若干组合逻辑进入本级,而输出也被认为是驱动后一级的同时钟的寄存器。在不设置约束的情况下,纯组合逻辑的输入-》输出不得超过一个T,否则也会被认为是Timing violation.

1. Timing path

Timing path就是时间线。Timing就是从起始位置的时间点到终点位置的时间点之间的时间长度。Path是指跟位置相关,即时间起始或终点的位置。Timing path就是某位置的某一时间点到另一位置的某个时间点。对于DFF来说,上升沿类似于一瞬间的脉冲,只有在这短短的一瞬间,数据才允许通过。对于DFF来说,有两个输入点:数据D和时钟CK,有一个输出点:数据Q。由于是时间比较,所以对于D和CK一定要有一个共同的起始时间点,如下图中的A点出现clk上升沿的时刻。如下图,假设我们分析DFF2的数据和时钟到达的时间。二者共同的出发点是A的上升沿,因为A位于时钟通路上,FF1的时钟经过A点到达FF1-C点,在FF1-C上升沿打开FF1,然后数据才能从FF1-Q输出,进而传递到FF2-D。在A点, FF2的时钟沿经过clock tree,达到FF2-C点。所以数据走过的路程是:

Data path: A-》clk_tree_buf1-》FF1-C -》 FF1-Q -》 Comb_logic -》 B

而对于FF2来说只要满足下个周期的上升沿能够采样即可,所以时钟到达FF2-C的路径是:

Clk path: A -》 clk_tree_buf2-》 C.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章