资料下载

×

FPGA+MicroBlaze裸机案例开发手册

消耗积分:0 |

格式:zip |

大小:4.06 MB |

2023-11-02

导读

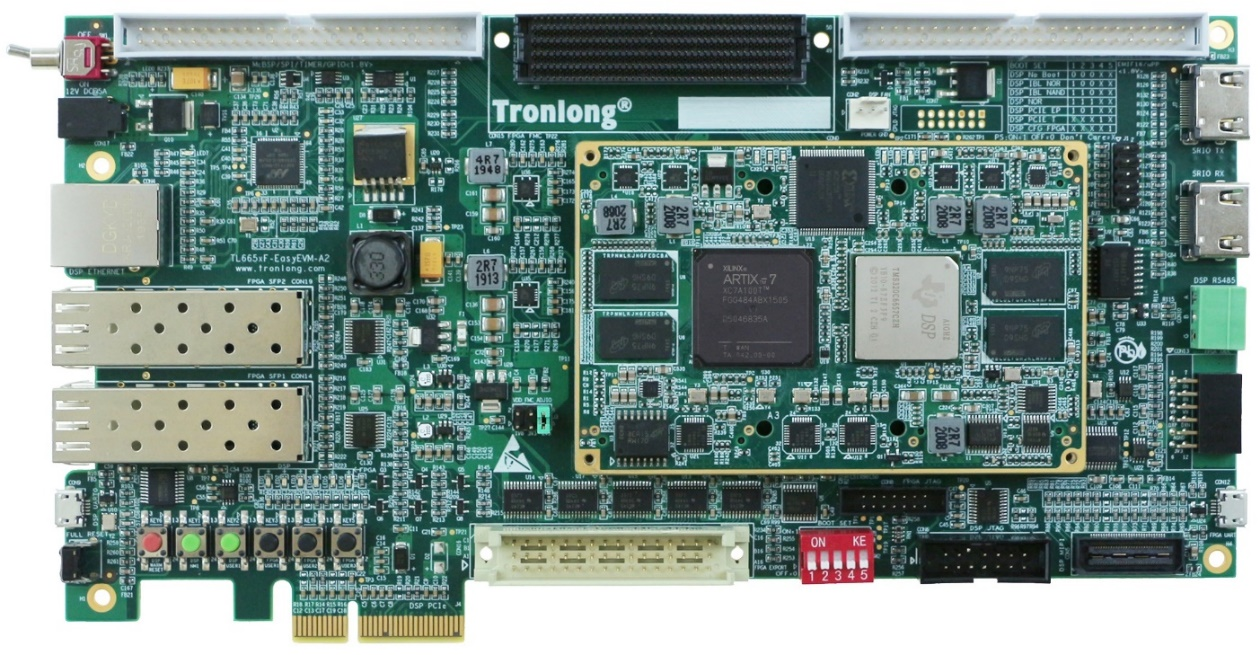

创龙科技TL665xF-EasyEVM评估板是一款基于TI KeyStone架构C6000系列TMS320C665x多核C66x定点/浮点DSP以及Xilinx Artix-7 FPGA处理器设计的高端异构多核评估板,由核心板和评估底板组成。核心板内部DSP与FPGA通过SRIO、EMIF16/uPP、I2C通信总线连接。核心板经过专业的PCB Layout和高低温测试验证,稳定可靠,可满足各种工业应用环境。

评估板接口资源丰富,引出千兆网口、PCIe、SRIO、EMIF16/uPP、双路SFP光口等高速通信接口,方便用户快速进行产品方案评估与技术预研。

目 录

前 言———— 4

1 mig_dma案例———— 6

1.1 案例功能———— 6

1.2 操作说明———— 6

1.3 关键代码(MicroBlaze)———— 7

1.4 Vivado工程说明———— 16

1.5 IP核配置———— 18

1.5.1 MicroBlaze IP核———— 18

1.5.2 AXI DMA IP核———— 21

1.5.3 MIG 7 Series IP核———— 22

1.5.4 AXI BRAM Controller IP核———— 30

1.5.5 Block Memory Generator IP核———— 33

1.5.6 AXI Timer IP核———— 34

1.5.7 AXI GPIO IP核———— 35

2 aurora_dma案例———— 37

2.1 案例功能———— 37

2.2 操作说明 ————38

2.3 关键代码(MicroBlaze) ————39

2.4 Vivado工程说明———— 43

2.5 模块/IP核配置———— 45

2.5.1 MicroBlaze IP核———— 45

2.5.2 AXI DMA IP核———— 45

2.5.3 AXI BRAM Controller IP核———— 47

2.5.4 Block Memory Generator IP核———— 49

2.5.5 AXI Timer IP核 ————50

2.5.6 Aurora 8B10B IP核 ————51

2.5.7 aurora_reset模块 ————54

2.5.8 cdcm61002_cfg模块 ————56

3 udp_echo案例 ————59

3.1 案例功能 ————59

3.2 操作说明———— 59

3.3 关键代码(MicroBlaze)———— 63

3.4 Vivado工程说明———— 65

3.5 模块/IP核配置———— 67

3.5.1 MicroBlaze IP核———— 67

3.5.2 AXI Ethernet IP核———— 67

3.5.3 udp_ip_stack模块———— 69

3.5.4 udp_echo_server模块———— 72

3.5.5 cdcm61002_cfg模块———— 76

4 udp_dma案例———— 78

4.1 案例功能———— 78

4.2 操作说明 ————79

4.3 关键代码(MicroBlaze) ————80

4.4 Vivado工程说明 ————85

4.5 模块/IP核配置 ————88

4.5.1 MicroBlaze IP核———— 88

4.5.2 AXI Ethernet IP核———— 88

4.5.3 udp_ip_stack模块 ————89

4.5.4 cdcm61002_cfg模块 ————94

4.5.5 AXI Timer IP核———— 97

4.5.6 AXI DMA IP核———— 98

更多帮助———— 100

前 言

本文主要介绍基于FPGA + MicroBlaze裸机案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx SDK 2017.4。FPGA + MicroBlaze裸机综合案例分为FPGA程序与MicroBlaze裸机程序两部分。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章