资料下载

四通道图像传感器模拟前端

输入钳位

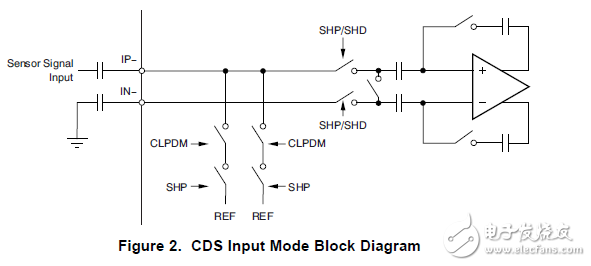

在电荷耦合器件(CCD)输入模式的vsp7500 / vsp7502 InP引脚连接到缓冲CCD输出通过电容耦合,因此,输入钳是必要的。的目的输入钳位是恢复在交流耦合过程中丢失的输入信号的直流分量,并建立CDS的期望直流偏置点。图2还说明了输入钳位。输入电平被夹紧到内部虚拟像素间隔期间的参考电压。更具体地说,夹紧功能变得活跃时两个CLPDM和小水电活跃。

16位ADC

vsp7500 / vsp7502还提供了一个高速、16位ADC。该ADC采用全差分流水线具有校正功能的体系结构。这种架构实现更好的线性度较低的信号电平,因为大的线性误差往往发生在满量程范围内的特定点,和线性改善的信号水平低于特定点。ADC确保整个满量程范围的16位分辨率。

光学黑(OB)环和OB夹(obclp)水平

vsp7500 / vsp7502有一个内置的光学黑(OB)偏移的自校准电路(OB循环),通过使用CCD图像传感器输出的OB像素补偿OB电平。该装置还提供数字OB钳环。CCD偏移补偿通过会聚两个OB循环,同时激活一个时期的OB像素从CCD的输出在CLPOB。20像素CLPOB期可能不够用于稳定的OB循环操作。

时钟和DLL

vsp7500 / vsp7502要求下面的时钟MCLK的正确操作:系统时钟CLPOB,的;光学黑电平钳位和CLPDM,输入钳。hblk定时信号传输水平消隐时间。在这一时期,高速HTG脉冲被屏蔽。的pblk定时信号输出消隐期间定时发送数据。在此期间,输出ADC数据被屏蔽。vsp7500 / vsp7502有内置的DLL电路,使所需的采样时钟和水平用于输出LVDS数据的定时脉冲和逻辑时钟。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章