资料下载

×

高性能DSP为何助于实现数字世界与真实(模拟)世界的通信

消耗积分:1 |

格式:rar |

大小:0.2 MB |

2017-09-13

高性能DSP为何助于实现数字世界与真实(模拟)世界的通信

由于DSP能够迅速测量、过滤或压缩实时模拟信号,因此DSP在电子系统设计中非常重要。这样,DSP有助于实现数字世界与真实(模拟)世界的通信。但是随着电子系统变得越来越精细,需要处理多个模拟信号源,工程师们不得不作出艰难的决策。是使用多个DSP并使其功能与系统的其余部分同步,还是使用一个能够实现多个功能的带精细软件的高性能DSP更具优势?

由于现在的系统很复杂,在许多情况下,单DSP的实现方案的往往没有足够的处理能力。同时,系统架构也不能满足多芯片系统的成本、复杂性和功耗要求。

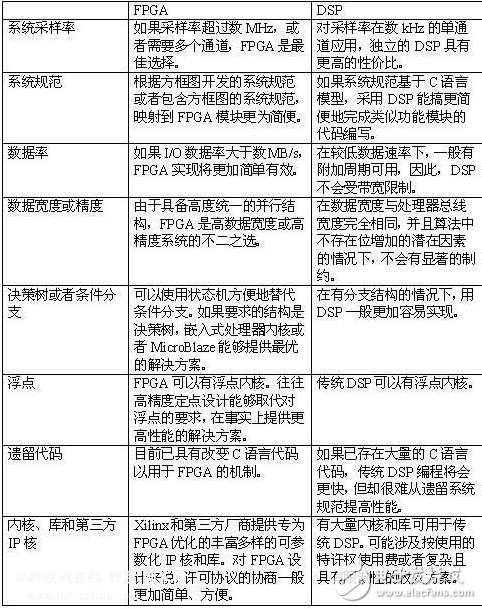

FPGA现已成为需要高性能DSP功能的系统的绝佳选择。事实上,与独立的数字信号处理器相比,FPGA技术一般可以为DSP难题提供更加简单的解决方案。要了解其中的原因,需要回顾一下DSP的起源和发展过程。

专用微处理器

在过去的二十多年里,传统的DSP架构一直在竭力跟上日益增长的性能要求的步伐。随着视频系统大踏步地迈进高清和3D时代,并且通信系统为实现更高带宽已经将现有技术发挥到极致,设计师们需要可替代的实现策略。用于实现数字信号处理算法的硬件不外乎以下三种基本器件之一:微处理器、逻辑电路和存储器。有些设计可能还需要额外硬件来实现模数转换(A/D)、数模转换(D/A)以及高速数字接口。

传统的数字信号处理器是设计用于实现专门目的的微处理器。这类处理器非常适合用于处理算法密集型任务,但是性能却受到时钟速率及其内部设计顺序性的限制。这限制了它们对输入数据采样每秒最多执行的运算次数。一般来讲,每执行一次算术逻辑单元(ALU)运算需要三或四个时钟周期。多核架构可以提高性能,但是提升幅度有限。因此,采用传统信号处理器的设计必须重复利用架构单元来实现算法。对于每次执行的加、减、乘或其他任何基本运算,不论是内部还是外部反馈,每次执行都必须循环通过ALU。

遗憾的是,在处理当今众多的高性能应用时,典型的DSP难以满足系统要求。过去已经提出过多种解决方案,包括在一个器件中使用多个ALU或者在一块板上使用多个DSP器件;不过这类方案往往会大大增加成本,并且只会将问题转移到另外一个领域。比如,用多个器件提高性能遵循指数曲线。要使性能提高一倍,需要用两个器件,若要再提高一倍,则需要用四个器件,依此类推。此外,程序员关注的重点往往会从信号处理功能转移到多个处理器和内核之间的任务调度上。这会产生大量的附加代码,而且这些代码会成为系统开销,而不是用于解决眼前的数字信号处理问题。

FPGA 技术的引进为解决DSP方案与日俱增的复杂性带来了福音。FPGA最初开发的目的是为了整合和集中分立的存储器和逻辑电路,以实现更高的集成度、更出色的性能和更高的灵活性。FPGA技术现已成为目前使用的几乎所有高性能系统的一个重要组成部分。相比传统DSP,FPGA是由可配置逻辑阵列(CLB)、存储器、DSP逻辑片(Slice)和一些其他元件组成的统一阵列构成的巨大并行结构。它们可以使用VHDL和Verilog等高级描述语言进行编程,或者在框图中使用系统生成器进行编程。FPGA还提供许多专用功能和IP核,用来以高度优化的方式直接完成实现方案。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章