资料下载

LAN91C111 10/100非pci以太网单芯片mac层

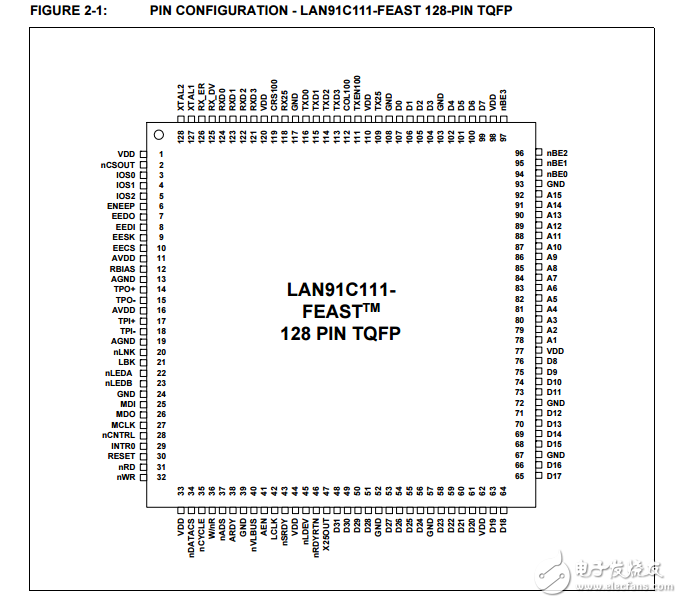

The Microchip LAN91C111 is designed to facilitate the implementation of a third generation of Fast Ethernet connectivity solutions for embedded applications. For this third generation of products, flexibility and integration dominate the design requirements. The LAN91C111 is a mixed signal Analog/Digital device that implements the MAC and PHY portion of the CSMA/CD protocol at 10 and 100 Mbps. The design will also minimize data throughput constraints utilizing a 32-bit, 16- bit or 8-bit bus Host interface in embedded applications. The total internal memory FIFO buffer size is 8 Kbytes, which is the total chip storage for transmit and receive operations. The Microchip LAN91C111 is software compatible with the LAN9000 family of products. Memory management is handled using a patented optimized MMU (Memory Management Unit) architecture and a 32- bit wide internal data path. This I/O mapped architecture can sustain back-to-back frame transmission and reception for superior data throughput and optimal performance. It also dynamically allocates buffer memory in an efficient buffer utilization scheme, reducing software tasks and relieving the host CPU from performing these housekeeping functions. The Microchip LAN91C111 provides a flexible slave interface for easy connectivity with industry-standard buses. The Bus Interface Unit (BIU) can handle synchronous as well as asynchronous transfers, with different signals being used for each one. Asynchronous bus support for ISA is supported even though ISA cannot sustain 100 Mbps traffic. Fast Ethernet data rates are attainable for ISA-based nodes on the basis of the aggregate traffic benefits. Two different interfaces are supported on the network side. The first Interface is a standard Magnetics transmit/receive pair interfacing to 10/100Base-T utilizing the internal physical layer block. The second interface follows the MII (Media Independent Interface) specification standard, consisting of 4 bit wide data transfers at the nibble rate. This interface is applicable to 10 Mbps standard Ethernet or 100 Mbps Ethernet networks. Three of the LAN91C111’s pins are used to interface to the two-line MII serial management protocol.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章