资料下载

×

如何使用寄存器级读&写控制基于PXI平台的FPGA

消耗积分:0 |

格式:rar |

大小:0.99 MB |

2017-10-16

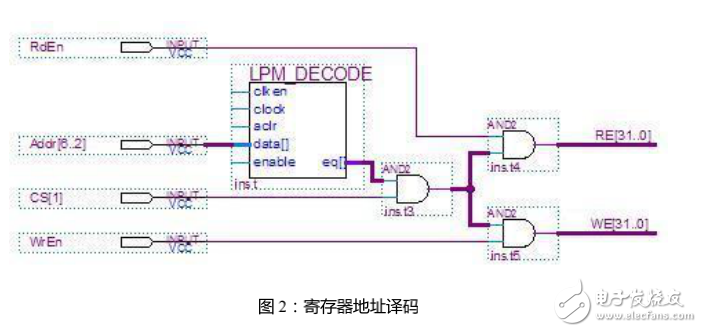

本设计实例中有四组完全相同的 I/O 引脚(见图 4),每组有 32 路通道。每路通道都支持双向传输,并可以独立配置传输方向。输出寄存器为双缓冲结构,支持四组 I/O 引脚(128 路通道)同步更新。第一阶段,通过 WE_Data 控制信号,将输出数据使用写入第一级数据寄存器,通过 WE_Tristate 写入三态控制信号。以上这些信号来自于 WE[31..0]信号,并且这些信号在每组 I/O 引脚间独立。第二阶段,通过 WE_UpdatePort 控制信号,将第一级输出的数据和三态控制信号写入第二级寄存器。以上这些信号也来自于 WE[31..0]信号,但是四组 I/O 引脚共用以实现四组 I/O 引脚数据的同步更新。使用 RE_Tristatelatch,RE_DataLatch,RE_TristatePort

和REDataPort控制信号访问输出寄存器两个阶段的数据和三态控制寄存器从而进行读

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章