资料下载

×

基于异步FIFO在FPGA与DSP通信中的运用

消耗积分:0 |

格式:rar |

大小:0.78 MB |

2017-10-19

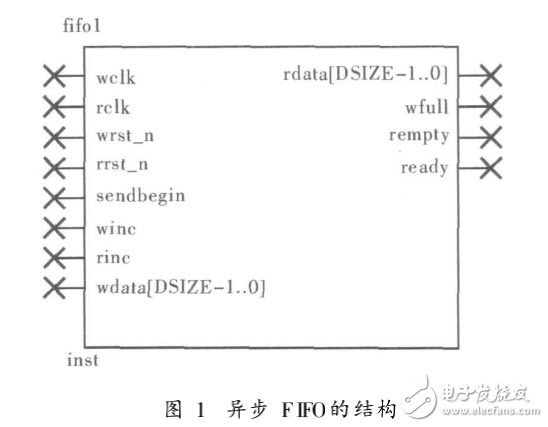

在目前电子系统的设计中, DSP+ FPGA 架构越来越多, 其原因在于该架构兼顾了速度和灵活性。通用 DSP的优点是通过编程可以广泛应用到产品中,并且主流制造商生产的 DSP 已能满足算法控制结构复杂、运算速度高、寻址方式灵活和通信性能强大等需求。但是传统的 DSP 采用冯 - 诺依曼结构或某种类型扩展。此种结构本质上是串行的, 因此遇到需处理的数据量大, 对处理速度要求高, 但是对运算结构相对比较简单的底层信号处理算法则显不出优点, 适合采用 FPGA 硬件实现。而采用 DSP+ FPGA 的数字硬件系统就可以把二者优点结合起来, 兼顾速度和灵活性, 既满足底层信号处理要求, 又满足高层信号处理要求。采用此架构, 就不可避免地遇到 FPGA 与DSP之间数据通信的问题。本文讨论了异步 FIFO 在FPGA 与 DSP 通信中的运用, 该方法具有传输速度快 稳定可靠并且实现方便等

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章