资料下载

155.52兆赫频率合成器ad809数据表

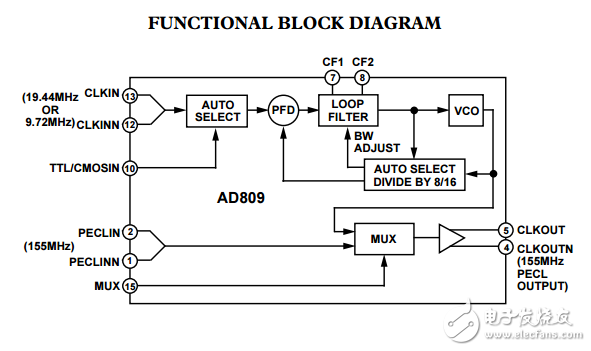

The AD809 provides a 155.52 MHz ECL/PECL output clock from either a 19.44 MHz or a 9.72 MHz TTL/CMOS/ECL/PECL reference frequency. The AD809 functionality supports a distributed timing architecture, allowing a backplane or PCB 19.44 MHz or 9.72 MHz timing reference signal to be distributed to multiple155.52 Mbps ports. The AD809 can be applied to create the transmit bit clock for one or more ports. An input signal multiplexer supports loop-timed applications where a 155.52 MHz transmit bit clock is recovered from the 155.52 Mbps received data. The low jitter VCO, low power and wide operating temperature range make the device suitable for generating a 155.52 MHz bit clock for SONET/SDH/Fiber in the Loop systems. The device has a low cost, on-chip VCO that locks to either 8× or 16× the frequency at the 19.44 MHz or 9.72 MHz input. No external components are needed for frequency synthesis; however, the user can adjust loop dynamics through selection of a damping factor capacitor whose value determines loop damping. The AD809 design guarantees that the clock output frequency will drift low (by roughly 20%) in the absence of a signal at the input. The AD809 consumes 90 mW and operates from a single power supply at either +5 V or –5.2 V.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章