资料下载

×

DSP HPI口与PC104总线接口的FPGA设计方案

消耗积分:1 |

格式:rar |

大小:0.2 MB |

2017-11-06

摘 要 通过对TI公司TMS320C5000系列DSP HPI总线和PC104总线时序的分析,以VHDL语言为工具,使用Altera的FPGA芯片EP1K50,设计完成PCI04总线和DSP HPI总线之间的通信接口,并在一款以TMS320VC5409DSP为数据采集处理器、研华嵌入式工控主板PCM-5825为系统主板组成的嵌入式数据采集系统申得到了运用;给出与整个接口设计相关的VHDL源代码和在PCM-5825上验证接口设计的X86汇编语言程序。

关键词 DSP HPI PC104总线 FPGA VHDL源代码

在一款嵌入式数据采集系统的设计中,采用TMS320VC5409 DSP作为对多路信号的采集与预处理,处理后的数据送至12.7 Cm(5in)的工控计算机中进行分析与保存。因为工控机的总线为PC104,因此需要设计PC104与DSP之间的通信接口。系统中以Altera公司的一片FPGA芯片EPlK50来对该接口和数据采集过程中的逻辑控制与FIFO进行设计。下面主要阐述该通信接口的设计。

1 DSP的HP0接口

TMS320VC5409 DSP的HPI是一个8位的并行接口,主要用来与主设备或主处理器接口。DSP内部有一定数量的双访问RAM,除了DSP本身可以访问该RAM区域外,主机也可以通过HPI口实现对双访问RAM的访问,从而实现主机与DSP的通信。

HPI接口通过HPI控制寄存器HPIC、地址寄存器HPIA、数据寄存器HPID等3个HPI寄存器进行控制和实现数据传输。这3个寄存器都是16位的,因此主机访问这些寄存器时需要分两次操作才能完成。

HPIC只有4位用于控制HPI的操作,这4位分别位于高字节和低字节的低4位,并规定HPIC的高低字节必须相同:

Bit0/8(BOB)一一用于字节顺序控制,BOB=1表示第1个字节为低字节,否则第1个字节为高字节;

Bitl/9(SMOD)一一访问模式控制,SMOD=l表示共享访问模式(SAM),否则为主机访问模式(HOM);

Bit2/10(DSPINT)一一主机通过将该位写l来向DSP发送1次HPI中断;

Bit3/11(H1NT)一一DSP通过向该位置l,使外部引脚HINT产生一个低电子作为给主机的中断,中断的清除必须由主机向该位写l来清除。

HPID是数据寄存器,主机通过读写该寄存器来实现对共享RAM的读写,RAM的地址则由HPIA地址寄存器的内容来决定。因此,主机对DSP的访问过程是,先往HPI地址寄存器HPIA写入欲访问的地址,然后再对数据寄存器HPID进行读或写访问。

HPI接口信号包括:

HAS一一输入,地址锁存信号,可连接到高电平;

HBIL一一输入,字节识别信号,用来识别传输的是高电平还是低电平;

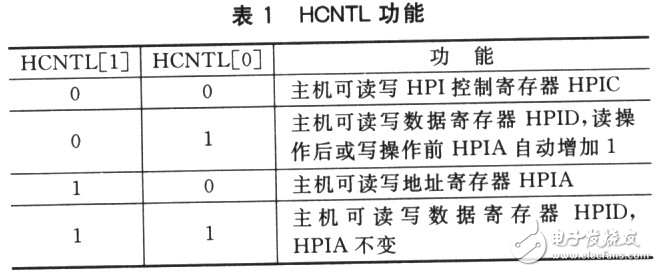

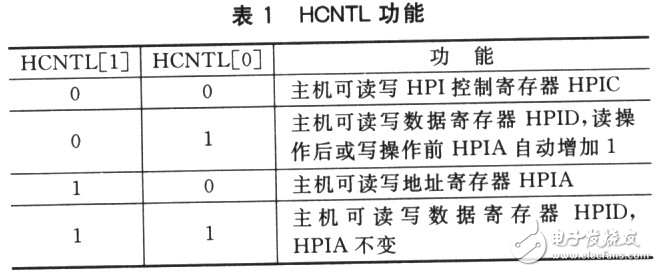

HCNTL[1..0]一一输入,HPI寄存器的访问地址信号,主机用来选择访问的HPI寄存器。如表l所列;

HCS一一输入,HPI片选信号,低电平有效;

HD[7..0]一一双向三态数据总线;

HDS1/HDS2一一数据输入选通信号,可将其中一个接低电平,另一个接逻辑控制;

HINT一一输出,给主机的中断信号,由HPIC寄存器的HINT位控制;

HRDY一一输出,HPI准备好,高电子有效;

HR/W一一输入,读写控制信号,高电子表示主机进行读操作,低电子表示主机进行写操作。

HPI的访问时序如图l所示。如前所述,访问寄存器时需要分两次操作才能完成。

关键词 DSP HPI PC104总线 FPGA VHDL源代码

在一款嵌入式数据采集系统的设计中,采用TMS320VC5409 DSP作为对多路信号的采集与预处理,处理后的数据送至12.7 Cm(5in)的工控计算机中进行分析与保存。因为工控机的总线为PC104,因此需要设计PC104与DSP之间的通信接口。系统中以Altera公司的一片FPGA芯片EPlK50来对该接口和数据采集过程中的逻辑控制与FIFO进行设计。下面主要阐述该通信接口的设计。

1 DSP的HP0接口

TMS320VC5409 DSP的HPI是一个8位的并行接口,主要用来与主设备或主处理器接口。DSP内部有一定数量的双访问RAM,除了DSP本身可以访问该RAM区域外,主机也可以通过HPI口实现对双访问RAM的访问,从而实现主机与DSP的通信。

HPI接口通过HPI控制寄存器HPIC、地址寄存器HPIA、数据寄存器HPID等3个HPI寄存器进行控制和实现数据传输。这3个寄存器都是16位的,因此主机访问这些寄存器时需要分两次操作才能完成。

HPIC只有4位用于控制HPI的操作,这4位分别位于高字节和低字节的低4位,并规定HPIC的高低字节必须相同:

Bit0/8(BOB)一一用于字节顺序控制,BOB=1表示第1个字节为低字节,否则第1个字节为高字节;

Bitl/9(SMOD)一一访问模式控制,SMOD=l表示共享访问模式(SAM),否则为主机访问模式(HOM);

Bit2/10(DSPINT)一一主机通过将该位写l来向DSP发送1次HPI中断;

Bit3/11(H1NT)一一DSP通过向该位置l,使外部引脚HINT产生一个低电子作为给主机的中断,中断的清除必须由主机向该位写l来清除。

HPID是数据寄存器,主机通过读写该寄存器来实现对共享RAM的读写,RAM的地址则由HPIA地址寄存器的内容来决定。因此,主机对DSP的访问过程是,先往HPI地址寄存器HPIA写入欲访问的地址,然后再对数据寄存器HPID进行读或写访问。

HPI接口信号包括:

HAS一一输入,地址锁存信号,可连接到高电平;

HBIL一一输入,字节识别信号,用来识别传输的是高电平还是低电平;

HCNTL[1..0]一一输入,HPI寄存器的访问地址信号,主机用来选择访问的HPI寄存器。如表l所列;

HCS一一输入,HPI片选信号,低电平有效;

HD[7..0]一一双向三态数据总线;

HDS1/HDS2一一数据输入选通信号,可将其中一个接低电平,另一个接逻辑控制;

HINT一一输出,给主机的中断信号,由HPIC寄存器的HINT位控制;

HRDY一一输出,HPI准备好,高电子有效;

HR/W一一输入,读写控制信号,高电子表示主机进行读操作,低电子表示主机进行写操作。

HPI的访问时序如图l所示。如前所述,访问寄存器时需要分两次操作才能完成。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章