资料下载

如何在C8051F020芯片进行高速ADC采样时进行代码优化的详细方法说明

在应用C8051F020的片内高速ADC进行时间序列采样时,编写代码使ADC工作于最高速度是一个难题。本文从ADC的C语言中断模式的驱动代码设计开始,分析对应的汇编语言中消耗CPU的主要步骤,研究ADC采样的优化方式。经过验证,通过使用额外定时器可以优化ADC采样结束时机的控制;而在时间关键场所,因为减少了现场保护和恢复的操作代码,查询方式比中断模式具有更高的时间效率。

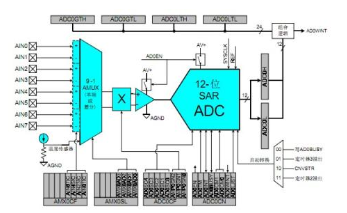

在设计需要进行时间序列采样的数据采集仪表中,需要用ADC对电压信号进行等间隔高速采样并缓存,带有高速ADC的C80S1F020单片机是一种很好的选择。C8051F020是一款由Silicon Laboratories公司生产的高性能8位混合信号兼容MCS-51单片机,内部集成4096字节的XRAM,以及2个带有PGA的高速ADC,其中8位模数转奂器ADC1采样率高达500kSPS(Sample per second)。在进行时间序列分析的应用中需要编程ADC1进行数据采集并将数据缓存到XRAM中。C8051 F020的机器周期和时钟周期相等(传统单片机的机器周期等于其时钟周期的12倍) ,当使用24MHz的晶振时,速度最高可达到24MIPS(Million Instructions Per Second),传统单片机仅2MIPS。虽然这个速度看起来已经很快,但是如果需要使得ADC1工作于最高频率,代码的编写则需要相当的技巧。针对时间关键部1分的编程,除了需要考虑常规的代码优化方案,如循环展开、宏替换函数等之外,本文将从基本的采样设计程序结构设计人手,研究如何在Keil集成开发环境下编写合适的C语言代码驱动F020的ADC1,使其工作于最高采样率。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章