资料下载

×

使用Hyperlynx实现板级信号完整性的仿真教程资料免费下载

消耗积分:10 |

格式:pdf |

大小:6.08 MB |

2019-11-01

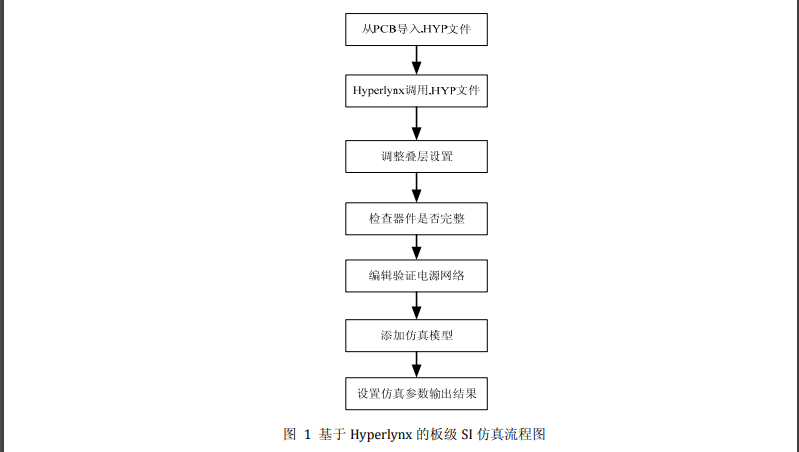

随着 IC 芯片时钟信号频率的增加、信号边沿的减小,由此带来的信号完整性问题已经越来越凸显。PCB 信号完整性问题主要包括由阻抗不匹配引起的信号过冲、相邻不同网络之间由于各种耦合产生的信号串扰、有损传输线造成的信号边沿退化等问题。信号完整性问题不仅会造成电路功能错误,也会造成各种电磁兼容问题。在高速 PCB 设计过程中,为了能够使 PCB 一次设计成功的同时又能确保板级辐射发射不超标,板级信号完整性仿真分析已经成为一种重要不可缺少的手段。信号完整性仿真的模型主要有 IBIS 模型、SPICE 模型、VHDL_AMS 模型、 Verilog_AMS 等等。其中 IBIS 模型是 PCB 设计业界中最常用的、最流行的信号完整性仿真模型。板级信号完整性仿真工具有 Mentor Graphics 的 Hyperlynx、 Cadence 公司的 SPECCTRAQuest 等等。下面以 Hyperlynx 为例说明板级信号完整性仿真的方法及具体过程。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章