资料下载

时钟恢复电路的设计资料详细说明

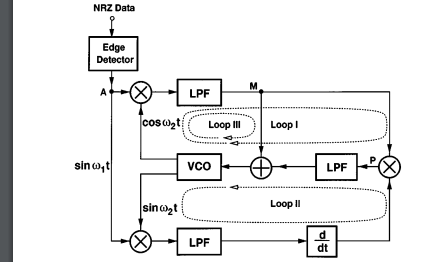

介绍了一种基于四相关器结构的2.5gb/s 15 mW时钟恢复电路的设计。该电路采用鉴相和鉴频相结合的方法,将微分、全波整流、混频等高速运算结合在一起,降低了功耗。此外,采用两级压控振荡器,该振荡器包含两个相移元件,以提供宽调谐范围和隔离技术,以抑制由于输入数据转换而产生的馈通。该电路采用20ghz 1-ãm BiCMOS技术制作,其均方根抖动为9.5ps,捕获范围为300mhz。

速低功耗时钟恢复电路在高性能通信系统中有着广泛的应用,本文介绍了一种采用20ghz 1-m BiCMOS技术制作的2.5gb/s 15 mW时钟恢复电路(CRC)的设计。该电路采用改进的“四相关器”结构、利用相位和频率检测从非归零(NRZ)数据序列中提取时钟。除了低功耗外,一个重要的问题是获得相对较宽的捕获范围,以便在温度和过程变化时电路能够锁定输入。时钟恢复电路被设计用于以2.5 Gb/s(SONET OC-48标准)运行的光纤接收器的前端。虽然目前以该速率实现的主要是III-V技术,但在主流VLSI工艺中执行该功能是有利的,以便允许更高级别的整合。图1所示为典型的光纤前端的框图,其中NRZ数据以光的形式被接收并由光电探测器转换为电流。然后电流被放大并通过跨阻放大器转换成电压,因为进一步的数字处理需要数据的定时信息,时钟恢复电路提取时钟,判决电路对数据进行重定时。因此,可以同步执行以下数据处理。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章