资料下载

FPGA的指导性原则详细资料说明

这一部分主要介绍 FPGA/CPLD设计的指导性原则,如FPGA设计的基本原则、基本设计思想、基本操作技巧、常用模块等。 FPGA/CPLD设计的基木原则、思想、技巧和常用模块是一个非常大的问题,在此不可能面面俱到,只能我们公司项目中常用的一些设计原则与方法提纲携领地加以介绍,希望引起同事们的注意,如果大家能有意识的用这些原则方法指导日后的工作,不断积累和充实自己,将取得事半功倍的效果!

本章主要内容如下

基本原则之一:面积和速度的平衡与互换;

基本原则之二:硬件原则;

基本原则之三:系统原则;

基本原则之四:同步设计原则;

基本设计思想与技巧之一:乒乓操作

基本设计思想与技巧之二串并转换

基本设计思想与技巧之三:流水线操作;

基本设计思想与技巧之四:数据接口的同步方法

常用模块之一:RAM;

常用模块之二:全局时钟资源与时钟锁相环

常用模块之三:全局复位/置位信号

常用模块之四:高速串行收发器

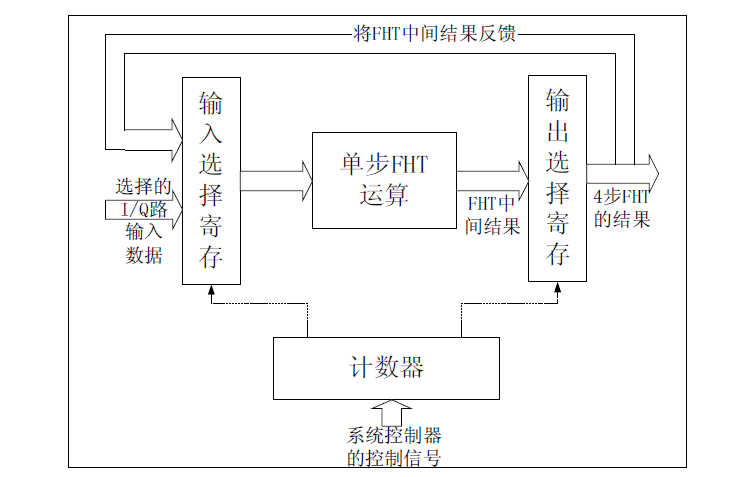

这里“面积”指一个设计消耗 FPGA/CPLD的逻辑资源的数量,对于FPGA可以用所消耗的触发器(FF)和查找表(LUT)来衡量,更一般的衡量方式可以用设计所占用的等价逻辑门数。“速度”指设计在芯片上稳定运行,所能够达到的最高频率,这个频率由设计的时序状况决定,和设计满足的时钟周期, pad to pad Time, Clock Setup Time, Clock holdime, Clock-to- Output Delay等众多时序特征量密切相关。面积(area)和速度(sped)这两个指标贯穿着 FPGA/CPLD设计的始终,是设计质量的评价的终极标准。这里我们就讨论下关于面积和速度的两个最基本的概念:面积与速度的平衡和面积与速度的互换面积和速度是一对对立统一的矛盾体。要求一个同时具备设计面积最小,运行频率最高是不现实的。更科学的设计目标应该是在满足设计时序要求(包含对设计频率的要求)的前提下,占用最小的芯片面积。或者在所规定的面积下,使设计的时序余量更大,频率跑得更高。这两种目标充分体现了面积和速度的平衡的思想。关于面积和速度的要求,我们不应该简单的理解为工程师水平的提高和设计完美性的追求,而应该认识到它们是和我们产品的质量和成本直接相关的。如果设计的时序余量比较大,跑的频率比较高,意味着设计的健壮性更强,整个系统的质量更有保证;另一方面,设计所消耗的面积更小,则意味着在单位芯片上实现的功能模块更多,需要的芯片数量更少,整个系统的成本也随之大幅度削减。作为矛盾的两个组成部分,面积和速度的地位是不一样的。相比之下,满足时序、工作频率的要求更重要一些,当两者冲突时,采用速度优先的准则。面积和速度的互换是 FPGA/CPLD设计的一个重要思想。从理论上讲,一个设计如果时序余量较大,所能跑的频率远远高于设计要求,那么就能通过功能模块复用减少整个设计消耗的芯片面积,这就是用速度的优势换面积的节约:反之,如果一个设计的时序要求很高,普通方法达不到设计频率,那么一般可以通过将薮据流串并转换,并行复制多个操作模块对整个设计采取“乒乓操作”和“串并转换”的思想进行运作,在芯片输岀模块再在对数据进行“并串转换”,是从宏观上看整个芯片满足了处理速度的要求,这相当于用面积复制换速度提高。面积和速度的互换的具体操作有很多的技巧,比如模块复用,“乒乓操作”,“串并转换”等,需要大家在日后工作中积累掌握。下面举例说明如何使用“速度换面积”和“面积换速度”。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章