资料下载

Zynq的启动与配置过程详解

作者:watchman,文章来源:ZYNQ微信公众号

Zynq的JTAG配置过程

初学 Zynq 的时候,都是按照惯例打开 Vivado 软件,然后实现 Zynq 可编程逻辑硬件部分PL的设置后,把硬件部署导出,再打开 SDK 进行 ARM 核的软件部分 PS 编程设计,最后再将硬件比特流文件(.bit)和软件的可执行链接文件(.elf)下载到 Zynq 开发板中,这样就可以对自己的软硬件设计进行调试和验证。

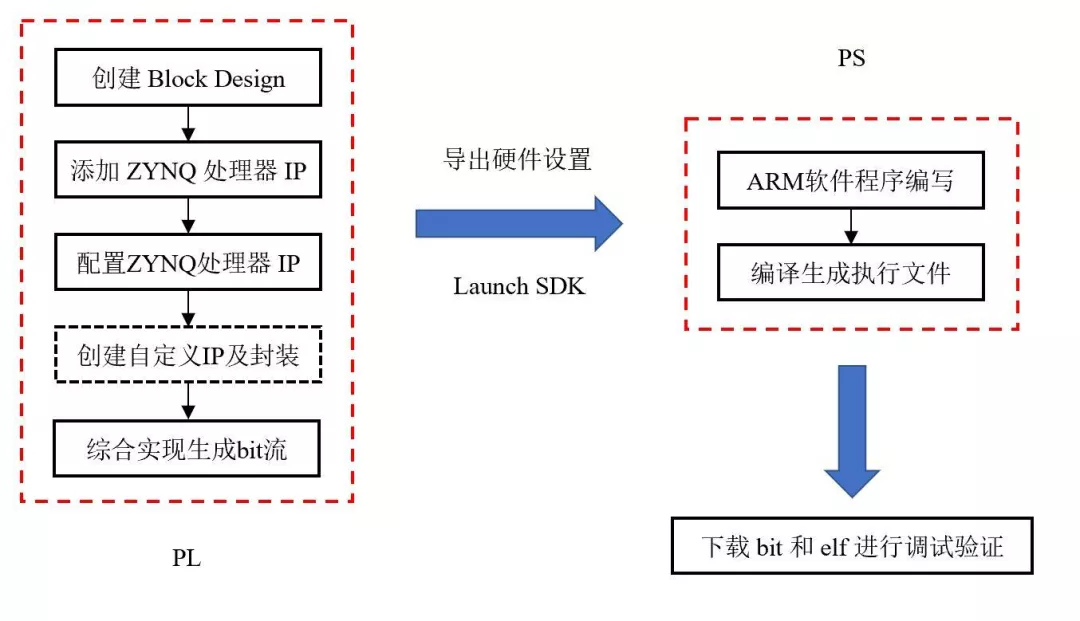

这种设计方式可以用下面的图很好的描述:

如上图所示,这其实是刚接触 Zynq 软硬件设计时需要了解的最基本开发流程,也是PL和PS设计结合的完美体现。

但是,上述开发的过程都有一个基本的前提,就是 Zynq 开发板是通过 JTAG 直接与电脑相连,然后实现程序的下载。

从另一个角度来说,PL和PS的配置都可以认为是电脑主机通过 JTAG 完成的。

但是,在实际中,Zynq 开发板不可能实时与电脑连接,当 JTAG 不起作用时,Zynq 芯片是怎样实现对自己的配置?

这也是本文将要和大家共同讨论的问题。

Zynq的启动流程

在无 JTAG 的模式下,Zynq 是通过片上CPU完成对芯片的配置,也就是PS和PL的配置是通过 PS 处理器 ARM 核来实现的。

需要注意的是,与传统的 Xilinx 7 系列 FPGA 芯片不同,Zynq 是不支持从 PL 端进行直接启动配置的,一定要通过 PS 部分来完成。

Zynq 的具体启动配置是分级进行的,一共可以分为3个阶段,可以用0~2来表示:

1. Stage 0:BootROM 阶段

2. Stage 1:FSBL (First Stage Boot loader)阶段

3. Stage 2:SSBL (Second Stage Boot loader)阶段

熟悉 ARM 开发的小伙伴应该对上面的启动过程感到很熟悉,但又有陌生的地方。不用急,下面对这三个阶段进行详细的分析。

Zynq启动阶段0——BootROM

阶段0,又称为 BootROM 阶段。ROM 相信大家都知道,Read-Only Memory,只读存储器的意思;而 Boot 是引导的含义,所以 BootROM 从字面的意思来看,就是只能去读取的引导存储器。

实际上,BootROM 的作用和它的字面意思完全一样,就是指 ARM 核在上电之后,需要第一时间去读取 BootROM 中固化的程序,完成对芯片的最初始化的配置。

因为是只读的,所以根据 ROM 的性质,BootROM 中的程序是无法修改的。有的朋友会问BootROM 这一部分代码主要完成了对 Zynq 的哪些配置?

在具体说明 BootROM 进行哪些配置之前,先要描述一下关于 Zynq 的启动引脚配置。

Zynq 拥有5个可以进行配置的 MIO 引脚,是 MIO[6:2],在硬件形式上就表现为5个跳线帽,可以分别接 GND 或 3V3 的高电平。它们的作用如下:

通过不同的引脚作用说明可以发现,当 JTAG 不起作用时,就需要通过改变 MIO[5:3] 的连接来实现从 SD 卡等不同的存储介质启动。

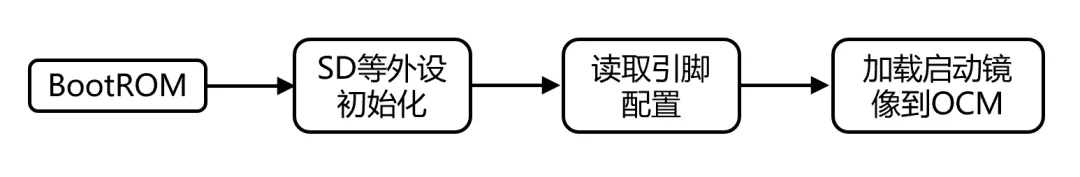

而 BootROM 最重要的作用就是通过读取 MIO[6:2] 的引脚配置情况,决定从何种介质中加载阶段1需要使用的启动镜像。当然在加载之前,BootROM 会先完成对 SD 卡,NAND,NOR,QSPI Flash 等的初始化,从而使得ARM 核能够成功访问并使用这些外设。

BootROM 在完成以上任务的同时,也会对安全模式等运行模式进行配置,这部分博主暂时不太了解,所以不做过多叙述。

BootROM 在从外部存储设备读取了启动镜像后,通常会把进行加载到 OCM 中。OCM,On Chip Memory,是Zynq 中 ARM 内核的片上存储器,也叫片上内存。

自此之后,BootROM 阶段的启动任务就算是圆满结束了,接下来 BootROM 阶段就把控制权转移到了阶段1手中。

注:BootROM 阶段不对 PL 进行配置

Zynq启动阶段1——FSBL

FSBL,(First Stage Boot Loader),就是 BootROM 加载到 OCM 中的启动镜像。FSBL 完成的任务是 Zynq 启动过程中的关键一环,可以分为以下4项:

1. 完成 PS 的初始化

2. 加载 PL 的bit流文件,完成 PL 配置

3. 加载 SSBL 引导程序或是ARM的裸跑程序到 DDR

4. 跳转执行 SSBL 或裸跑程序

FSBL 的任务如上所示,整个思路还是非常清晰的。

第1步就是对 PS 端初始化,包括 DDR,MIO 等。

第2步就是PL的配置,也就输传统的 FPGA 下载 bit 流的过程,但要注意的是,在 Zynq 的非 JTAG 模式下,PL 是无法直接自行配置的。

第3步是加载 SSBL 或裸跑程序到 DDR 内存中,其中 SSBL,Second Stage Boot Loader,是在 Zynq 需要运行操作系统时才进行加载。而像我们入门学习时做的点亮 LED 灯实验,就只是属于裸跑程序。

最后第4步,ARM 会跳转到 DDR 中执行所加载的程序。所以 FSBL 阶段的运行思路是很好理解的。

在这里插入图片描述

Zynq启动阶段2——SSBL

SSBL 在 Zynq 的启动过程中是可选的一个阶段,就像所提到的点亮 LED 实验,包括一些其他的比较小型的程序,如果不需要用到操作系统的话,那么 Zynq 的启动流程到 FSBL 阶段就足够了。

因此,SSBL 是面向于需要运行操作系统的应用场合。相信熟悉操作系统启动知识的朋友到这里应该很清楚了,SSBL 就是操作系统在启动过程中的引导程序 boot loader。

对于 Linux 而言,Zynq 的 SSBL 阶段和 u-boot 的作用是相同的。具体来说,SSBL 的作用就是将 Zynq 所需要的操作系统加载到 DDR 内存之中。

到此,Zynq 的启动与配置就算完成了。Zynq 启动过程其实与传统的 ARM 开发过程类似,区别就在于它是PS + PL 的架构,所以在启动过程中,额外需要加载二进制 bit 流文件。Xilinx 将 Zynq 的启动划分为3个阶段,从结构上看也是科学合理的。

总结

本文主要与大家分享了 Zynq 在非 JTAG 模式下的启动配置流程,旨在让大家对 Zynq 的三阶段启动模式有一个具体的认识,希望大家多多交流。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章