资料下载

×

神经网络图像压缩算法的FPGA实现技术研究论文免费下载

消耗积分:0 |

格式:rar |

大小:4.83 MB |

2021-03-22

神经网络图像压缩是图像压缩和神经网络领域的主要研究方向之一,基于多层前馈神经网络的压缩算法在神经网络压缩算法中最有代表性。本文结合国家某科研项目对该类算法的硬件实现进行研究,具有重要的理论和实用价值。

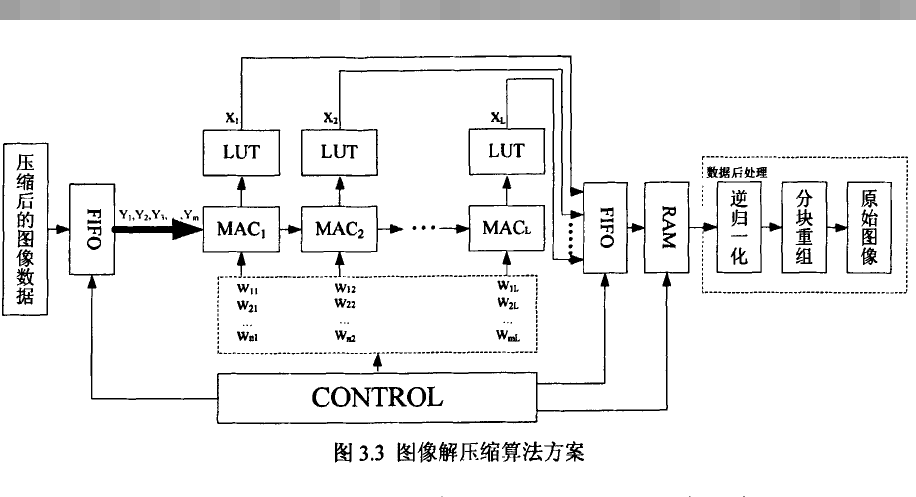

本文重点研究用FPGA(现场可编程门阵列)实现神经网络图像压缩的技术问题,论文提出了一种用FPGA实现图像压缩算法的技术方案,并提出该方案中重要模块的设计方案,详细给出了设计思路、模块结构及硬件时序仿真结果。

本文首先介绍了神经网络图像压缩的现状,研究了三层前馈神经网络理论以及BP算法。给出了基于三层前馈式BP网络的图像压缩及解压缩算法,选择合适的传输函数,使用一些图像对神经网络进行了训练,得出网络的重要参数,完成了针对图像压缩的BP网络设计。

其次,本文针对给出的基于三层前馈式BP神经网络的图像压缩及解压缩算法,对主要的硬件实现方案进行了对比,论证了使用FPGA实现的优点,提出了一种用FPGA实现图像压缩算法的技术方案。然后,对FPGA实现方案中的主要模块的电路设计思路和设计结构进行了研究,提出了针对通用设计方法的相应改进,给出了时序仿真波形图及图像压缩算法的FPGA电路原理图。

最后,分析和硬件仿真结果表明,本文所提出的基于FPGA的神经网络压缩方案合理可行,具有一定先进性和实用性,对相关研究工作具有重要参考价值。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章