专为工业应用而设计的MOSFET—TOLT封装

电子说

描述

【导读】近年来,工业应用对MOSFET 的需求越来越高。从机械解决方案和更苛刻的应用条件都要求半导体制造商开发出新的封装方案和实施技术改进。从最初的通孔封装(插件)到 DPAK 或 D2PAK 等表面贴装器件 (SMD),再到最新的无引脚封装,以及内部硅技术的显著改进,MOSFET 解决方案正在不断发展,以更好地满足工业市场新的要求。本文介绍了 TOLT 的封装方案、热性能和电路板的可靠性。

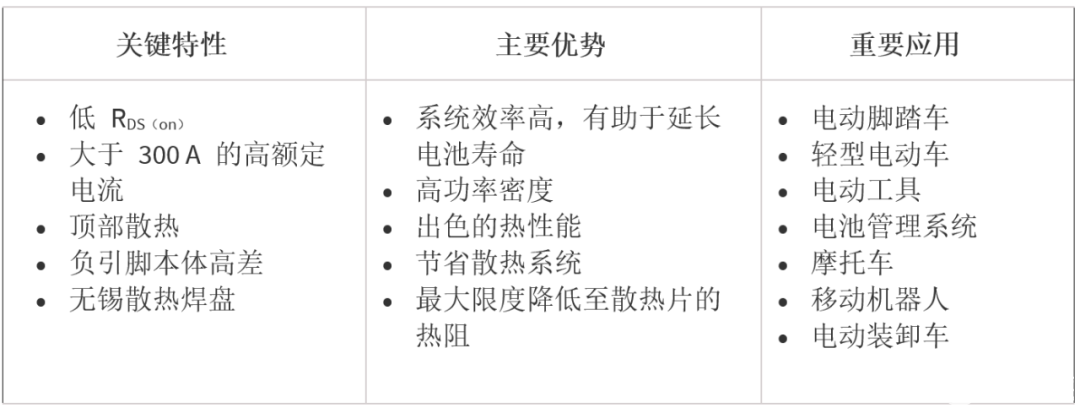

关键特性,主要优势和应用

目标应用市场

英飞凌公司的 TOLT(JEDEC:HDSOP-16),封装OptiMOS™ 5 功率 MOSFET,有助于实现非常高的功率水平。由于通过顶部冷却改善了热阻,TOLT 可以在不增加器件数量和系统尺寸的情况下满足功率要求高的应用需求。因此,TOLT 封装的重点应用是大电流应用。该封装适用于功率水平高达 50 kW 的大功率电机驱动器,具体应用如下:

图1 具体应用

封装设计

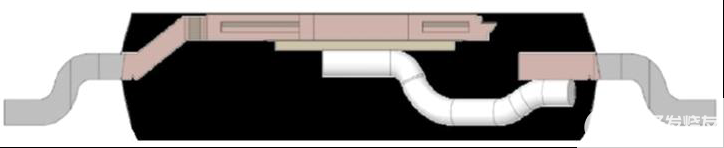

新 TOLT 封装的概念不同于标准的底部散热功率 MOSFET。在 TOLT 中,封装内的引线框架倒置,漏极焊盘(芯片底部 = 漏极连接)暴露在封装顶部。图2 为带有倒置引线框架的封装的侧视图。

图2 TOLT 侧视图

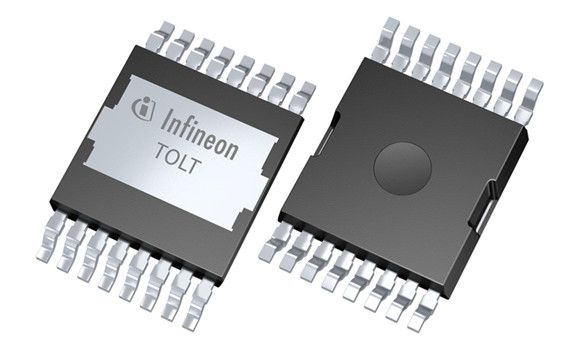

封装外形

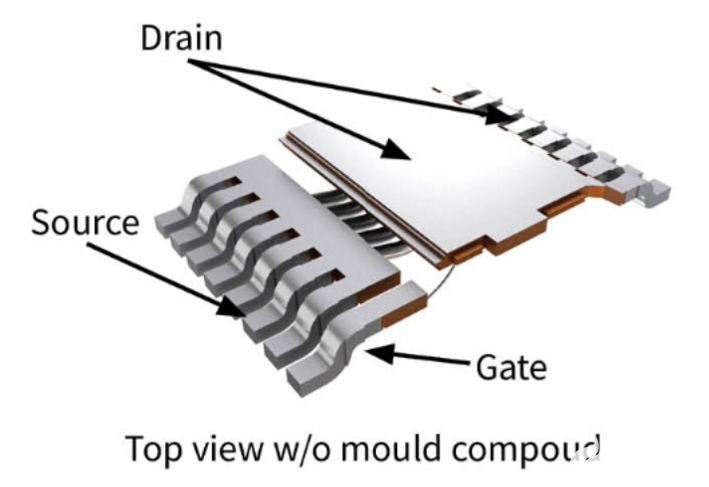

图3 和图4 为栅极、源极和漏极引脚。一排八个引脚连接到顶部的裸露焊盘,以与电路板进行漏极连接。在封装的另一侧,一个引脚用于栅极控制,其余七个引脚连接到电流源极。

图3 TOLT 3D 视图

图4 TOLT 底视图

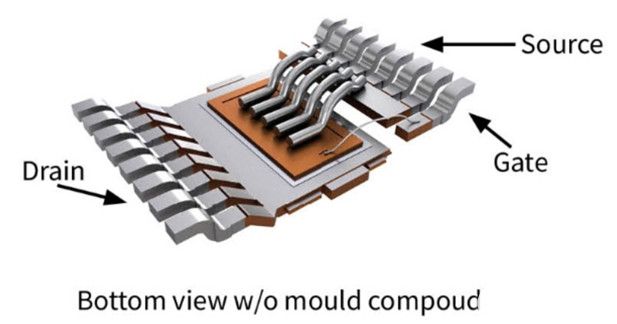

图5为 TOLT 封装尺寸细节。两个方向的高度容差都保持在±0.05 mm。负引脚本体高差的容差为 0.01 至 0.16 mm。

图5 尺寸图

TOLT优势和准则

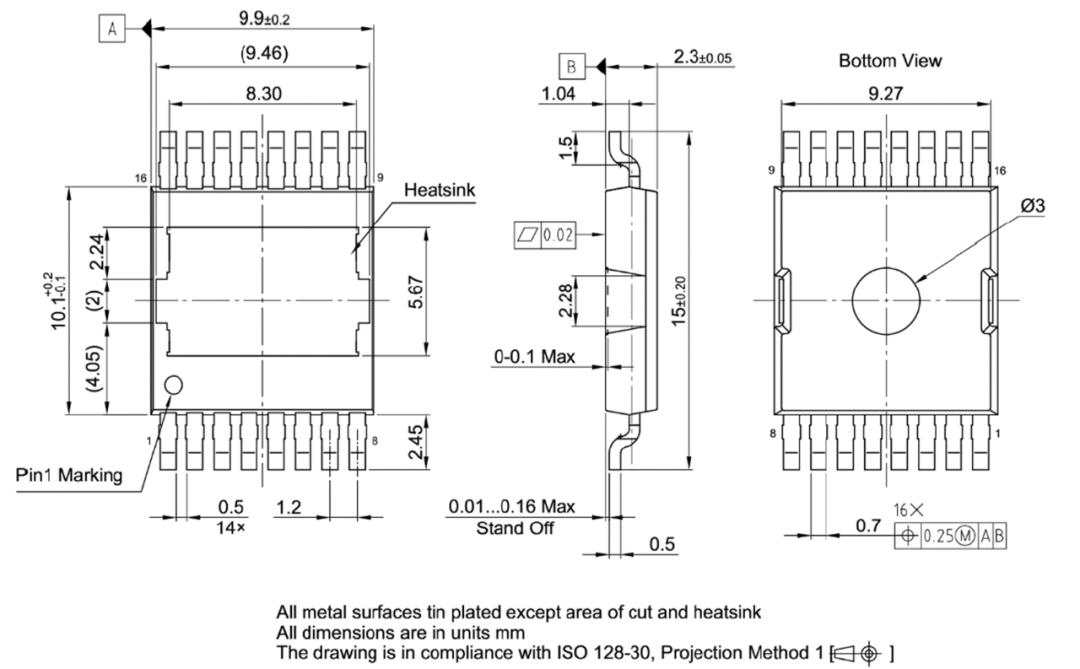

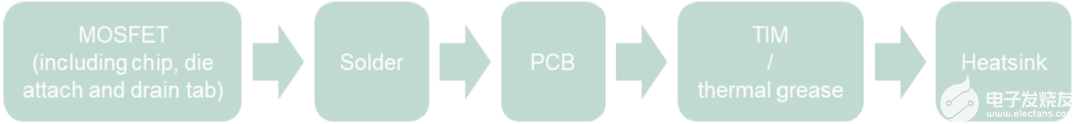

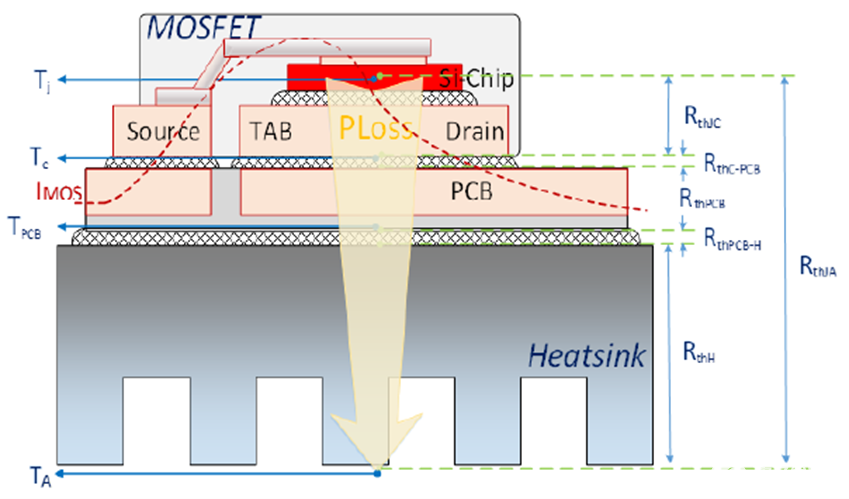

顶部散热不仅可以获得更高的应用功率,而且还有其他几个重要优势。在标准散热方案中(图6),散热器通常安装在 PCB 下方。从芯片到外部的热传递路径如下:这种解决方案的缺点是热性能降低,具体取决于 PCB 和 TIM/导热膏参数。这些组件的导热性差可能会导致过热和应用功率降低,还可能意味着需要更高的散热成本。此外,组装板需要承受更高的温度,这就需要使用更昂贵的 PCB。

图6 背面散热方式中的热路径

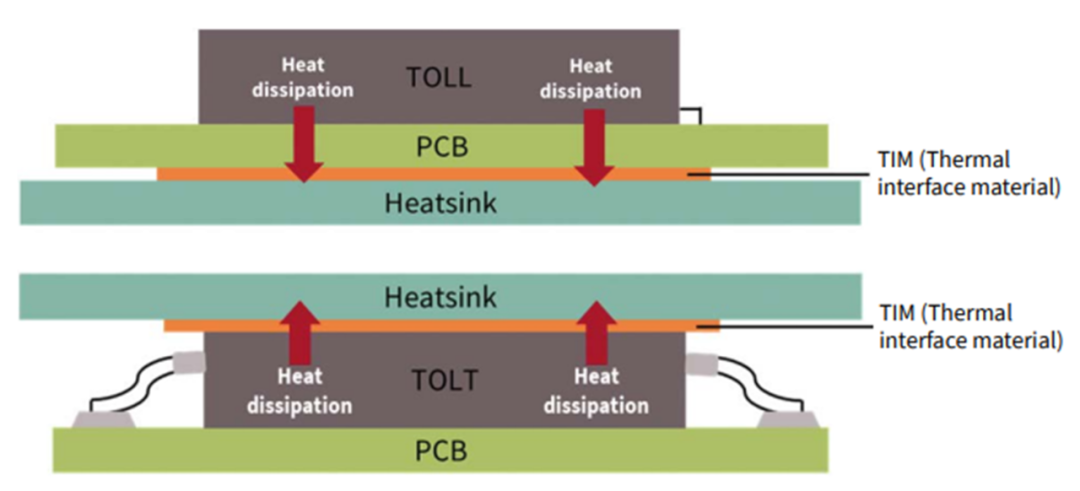

而得益于顶部散热方案(图7),热路径可以显著缩短:通过消除热路径中的 PCB 和焊料互连来减少热路径对 MOSFET 性能有巨大的影响。

图7 顶部散热方式中的热路径

英飞凌研究了这两种解决方案比较:找正品元器件,上唯样商城。

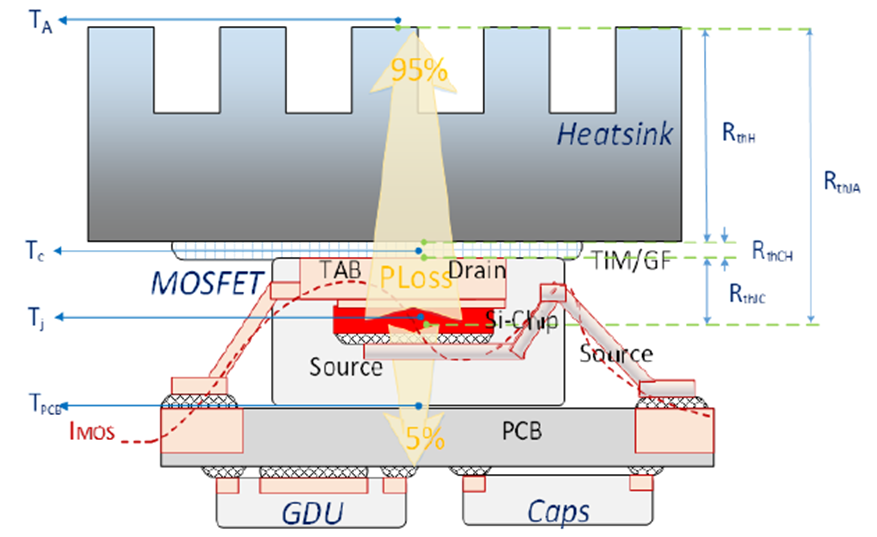

1.依托顶部散热设计,漏极暴露在封装表面,显著降低管芯和散热器之间的热阻,可将 95% 的热量通过散热器传递,只有5%通过PCB传递(图8),诸如 TOLL 或 D2PAK 等底部散热型封装(图9),其热量均通过 PCB 传导至散热片,从而会导致功率损耗较高。

图8

图9

2.SMD组件可以放置在PCB底部的TOLT MOSFET下方(图10),以优化可用面积;

图10 TOLL & TOLT 散热示意图

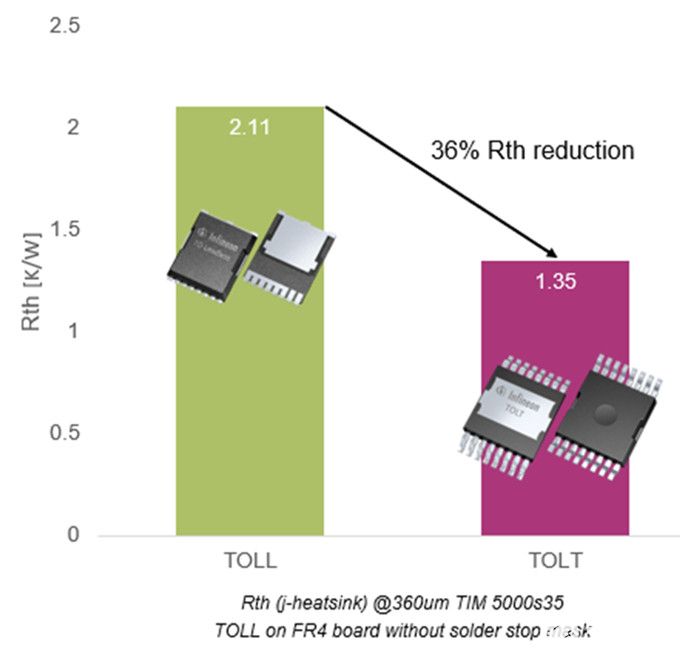

3.TOLT增加电流/功率处理能力,相较于 TOLL 封装,TOLT 封装的 RthJA 降低了 20%,RthJC 改善近 50%, Rth(J-heatsink) 降低了36% (图11)。

图11

4.额外优势

除了可以为散热系统实现更高的功率密度或节省成本外,TOLT 产品还有其他优势。以下是一些示例:

● 由于散热器没有安装在 PCB 下方,也没有热量通过 MOSFET 底侧传递到电路板,因此栅极驱动器或电容可以放在 PCB 的另一侧。这样的解决方案能够更有效地利用 PCB 空间。

● 增加爬电距离(源极和漏极电势之间的距离)。

● 可以使用具有较低玻璃化转变温度的 PCB。

● 传递到 PCB 和附近组件中的热量更少。

5.热界面材料厚度

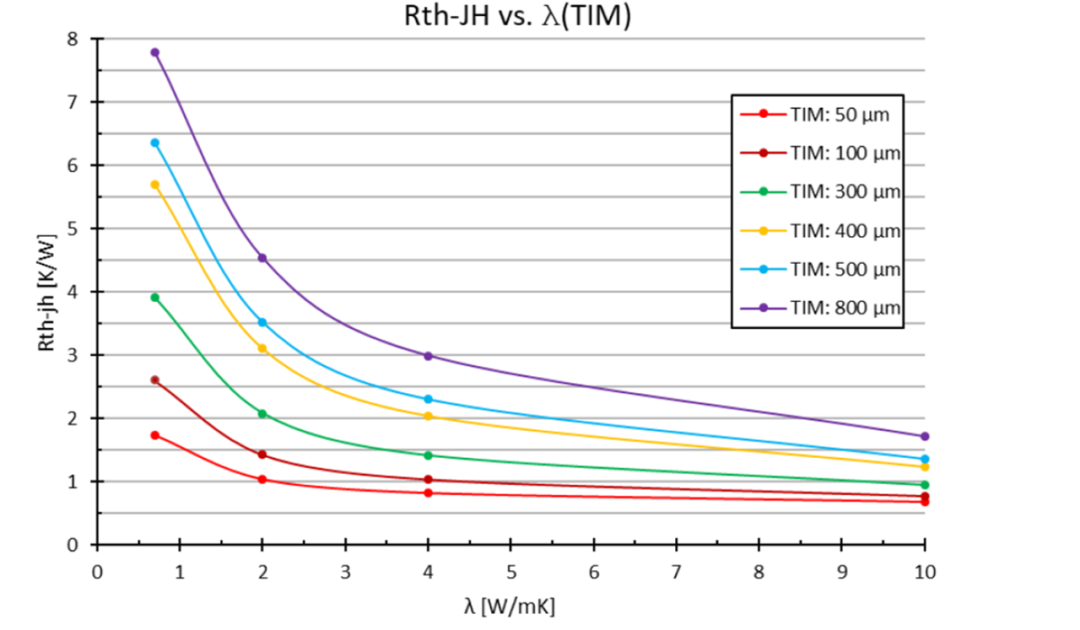

为保证 TOLT 封装的最佳热性能,并保证封装尽可能低的热阻,优化 TIM 厚度就显得至关重要。英飞凌为 TOLT 封装模拟了几种不同 TIM 厚度的情况(图12),从而分析其对从结到散热片总 RTH 的影响。在模拟中,散热片温度固定为 85°C 的环境温度。

图12 为 Rth 对于不同 TIM 厚度的 TIM 热导率的相关性

从图中可以看出,TIM 越薄,热阻越低。但是,应注意 TIM 的热导率 (λ) 值。更好的热导率补偿了 TIM 厚度的负面影响。

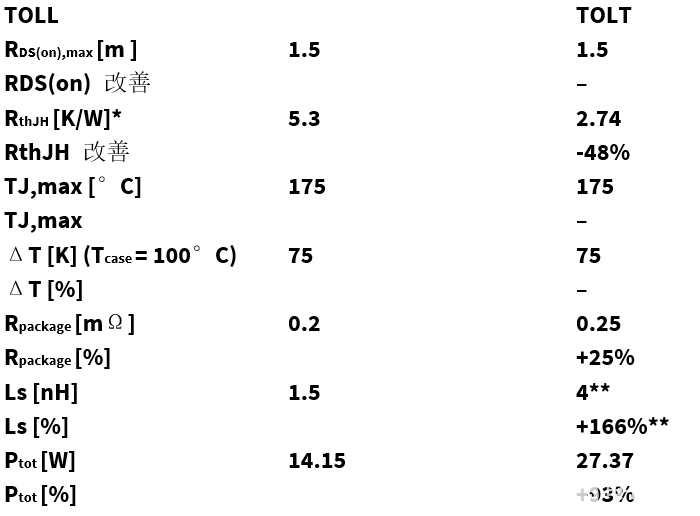

市场上现有的 TIM 的热导率通常在 3 到 6 W/mK 之间。为了达到最佳的热性能和足够的电隔离相平衡,系统工程师应优化 TIM 的厚度和热参数。下表为一些目前市场上现有的 TIM 示例。

客户最常用且在市场上广泛使用的材料是热导率在 3 至 4 W/mK 范围内的 TIM。根据对该值的仿真,MOSFET 结和散热片之间的热阻在 0.8 和 3K/W 之间变化,具体取决于 TIM 厚度。实际 TIM 厚度为 300 至 500 μm 时,热阻值可达 1.5 至 2.4K/W。当 Rth 等于 2.4 K/W 且 MOSFET 结与外壳之间的温差为 90°C(假设 Tcase = 85°C 和 Tjmax = 175°C)时,单个 TOLT MOSFET 可消耗大约 40 W 的功率。

6.电参数

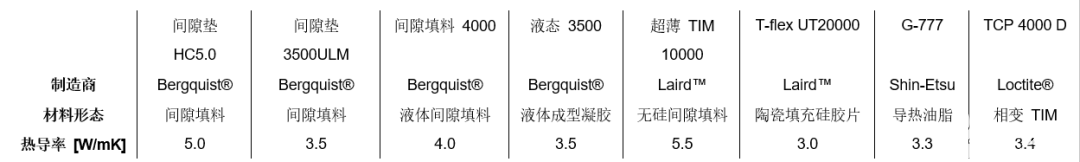

TOLT 封装中的 MOSFET 具有与相应 TOLL 部件相同的 RDS(on) 值。例如,采用 TOLT 封装的出色的100V MOSFET(IPTC015N10NM5) 和相应的TOLL(IPT015N10N5),RDS(on),max 均为 1.5 mΩ。

参数比较:TOLL vs. TOLT

与 TOLL 相比,在带过孔的普通 2s2p 电路板和 85°C 的环境温度条件下,TOLT 的最大改进之处在于结到散热片的热阻 Rth 明显降低。Rth 降低了近 50%,这会导致总耗散功率提高 90% 以上。

TOLT的电路板可靠性

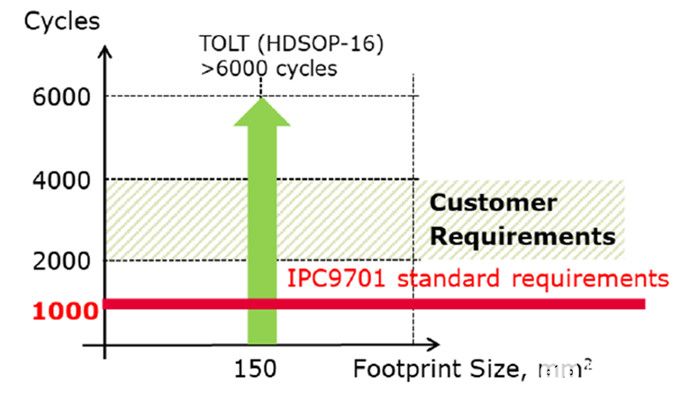

所有 SMD MOSFET 的另一个重要方面是不同应用条件下的电路板的可靠性。在苛刻的工业应用中使用这些 MOSFET 会使部件承受巨大的机械应力。用于评估 PCB 上封装可靠性的最常见测试是板上温度循环 (TCoB) 测试。TOLT 封装的散热片安装在封装顶部,因此还必须研究该部件可以承受的最大机械应力。

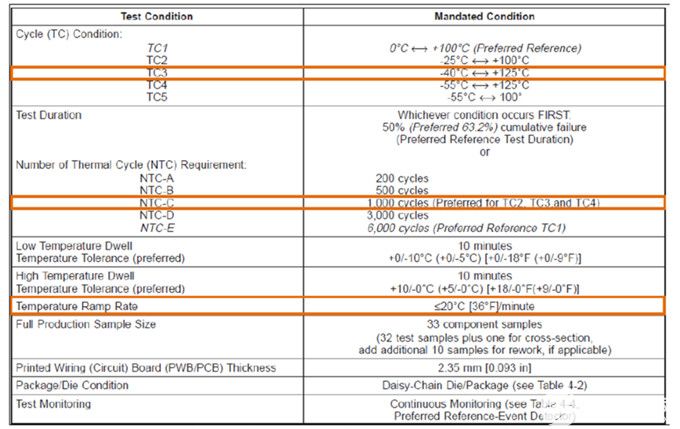

1. 板载温度循环可靠性

电子元件在工作期间会暴露在不断变化的温度下,这会导致材料膨胀。每种材料都有其自身的热膨胀系数,如果应力足够大,热膨胀率的差异可能会导致焊点出现裂纹。证明对热机械应力的鲁棒性的测试就是 TCoB 测试。IPC-9701 标准确定了应该如何以及在何种条件下进行 TCoB 测试。

图13 IPC-9701:表面贴装焊接部件的性能测试方法和验证要求

图14 为汽车应用中零部件的测试条件

从图13 和图14 中可以看出,汽车零件应能 -45°C 至 +125°C 下承受 1,000 次循环,期间无故障出现。尽管通过了工业验证,英飞凌 MOSFET 仍根据更严格的汽车标准进行了测试。根据标准要求,升温速率应小于每分钟 20°C。然而,在英飞凌的 TCoB 测试期间,升温速率条件为每分钟 60°C。这会增加器件上的应力,还能满足更严格的热冲击测试要求。这种严苛的测试条件使英飞凌的封装承受了比 IPC-9701 标准要求更大的应力,从而证明了其卓越的鲁棒性和电路板级可靠性。

在英飞凌进行的 TCoB 测试期间,TOLT 部件受到监控,电气故障的标准是电阻增加 20%。图15测试结果表明,TOLT 封装可以承受至少 6,000 次循环而不会出现电气故障。6,000 次循环后,测试结束。

图15 TOLT 在 TCoB 测试中达到至少 6,000 次循环

热仿真

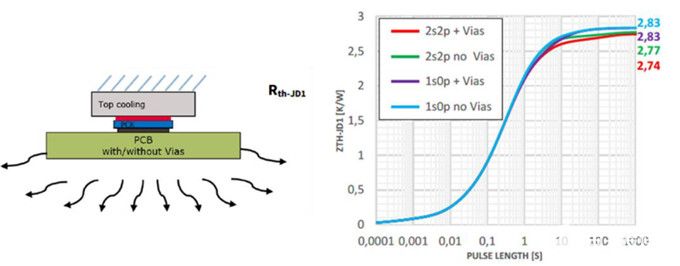

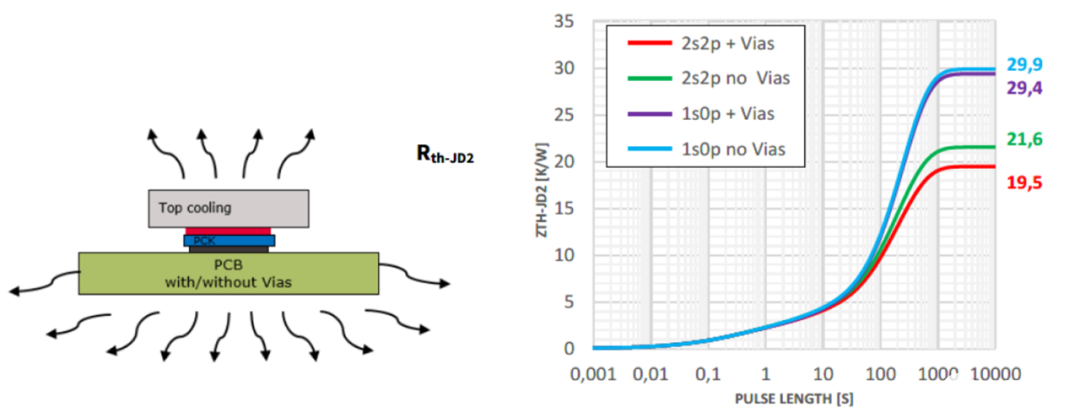

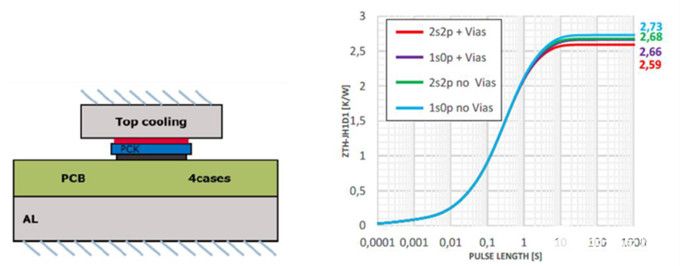

本节将介绍和讨论不同电路板和散热片安装配置的热仿真结果。在图表中可以看到各种配置的热阻抗值。

在两种不同的散热系统结构下,仿真了从结到环境的热阻:

a) 在固定环境温度下,通过顶部散热的 Rth_JD1 (图16),以及通过顶部散热,同时让散热片保持自然对流的 Rth_JD2 (图17)。

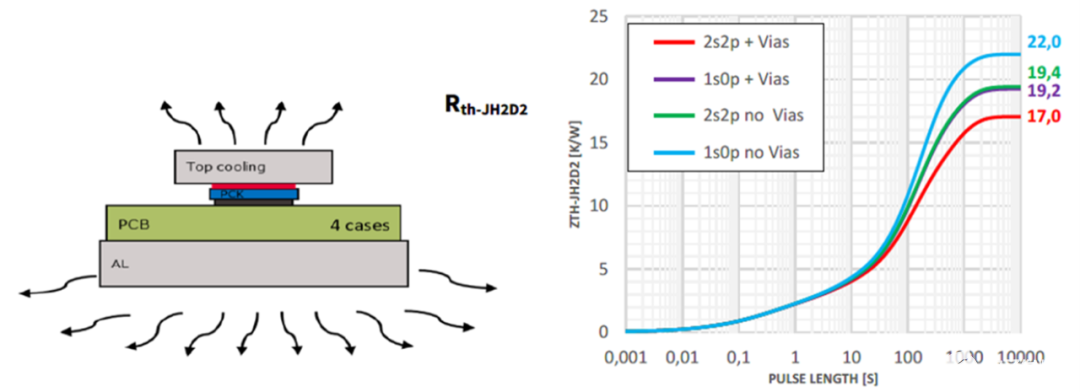

b) 在固定环境温度下,通过 PCB 和顶部散热 的Rth_JH1D1 (图18),以及在自然热对流下,通过 PCB 和顶部散热的 Rth_JH2D2 (图19) 。

对于每种散热方式,仿真了四种不同的 PCB 配置:2s2p(四层 PCB,铜厚 1 oz. – 2 oz. – 2 oz. – 1 oz. ), 带和不带过孔,以及 1s0p(单层 PCB,铜厚 1 oz. ),带和不带过孔。所选 TIM 的热导率为 0.7 W/mK,厚度为 100 μm。在相关情况下,环境温度设置为 85°C。

如图16所示,对于顶部散热,在热量直接传递到主动冷却的散热片(温度固定)时,PCB 的选择在 Zth 性能方面没有显著差异。这意味着可以使用玻璃化转变温度较低的更经济的电路板。无论使用哪种电路板, 热阻抗值都约为 2.8 K/W。

图16 不同电路板的 TOLT 热阻抗;顶部散热温度固定为 Tambient

图17 不同电路板的 TOLT 热阻抗;自由热对流

但在自由热对流 (图17) 的情况下,电路板的选择可能会有所不同,因为一些热量会传递到 PCB。普通 2s2p 电路板的热阻将增加到 19.5 K/W。

此外,仿真结果表明,如果在 PCB 下方安装第二个散热片,热性能不会显着提高。例如,没有过孔的 2s2p 电路板,其封装上方只有一个散热片,而 PCB 下方没有散热片,电路板热阻抗为 2.77 K/W。如果在电路板下方增加一个散热片,热阻抗仅略微降低到 2.59 K/W,这可以忽略不计。图18和图19为两侧均带有散热片的仿真结果。

图18 不同电路板的 TOLT 热阻抗;顶部散热温度固定为 Tambient

图19 不同电路板的 TOLT 热阻抗;自由热对流

总结

新型顶部散热 TOLT 封装,为大功率工业应用在 FR4 PCB 上实现。TOLT 由于缩短了从管芯结到散热片的热路径,因此改善了热阻,从而提高了电气性能。

为了确保最佳热性能,在开发 TOLT 封装过程中,英飞凌设计人员采取了不同的措施。这些措施包括最小化封装高度,引入引脚的负引脚本体高差,并采用无锡散热焊盘。影响 TOLT 产品整体热性能的一个关键方面是封装顶部和散热片之间的热界面材料 (TIM)。设计人员可以在 TIM 的厚度、热导率和价格之间权衡,从而实现预期的热性能。热仿真证实,与在 FR4 PCB 上的标准底部散热解决方案相比,封装的热阻有了显著改善。除了仿真外,还进行了可靠性试验,例如板上温度循环、弯曲和压缩测试。实验结果证明,TOLT 封装在顶部有额外负载压力的情况下可以承受足够数量的热冲击循环,这超过了通用标准的要求。

审核编辑:汤梓红

-

LT5506的典型应用专为低电压操作而设计2019-08-29 1971

-

LT5500的典型应用是专为低电压工作而设计的接收器前端IC2019-08-30 2025

-

KIT10XS3535EVBE,评估板支持10XS3535,专为低压汽车和工业照明应用而设计2019-09-26 2366

-

解密ACRN:一个专为物联网而设计的Hypervisor2020-05-05 2196

-

专为低功耗数字电话应用而设计的高性能电流模式开关稳压器2020-07-29 1637

-

专为QR ZVS反激式转换器而设计准谐振电流模式控制器IC2020-08-12 3243

-

LFPAK33中的N沟道 100V,36.6 mΩ 标准电平 MOSFET,专为高功率 PoE 应用而设计-PSMN040-100MSE2023-02-23 466

-

英飞凌推出TOLT和Thin-TOLL封装的新型工业CoolSiC™ MOSFET 650 V G2,提高系统功率密度2024-09-07 2300

-

TOLL/TOLT 封装系列:区别有哪些?2025-05-13 3365

-

仁懋TOLL/TOLT封装系列区别在哪?2025-06-04 1648

-

专为低功耗/802.15.4/Thread/Zigbee/蓝牙®应用而设计的 2.4 GHz 前端模块 skyworksinc2025-06-05 121

-

仁懋TOLT封装MOS——专为大功率而生2025-06-18 2367

-

超越国际巨头:微碧半导体VBGQTA1101以顶尖TOLT封装重塑功率密度标杆2025-10-11 32169

-

英飞凌推出专为高功率与计算密集型应用而设计的400V和440V MOSFET2025-10-31 547

-

Wolfspeed最新推出TOLT封装650V第四代MOSFET产品组合2026-01-21 3322

全部0条评论

快来发表一下你的评论吧 !