资料下载

关于Ultra96的Xilinx DDS编译器IP教程

描述

直接数字合成器 (DDS) 是软件定义无线电和数字通信系统中的关键工具,因为它们提供了一种在数字域中生成复杂信号的方法,该信号也是可变的。虽然 DDS 背后的理论相当简单,但第一次在 FPGA 中实现它可能有点挑战性,这就是为什么我想创建这个项目作为一个非常简单的示例,说明如何采用 Xilinx DDS 编译器 IP 并获得它在 Ultra96 板的可编程逻辑中运行。

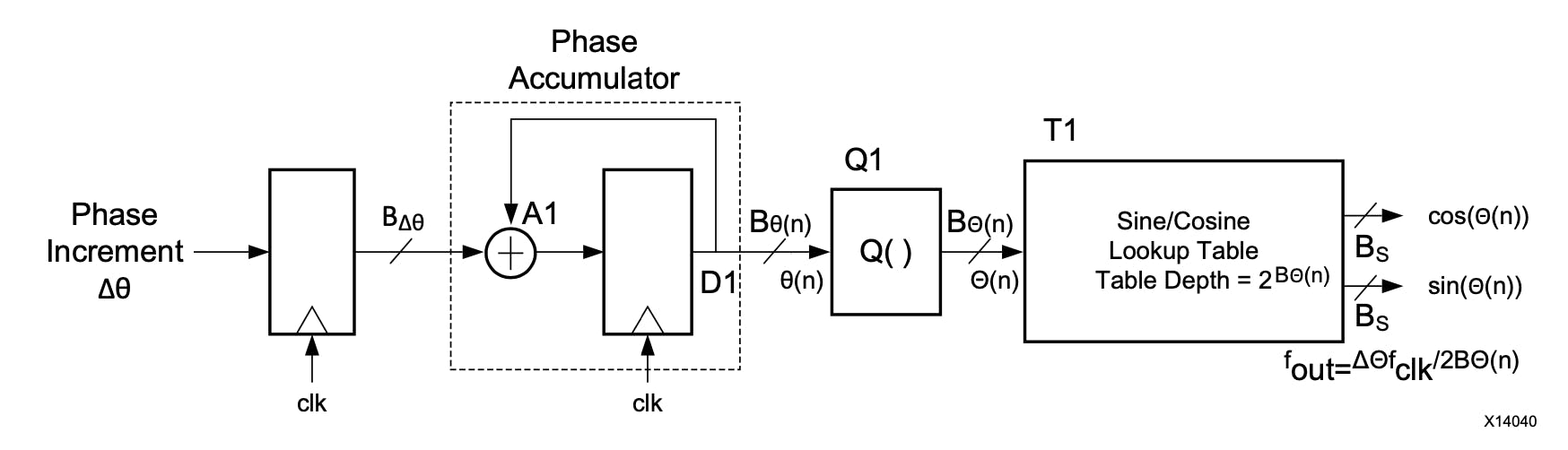

也称为数控振荡器 (NCO),DDS 包含一个正弦曲线数据值的查找表,该表采用给定的相位值并输出正弦曲线的适当数据/幅度值。该输入值决定了输出波形的频率,该值越小,DDS 通过正弦查找表的速度越慢,输出波形的频率越低。相反,输入值越高,DDS 通过查找表的速度越快,输出波形的频率越高。这个输入值通常被称为调谐字,但在赛灵思 DDS 编译器 IP 中,它被称为相位增量。

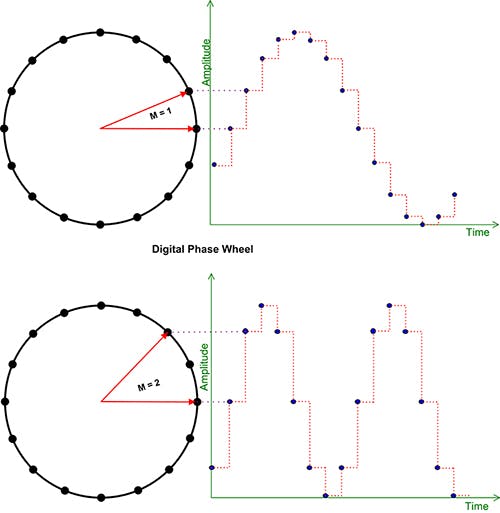

如上图所示,该相位增量值 (Δθ) 越大,代表复杂波形的单位圆周围的 DDS 步长越快。当 M 加倍时,产生的复杂波形的频率也加倍,因为它绕单位圆的速度是原来的两倍。与该单位圆的相位值相关的数据点存储在 DDS 的查找表中。

在这一点上,我们可以看到 DDS 的主要优势之一:我们可以通过改变告诉 DDS 多快通过查找表的输入值(又名 - 多快绕单位圆移动)。

输入相位增量值不断添加到自身 (A1 和 D1) 以生成所需输出波形的每个瞬时值,从而从查找表 (T1) 中获取该瞬时相位值的适当数据值/幅度。

为了演示 DDS 及其输出波形频率变化的容易程度,我决定一个简单的啁啾波形是合适的。啁啾是正弦曲线以一个频率开始,然后在一段时间内线性增加或减少(这有时也称为扫描)。

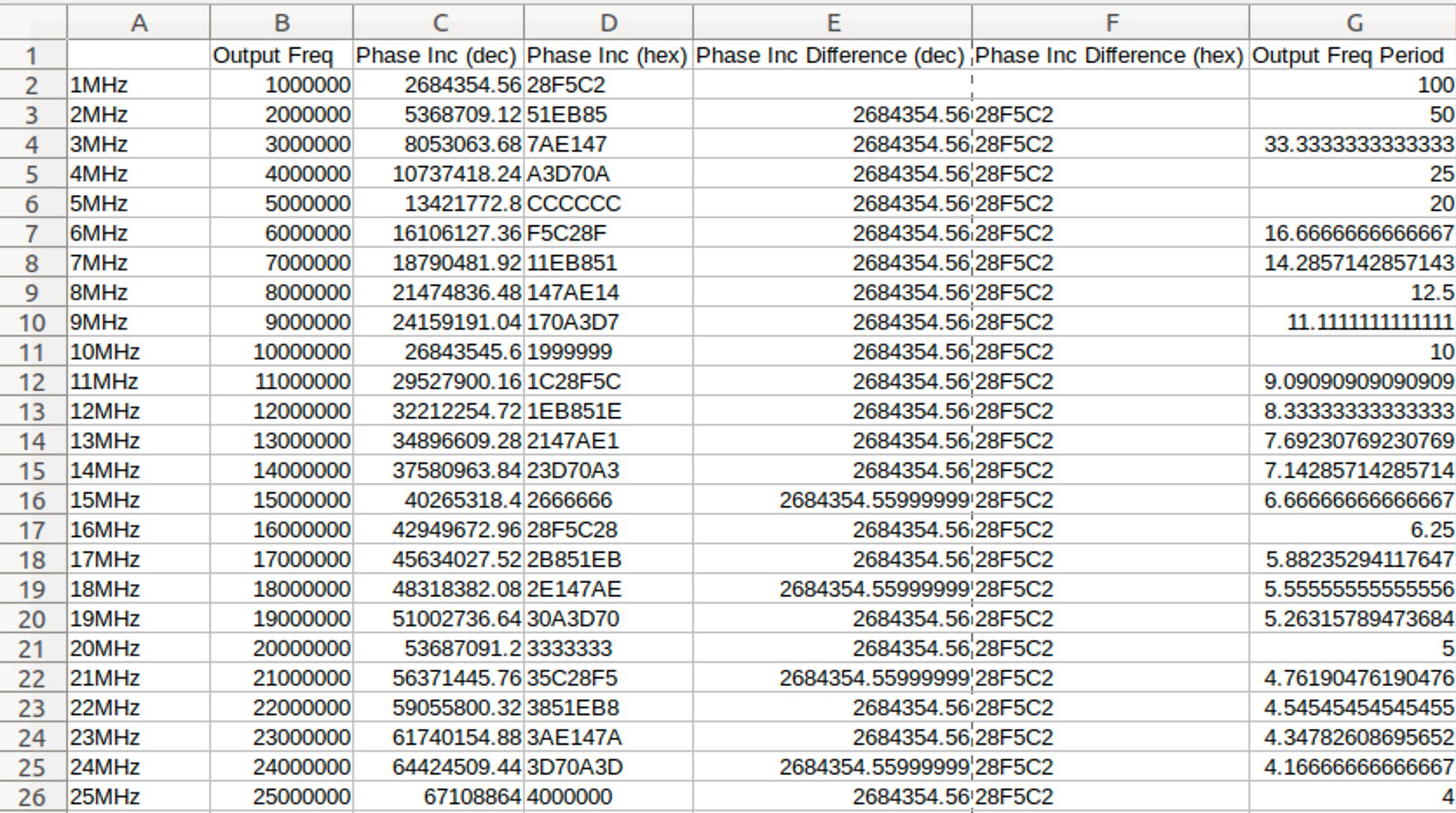

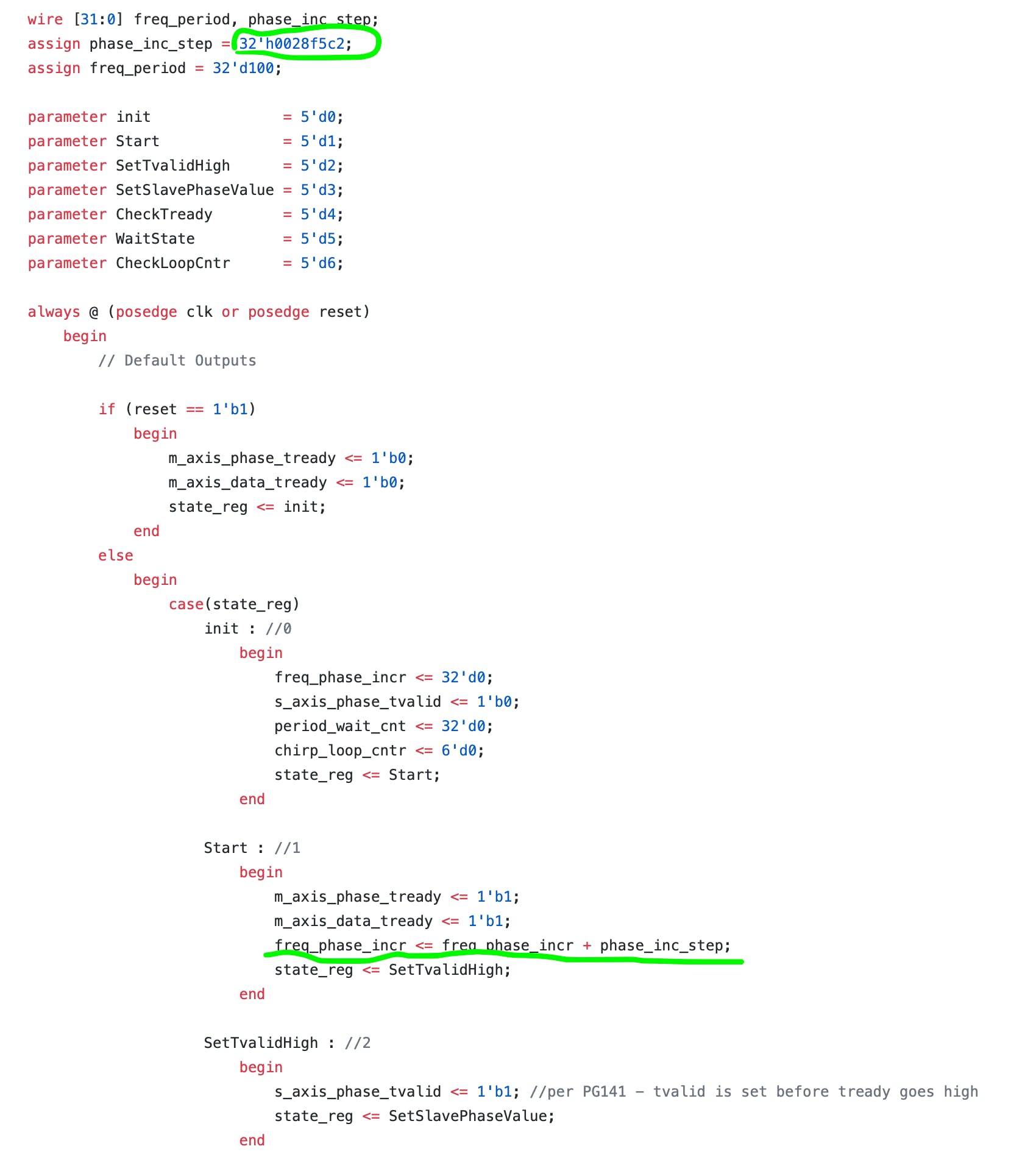

我决定在 26 微秒内以 1MHz 的步长从 1MHz 到 25MHz 做一个简单的啁啾(我的结构时钟是 100MHz,即每个时钟周期 10 纳秒,我随机选择让 DDS 编译器输出每个频率 1 微秒以便在逻辑分析仪窗口中轻松查看)。

通过递归地将 1MHz 的相位增量值添加到自身,然后将其作为输入馈送到 DDS 编译器,这实现了我的啁啾从 1MHz 到 FPGA 结构时钟的一半(在 ILA 中采样时保持奈奎斯特规则)以 1MHz 步长。我选择只提高到 25MHz,这样整个啁啾声就可以立即显示在我的屏幕上以进行截图,但是我的结构时钟设置为 100MHz,所以我可以提高到 50MHz。

我使用来自 PG141 的以下等式计算了 B 列中每个输出波形频率的 C 列中的相位增量值:

然后我将 C 列中的相位增量值转换为十六进制以去掉小数位,因为我是在 Verilog 中编写这段代码的。我创建了 E 列和 F 列来表明相位增量的差异确实导致了与 1MHz 相同的十六进制值。

从我在之前的一个项目中为 Ultra96 生成的 Vivado 项目开始,需要将三件事添加到此 DDS 啁啾的顶层包装器中:

1 - Xilinx DDS 编译器。2 - 与 DDS 的 AXI Stream slave 和 master 接口的逻辑。3 - 一个集成逻辑分析仪 (ILA) IP,用于查看 DDS 的输出波形。

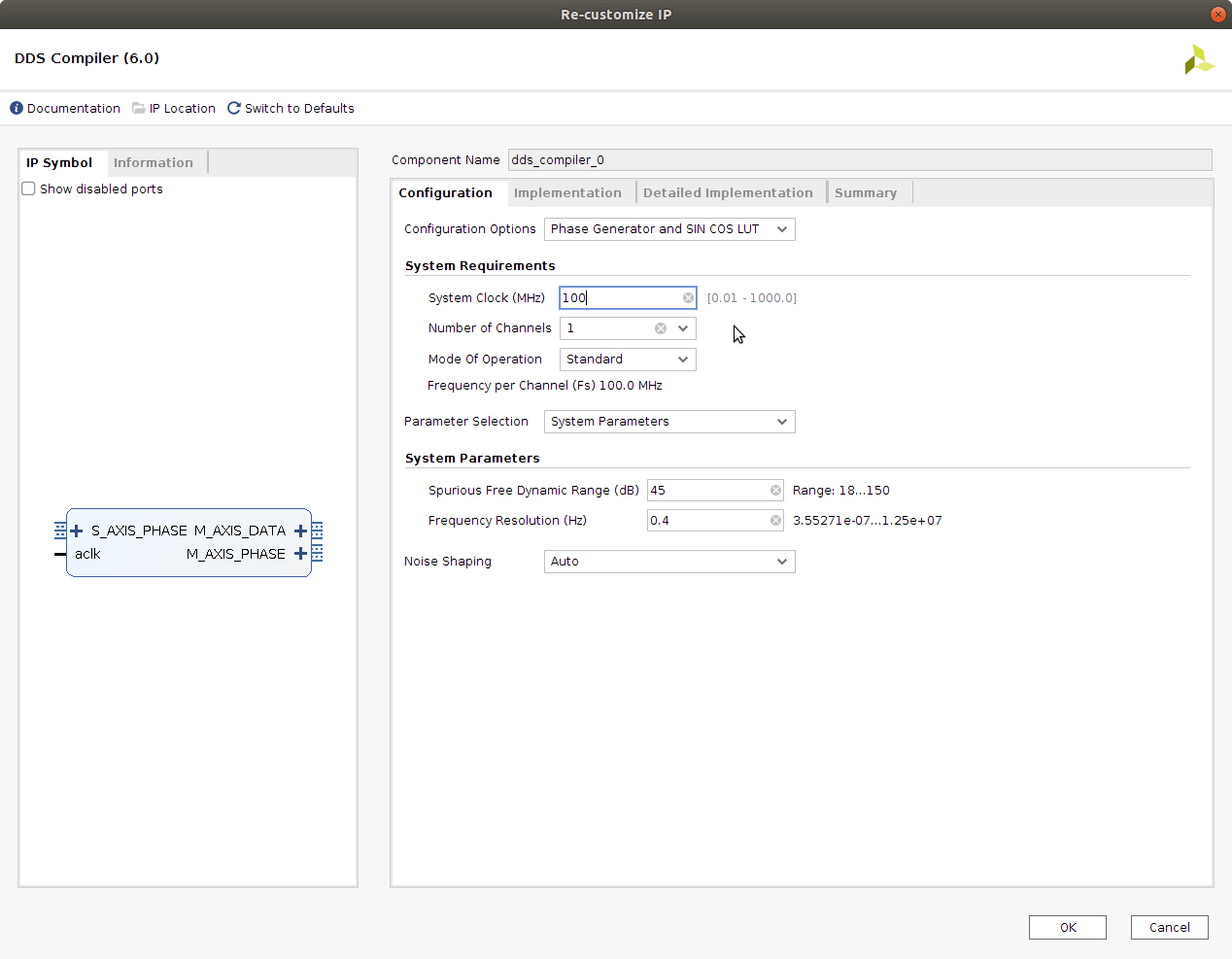

在 Vivado 的 Flow Navigator 列下,打开 IP 存储库并搜索“DDS”。当 DDS 编译器 IP 出现在 IP 存储库的列表中时,双击它后,将弹出一个对话框。单击“自定义 IP”按钮,将出现 DDS 编译器的配置窗口。

在如上所示的第一个选项卡中,出于我们的目的,所有默认设置都可以保留。

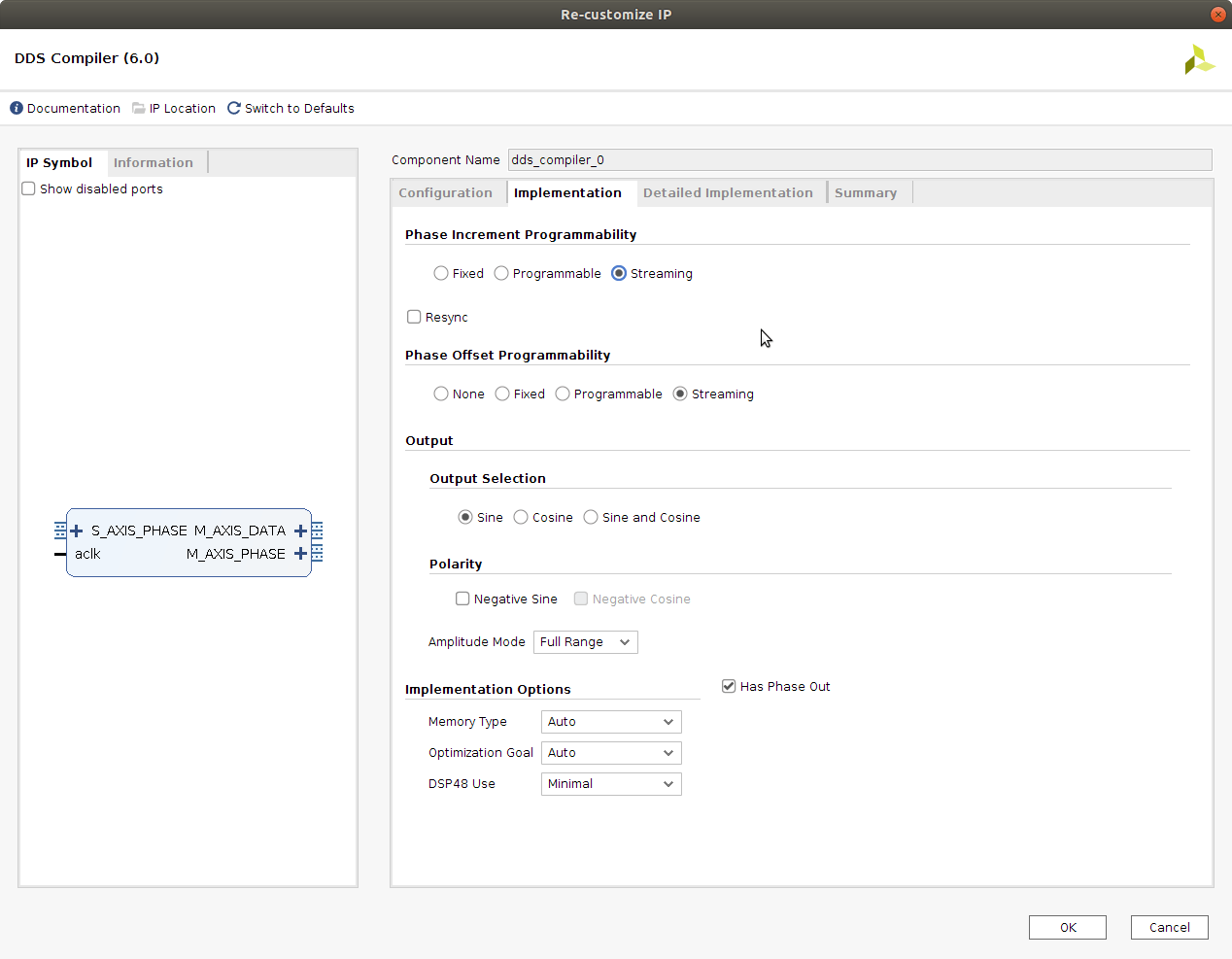

在第二个选项卡下,为相位增量和偏移可编程性选择流式传输。我发现这使得从 AXI Stream 接口变得最简单。

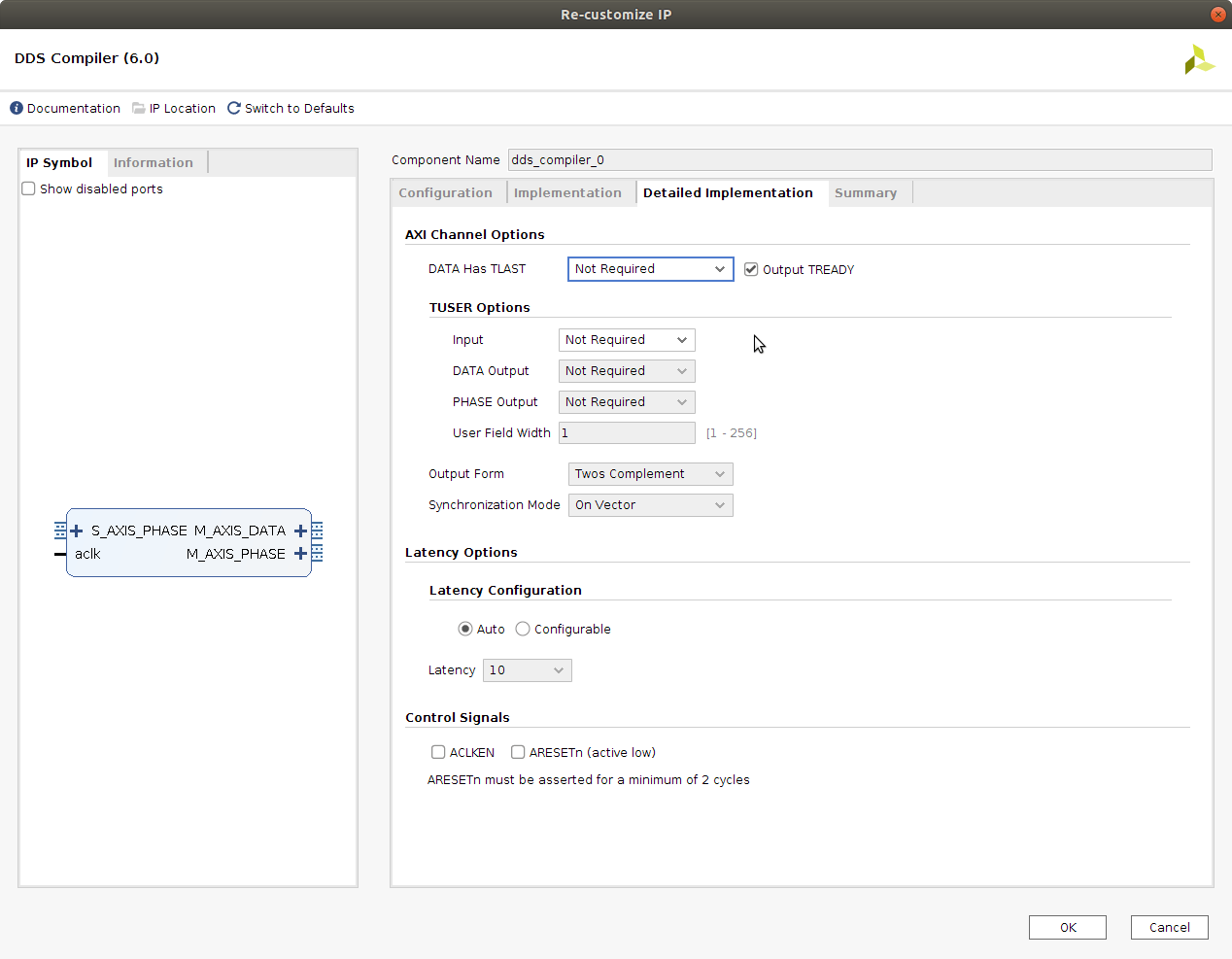

此外,对于 DDS 编译器的 AXI Stream 接口,在详细实现选项卡下,选中“输出 TREADY”框。我发现在处理 AXI Stream 时,TREADY 信号几乎总是一个必要的信号。

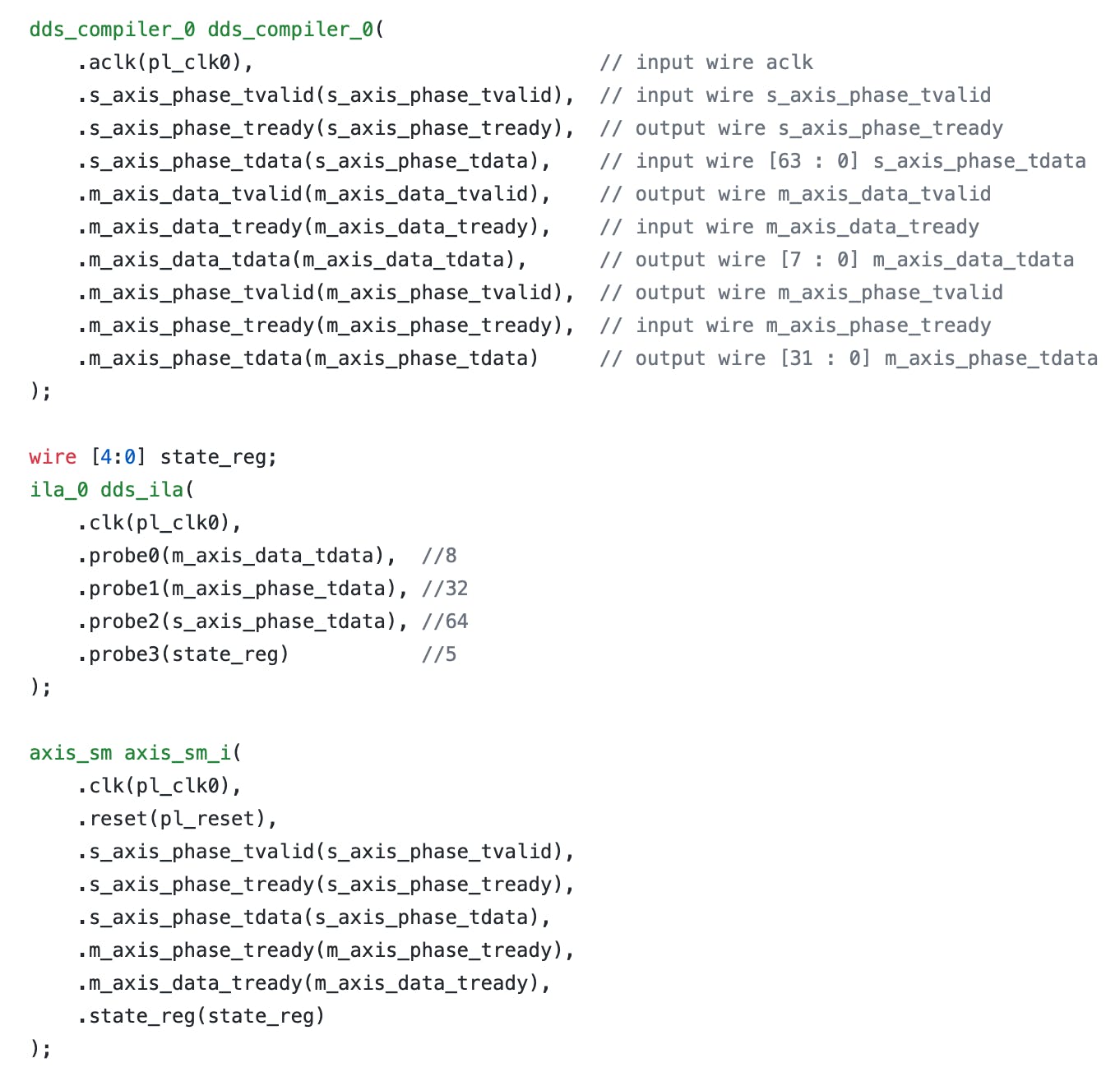

在添加 ILA 时,我总共添加了 4 个探针,用于监控 DDS 从接口上的输入相位增量值以及 DDS 在其主接口上的输出数据和相位值。我将 Ultra96 上的 UltraScale 芯片设置的深度尽可能大,以方便我的设计,即 65536。我建议始终尝试设置 ILA 以捕获尽可能多的数据。

例化 ILA 和 DDS IP 模块后,我编写了自己的简单状态机来创建 AXI Stream 接口,将相位增量值输入到 DDS,然后等待 1 微秒,然后将 1MHz 步长添加到相位增量值并输入到DDS。该状态机还保持计数,因此在达到 25MHz 的相位增量值后,它会在下一次迭代中回到 1MHz。

我发现这个简单的 AXI Stream 接口状态机在许多不同的应用程序中都非常方便。主要的逻辑步骤是:1 - 设置初始值。2 - 将目标 IP 的从接口上的 Tvalid 信号设置为高电平。3 - 设置要在目标 IP 的从接口上输入的数据值(相位增量值到 DDS 编译器)。4 - 检查来自目标 IP 的从接口的 Tready 信号,以验证它是否已准备好接收下一个数据值。

我的所有文件都在链接的 Github 存储库中,以及这里状态机的完整代码。

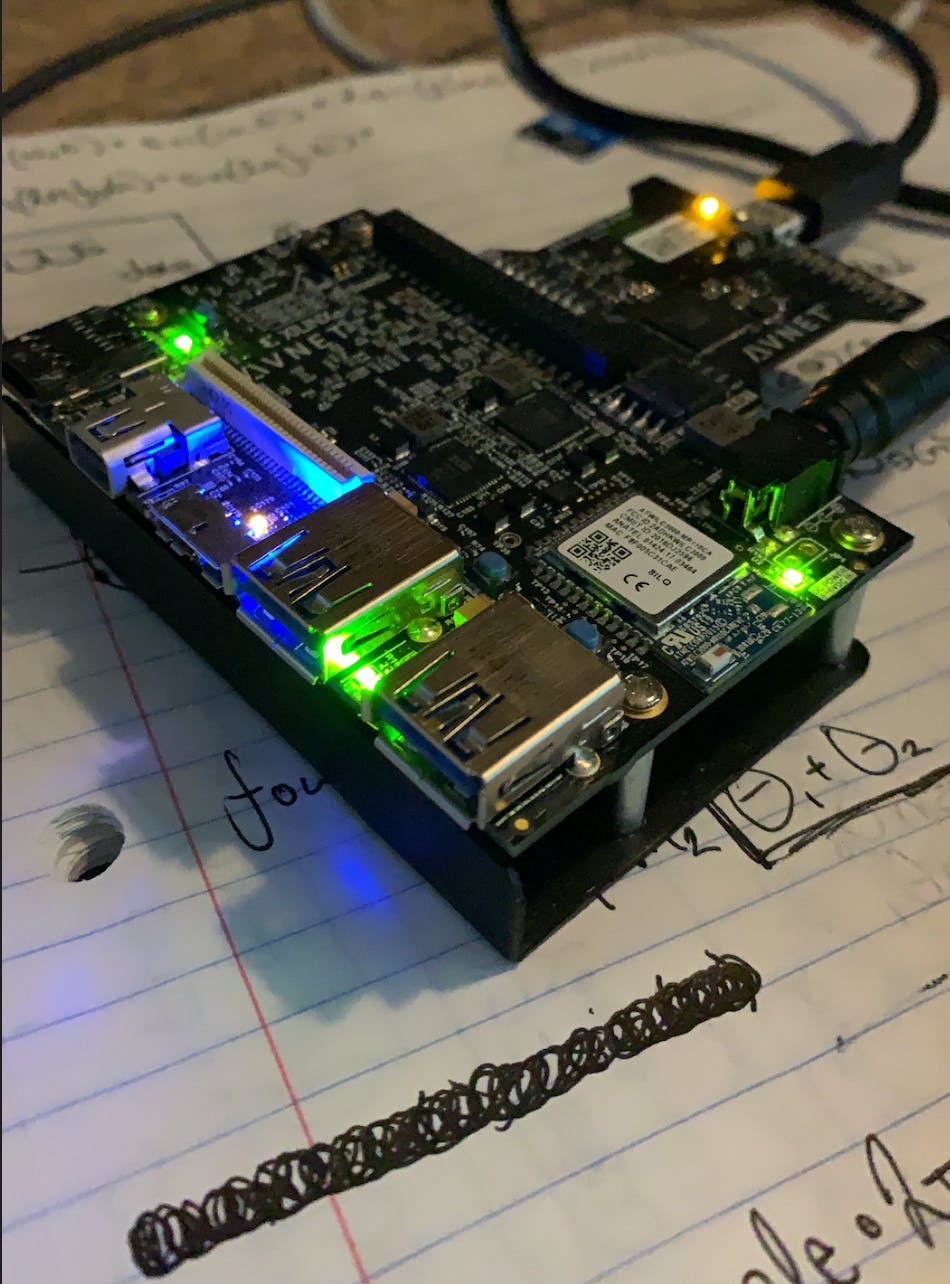

生成新的比特流后,打开 Ultra96 的电源并连接到其 JTAG 端口(您可以使用飞线完成此操作,但 Ultra96 的 JTAG 到 USB 接口将使您的生活变得更轻松)。

从 Vivado 的 Flow Navigator 中,选择Open Hardware Manager ,然后选择Open Target和Autodetect选项。一旦硬件管理器与 Ultra96 建立连接,选择Program Device选项并指定刚刚使用 DDS 逻辑创建的新比特流。

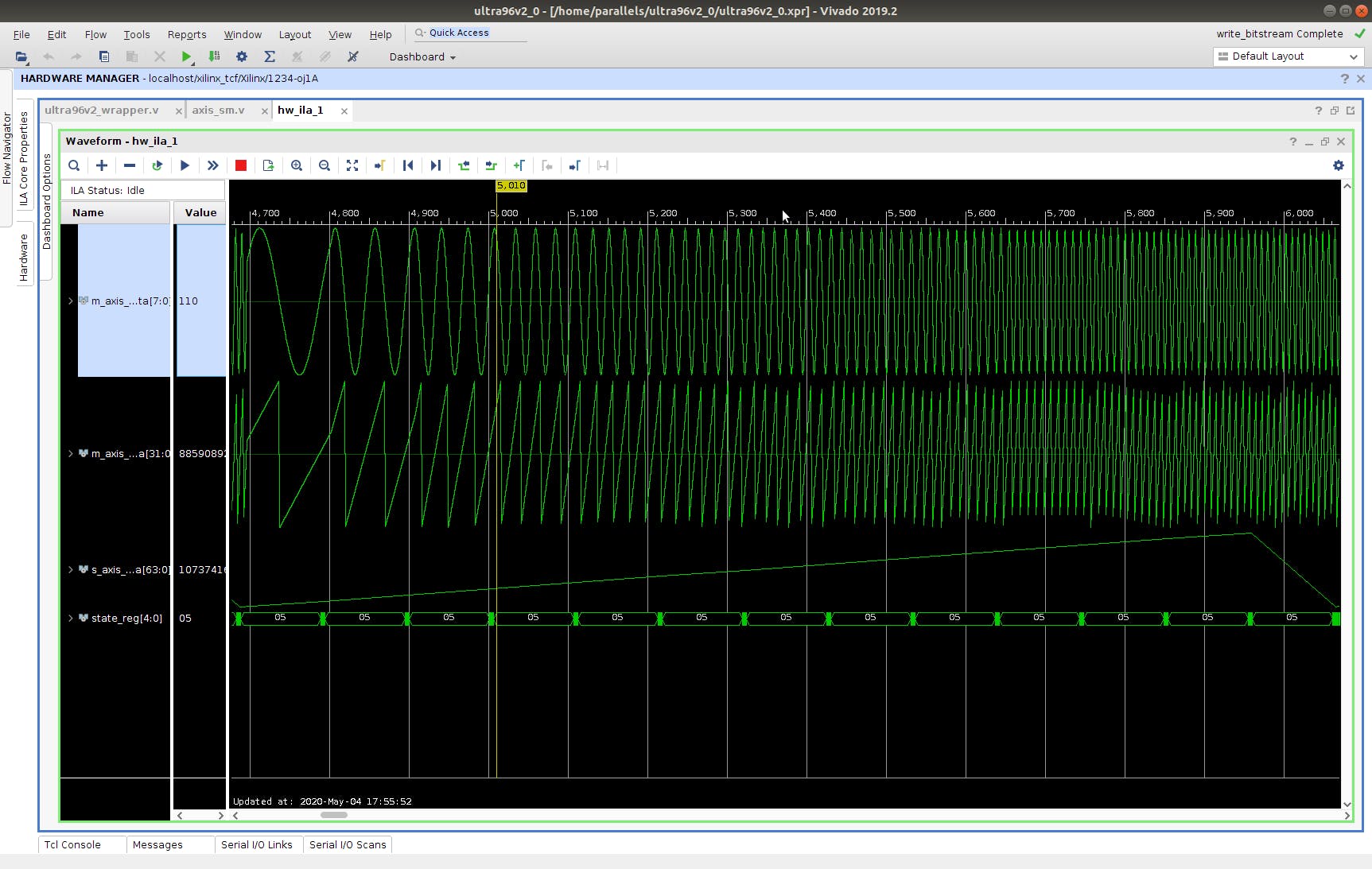

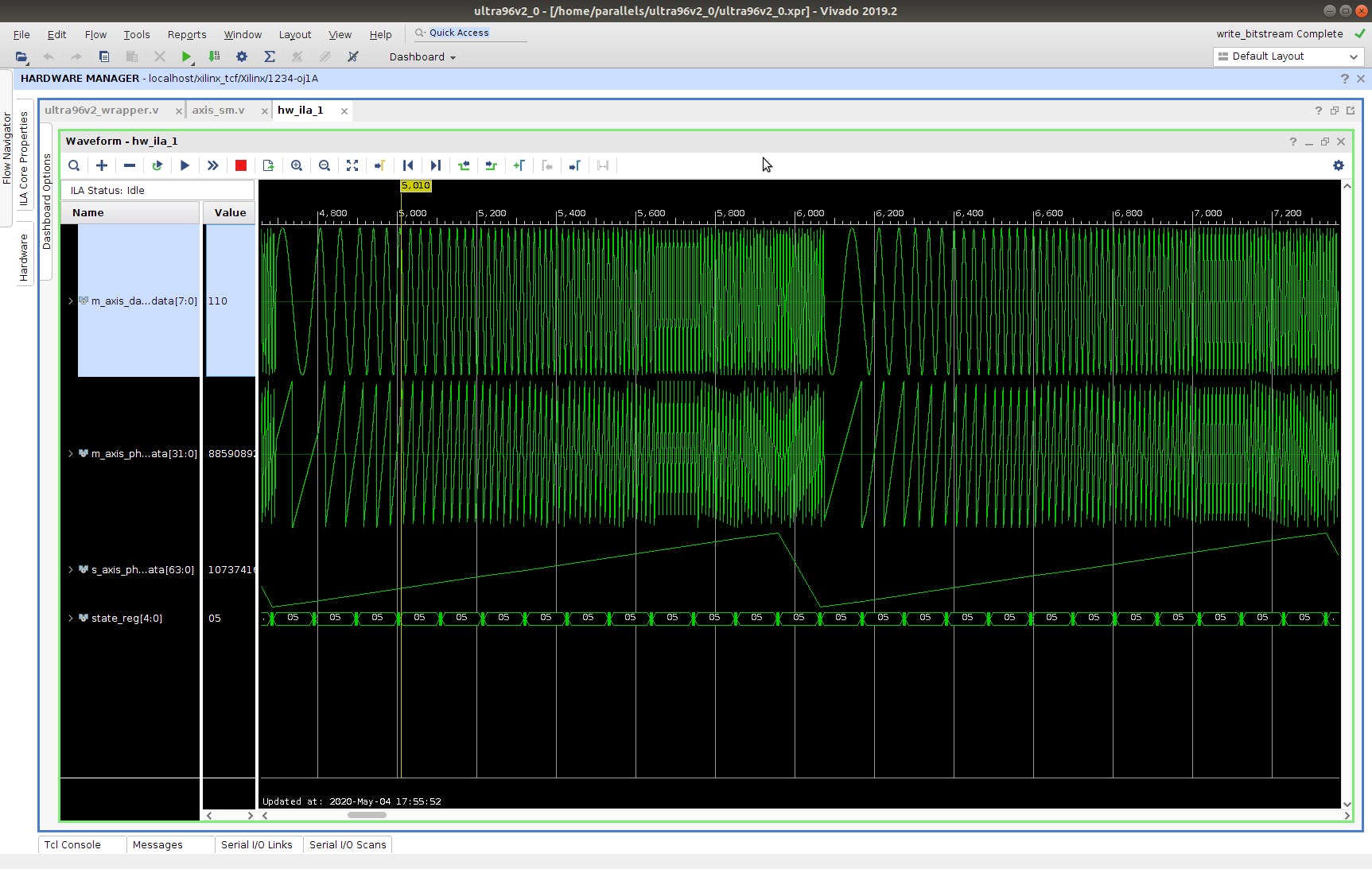

成功闪光后,ILA 窗口将出现,如果您单击即时捕捉按钮(带有 >> 字符的蓝色按钮),您将看到 DDS 不断循环的啁啾声。

ILA 顶部的图是 DDS 编译器输出的实际正弦波形,下图是其瞬时相位值。向下的第三个图是输入到 DDS 编译器的相位增量值。

底部的十六进制值只是状态机状态,用于演示每个状态如何与 DDS 编译器的控制相关。

我希望这个简单的 DDS 编译器示例对您有所帮助。如果您想进一步阅读,我附上了 Xilinx 的 DDS 编译器 (PG141) 产品指南,其中深入解释了其操作理论。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章