资料下载

Wiznet以太网芯片设计指南

描述

介绍

我总结了设计以太网芯片电路时需要注意的点。它基于 Wiznet 的芯片。请仅作为参考。

指数

- 设计检查表

- SCH 设计指南

- PCB设计指南

设计检查表

这是一个检查菜单,可让您在找到错误的确切原因之前进行简单检查。

刚果检查

在设计电路时,设定设计规则,看看是否有任何部分偏离这些规则。也就是说,它是一个可以检查是否存在致命错误的函数。每个设计工具略有不同,但检查是否有 DRC 错误。

_ZqP0S3G4Uh.png?auto=compress%2Cformat&w=740&h=555&fit=max)

去耦电容

适用于所有芯片设计。去耦电容是用来消除电源线的噪声。由于滤波的目的是尽量靠近对应的芯片,也就是线路的末端。通常,从主电源开始,大帽是按照小帽的顺序排列的。换句话说,最好将最小的盖放在芯片上。但是,对于某些芯片,建议检查数据表,因为在主芯片附近会放置一个大帽。

_qMBad1kFyE.png?auto=compress%2Cformat&w=740&h=555&fit=max)

_ncecLJh3Of.png?auto=compress%2Cformat&w=740&h=555&fit=max)

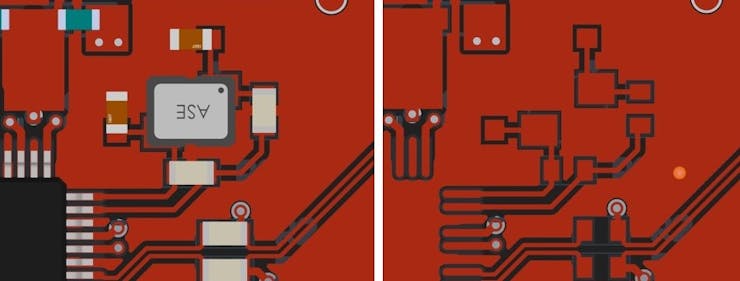

振荡器

建议将振荡器放置在尽可能靠近芯片的位置。

因为是频率很高的时钟,所以建议画一条和芯片同层的线,不要过孔。

建议线路设计的越简单越短。

此外,绝对不可能将两个设备连接到一个振荡器。(电流不足,相互干扰问题)

地平面

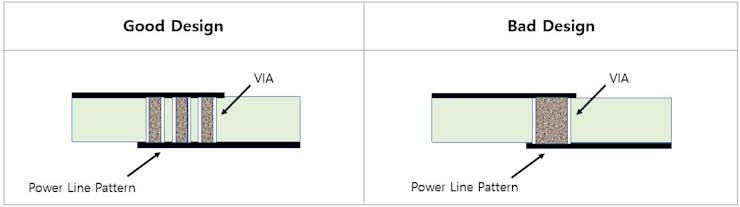

Power Line 还应考虑 Pattern 和 Via 设置。在图案中,电流容量根据铜箔的宽度、厚度(高度:OZ)和温度而变化。

电流容量因 Via 而异,因此建议在设计时考虑到这一点。最好设计几个较小的过孔而不是一个大过孔。

_qJhocIqi7T.png?auto=compress%2Cformat&w=740&h=555&fit=max)

原理图设计指南

电路类型分为以下几类。

- W6100, W5100S, W5300

- W5500

- W7500P

- W7500

W6100、W5100S、W5300原理图设计

_7DFUsWyG1A.png?auto=compress%2Cformat&w=740&h=555&fit=max)

- 如果您使用不包含 Trans 的 RJ45 连接器,则还必须设计 Trans 部分。

- 选项 1 是用于 EMI 保护的阻尼电阻器。在我们的例子中,经常使用 33Ω。

W5500原理图设计

_oYOAiPtGb3.png?auto=compress%2Cformat&w=740&h=555&fit=max)

- 如果您使用不包含 Trans 的 RJ45 连接器,则还必须设计 Trans 部分。

- 选项 1 是用于 EMI 保护的阻尼电阻器。在我们的例子中,经常使用 33Ω。

****** W5500 内部 Rx、Tx PHY 以不同模式驱动。因此,改变了TCT/RCT的设计。

让我们看看下面的电路

_IPuQAiDP78.png?auto=compress%2Cformat&w=740&h=555&fit=max)

一般的 PHY 芯片具有与 Rx 和 Tx 相同的 UTP 端口电平。PHY有两种模式,Voltage Mode和Current Mode,根据PHY Chip数据中存储的UTP端口电平来决定。

与常规芯片不同,W5500 具有不同的 Rx 和 Tx 端口级别。Rx 侧以电流模式驱动,Tx 侧以电压模式驱动。

在电流模式下,CT 应通过电容连接到 GND,在电压模式下,电源应连接到 CT。

如果您查看上面的以太网插座,就会发现 RCT 和 TCT 是捆绑在一起的。因此,如果电压施加到电流模式 RCT,则需要用适当的电容器将 Rx 和 Tx 线绝缘以防止旁路。

换句话说,只有当电路配置了W5500、TCT、RCT捆绑在一起的RJ-45 Socket时,才需要在Rx Line上加一个Capacitor。

W7500P原理图设计

_dBq9vG4ynj.png?auto=compress%2Cformat&w=740&h=555&fit=max)

- 如果您使用不包含 Trans 的 RJ45 连接器,则还必须设计 Trans 部分。

- 选项 1 是用于 EMI 保护的阻尼电阻器。在我们的例子中,经常使用 33Ω。

W7500原理图设计

- PHY Chip需要另外设计,设计部分参考PHY Chip厂商的Doc。

[附加]变压器与RJ-45分离时的电路(如果使用带变压器的RJ-45插座,适用X)

_KOdU8bKEeX.png?auto=compress%2Cformat&w=740&h=555&fit=max)

- A 和 B 部分应尽可能靠近变压器级放置。

- 变压器与 RJ-45 插座之间的距离应尽可能近。

- 建议距离小于 25mm (1000mil)。

PCB设计指南

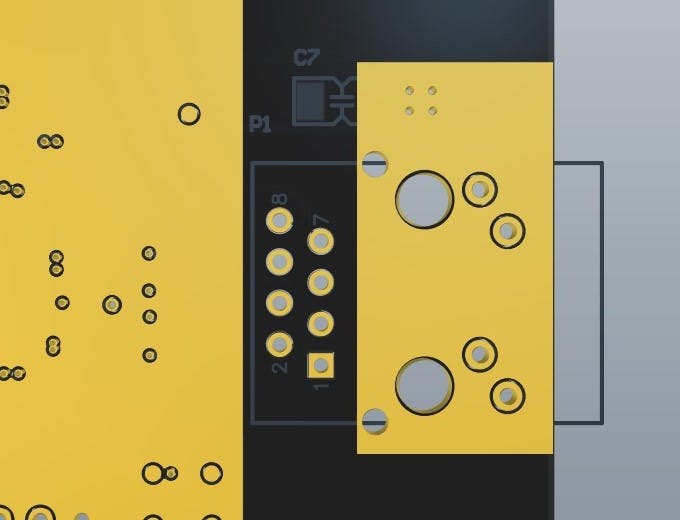

以太网插座部分

Socket分为Socket combined with Trans和Socket separated。分为这两类,但请注意,根据变压器设计,电路可能略有不同。总的来说,Socket结合Trans使用的比较多。

_NEGH8iqZrL.png?auto=compress%2Cformat&w=740&h=555&fit=max)

- 像上面的PCB一样,不把Power和GND Plane放在Ethernet Socket下面的层里,也能起到很好的绝缘作用。

- 如果设计与 Trans 分离,则 Trans 也可以绝缘,而无需将 Power 和 GND Plane 放在下层。

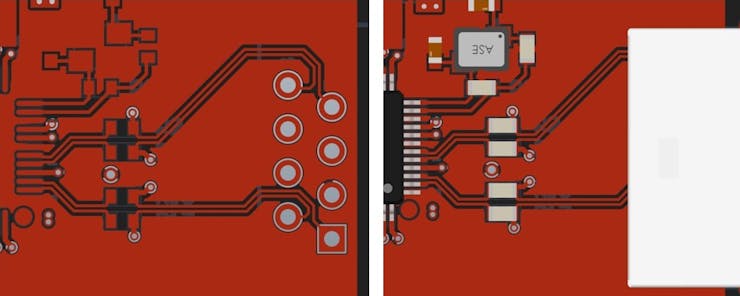

MDI数字线

_LDlw0pSjZw.png?auto=compress%2Cformat&w=740&h=555&fit=max)

_vJKguf05yT.png?auto=compress%2Cformat&w=740&h=555&fit=max)

- TX 和 RX 线越短越好。

- 为了屏蔽,最好在 TX 和 RX 对之间制作一个 GND 平面。

- PHY 和 RJ45 连接器之间不应有数字信号路由。

- TX 和 RX 信号附近不能有高频设备和线路。

- 尽可能调整TX和RX线的长度是好的。

- TX+/- 和 RX+/- 信号的独立阻抗应保持在 50 欧姆以下,+/- 差分信号的阻抗应保持在 100 欧姆。

- 建议信号长度小于25mm(1000mil),无论多长都不应超过75mm(3000mil)。

- TX+/- 和 RX+/- 的走线应该以 45 度或曲线连接。

- TX+/- 和 RX+/- 信号不适用于 Via 或 Layer 更改。

_LXkm6JkQvQ.png?auto=compress%2Cformat&w=740&h=555&fit=max)

_6im2FYh7Wk.png?auto=compress%2Cformat&w=740&h=555&fit=max)

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章