资料下载

SP701上的lwIP入门

描述

在我上一篇项目博文中,我介绍了如何在 Vivado 2021.2 中为基于 SP701 Spartan-7 的开发 FPGA 板创建基础硬件设计。该项目是涵盖如何使用 Xilinx 的嵌入式软件 IDE Vitis 在嵌入式 C 语言中创建轻量级 IP (lwIP) 回显服务器以在 SP701 上运行的项目的延续。

如果您还不熟悉,Vitis 及其前身 Xilinx SDK 都有一个模板 lwIP 回显服务器项目,可以用作起点并根据用户的特定应用需求进行定制。我发现它作为为我的 FPGA 设计建立网络通信的基准非常方便,并且节省了大量时间,所以我不会在每次需要通过以太网连接控制我的 FPGA 时重新发明轮子。

作为高级概述,我将使用 lwIP 回显服务器项目模板创建一个新的应用程序项目,将 SP701 连接到我的本地网络,直接连接到我的路由器,然后使用套接字在我的主机 PC 上创建一个简单的 Python3 脚本来发送一些向 SP701 上的服务器测试数据包,看它们是否成功回显。

启动 Vitis

Vitis 可以直接从 Vivado 启动,也可以从命令行独立启动。

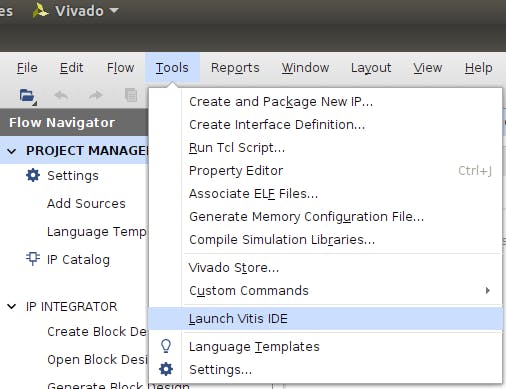

要从 Vivado 启动,请选择Tools > Launch Vitis IDE (这可以在 Vivado 中打开或不打开项目的情况下完成):

要从命令行启动,首先获取环境然后运行 Vitis:

~$ source /tools/Xilinx/Vitis/2021.2/settings64.sh

~$ vitis

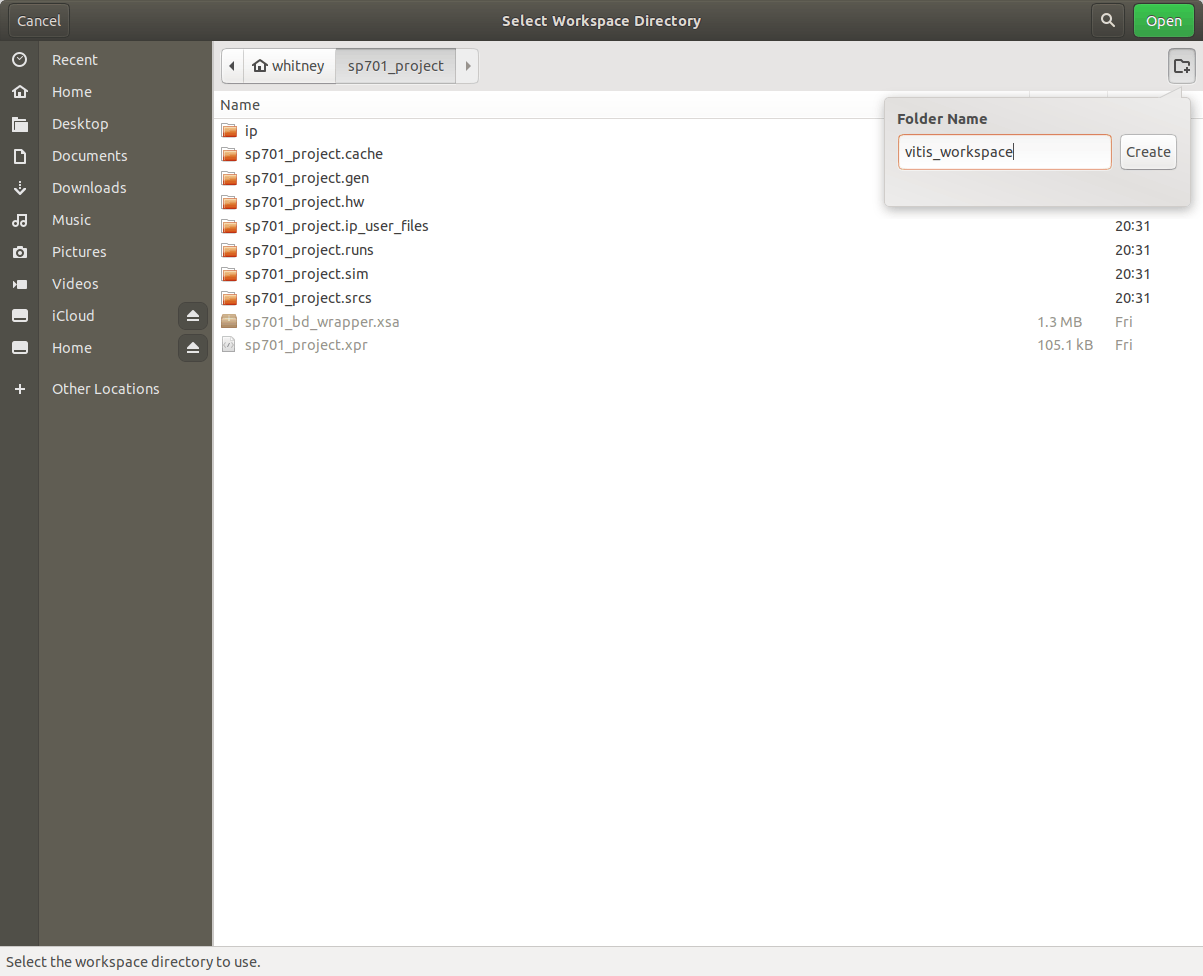

为这个 Vitis 实例的工作区选择一个目录,我个人喜欢在 Vivado 项目的顶层创建一个文件夹,我在 Vitis 工作区中创建软件中的硬件将基于该项目。这只是我保持一切井井有条的方式。

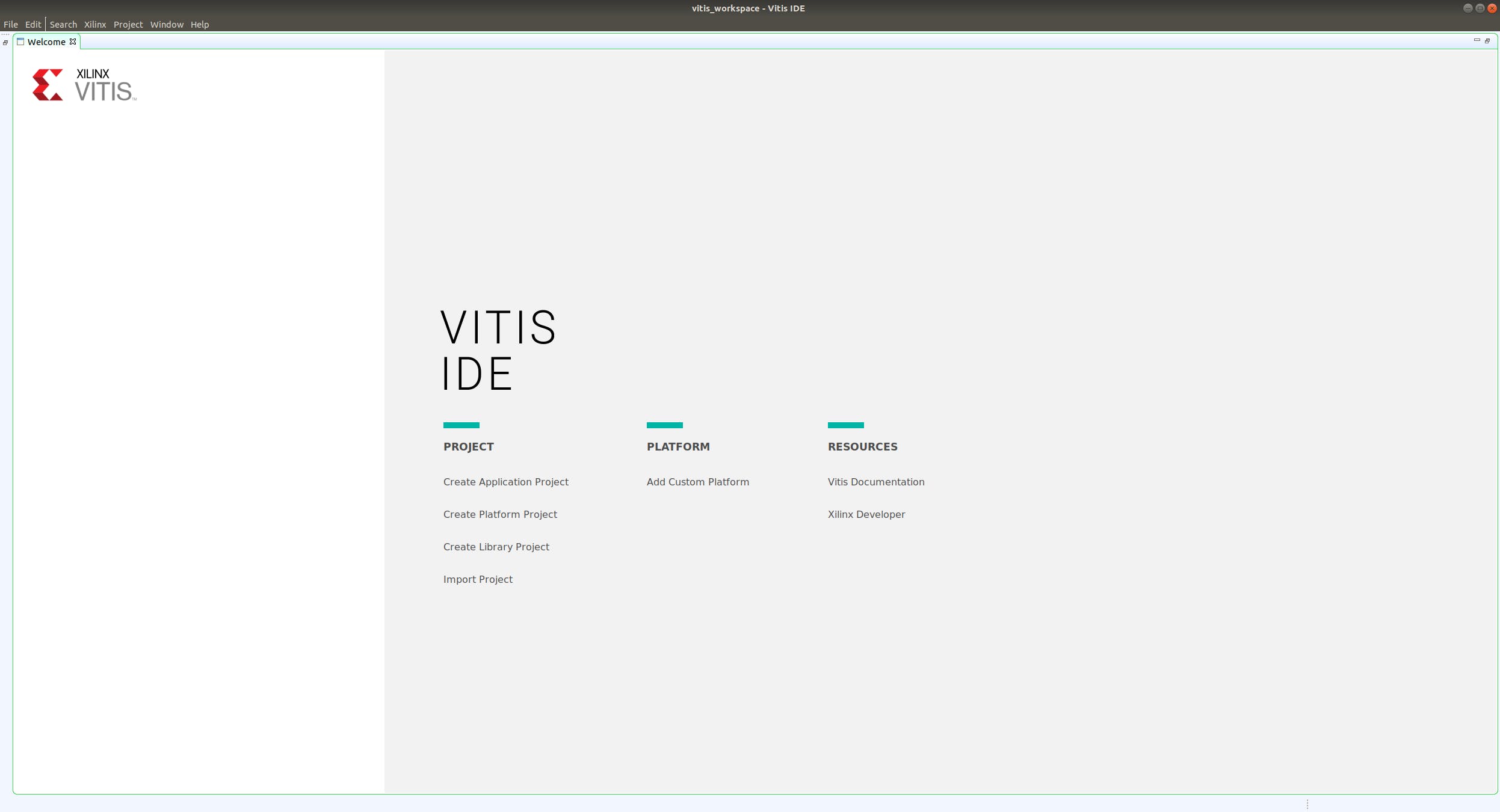

Vitis 最初将启动到一个完全空白的工作区。与它的前身 Xilinx SDK 不同,它会自动从 Vivado 中提取导出的硬件平台。

整个项目流程可以分解为以下步骤:

- 使用从 Vivado 导出的硬件平台设计为目标创建一个平台项目。

- 创建一个应用程序项目,其中包含要在目标硬件的处理系统上运行的实际 C 代码。

- 使用硬件上的系统调试器等调试器调试应用程序。

- 对目标设备的闪存进行编程。

我将介绍该项目的前三个步骤。

平台项目

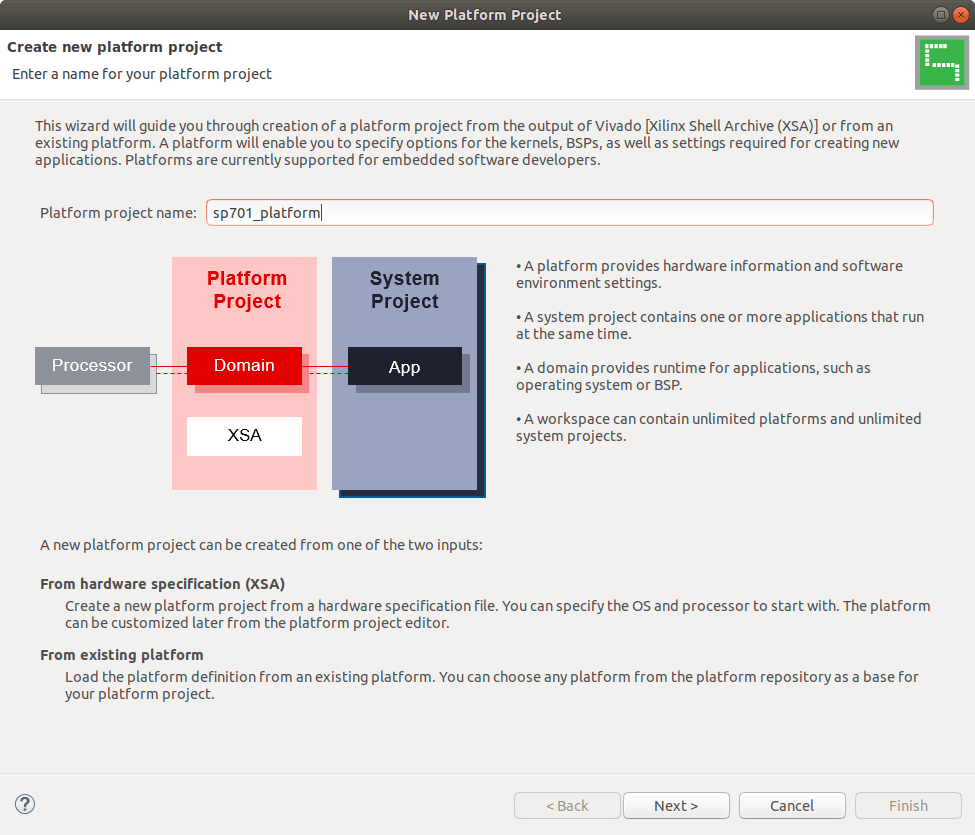

通过从空白工作区窗口中选择创建平台项目,基于从 Vivado 导出的硬件平台(带比特流)创建新的平台项目。

弹出窗口将指导您完成用于命名平台项目的参数选择,并指向为目标板(.xsa 文件)导出的硬件平台所在的位置。

由于这是一个未使用 Linux 或 RTOS 等操作系统的裸机应用程序,因此Operating system设置为standalone 。

目标处理器是 Vivado 模块设计microblaze_0中 MicroBlaze 处理器的实例化。

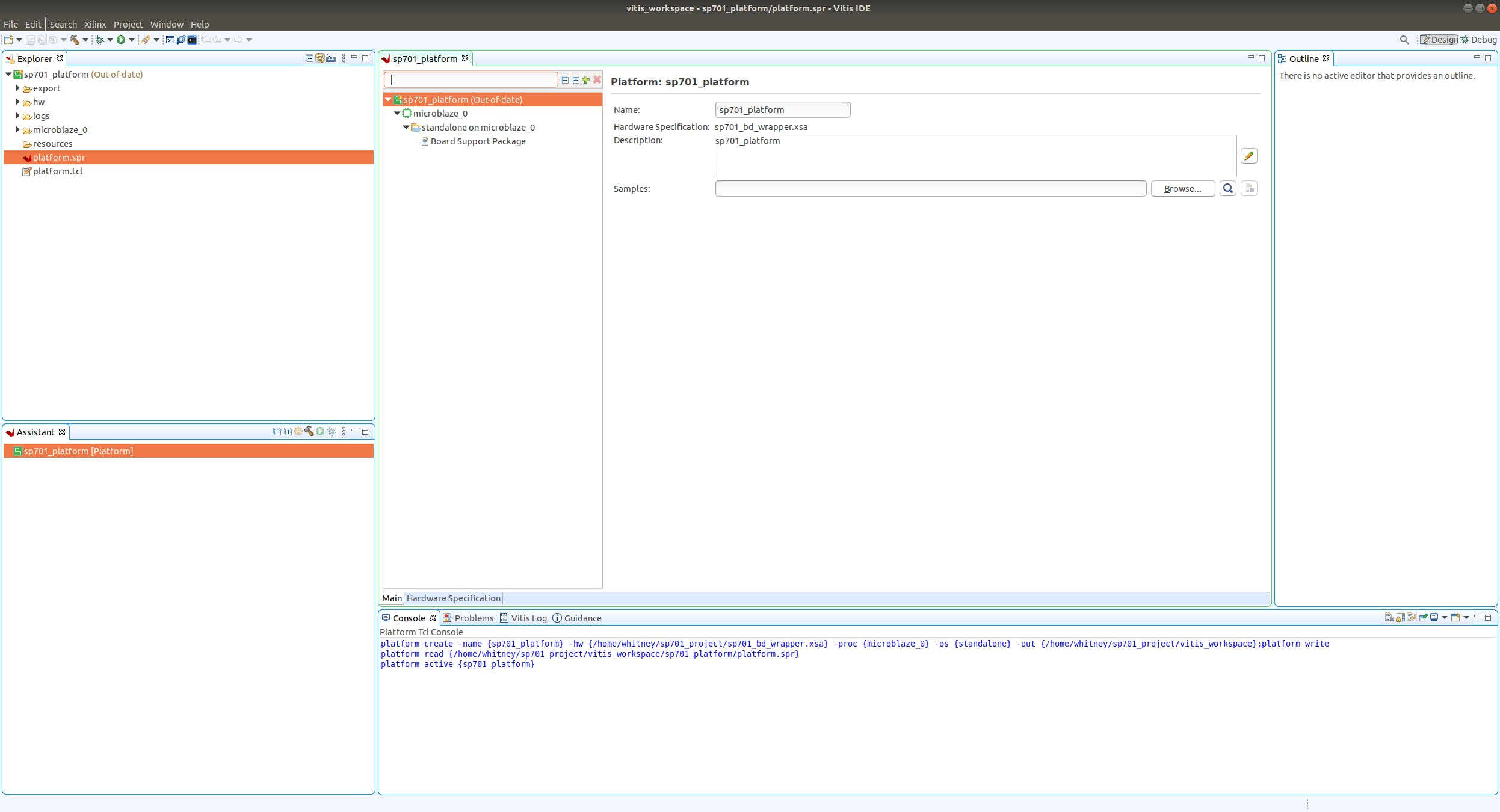

单击 Finish,Vitis 将在空白工作区中生成平台项目。

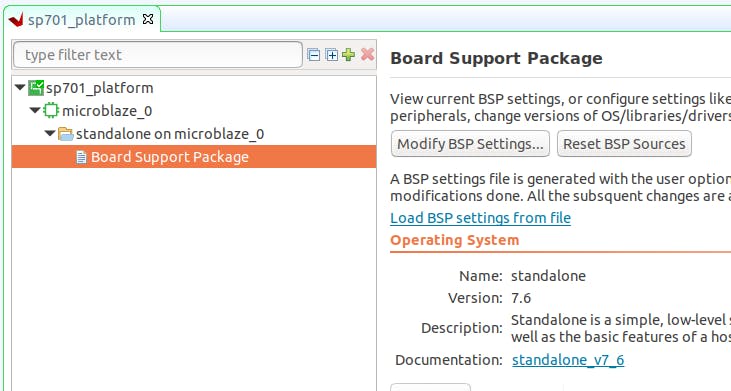

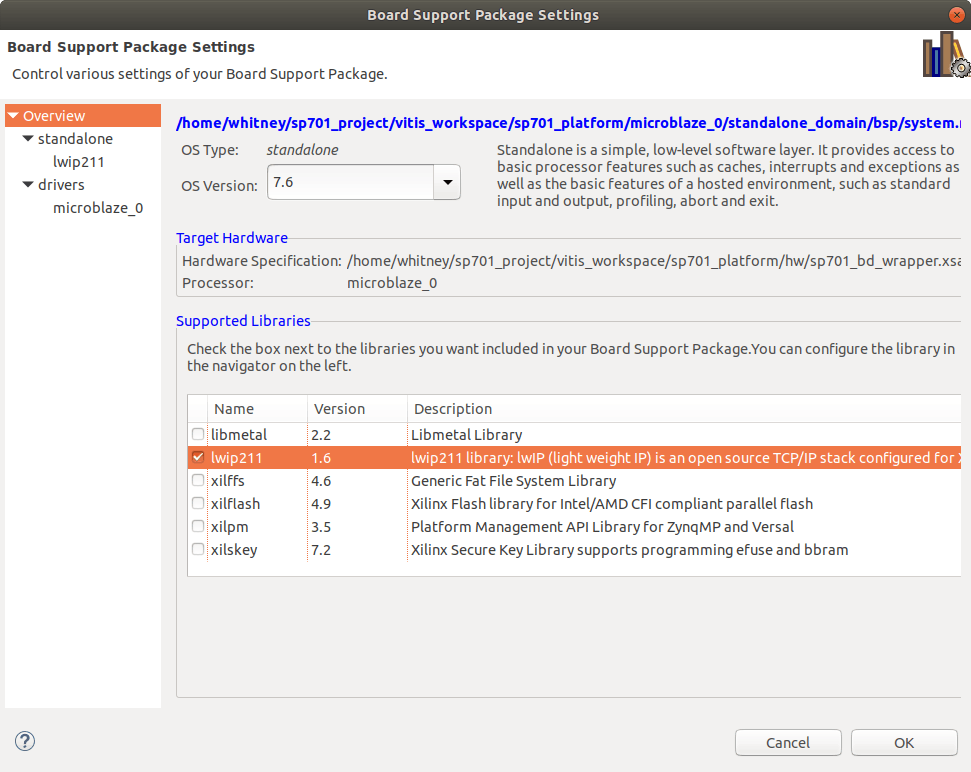

在这个特定实例中创建应用程序项目之前,需要修改平台项目中生成的 BSP 以包含 lwIP 库,因为在新平台项目中默认情况下未启用该特定库

要修改 BSP 以添加 lwIP 库,请选择修改 BSP 设置...

然后在弹出窗口中,选中启用lwip211的复选框并单击OK 。

请注意,平台项目显示为已过期。这是因为此时尚未构建平台项目,因此不存在输出文件。运行平台项目的初始构建,这样它就不会再使用菜单栏中的构建图标或按 ctrl+B 显示为过时。

应用项目

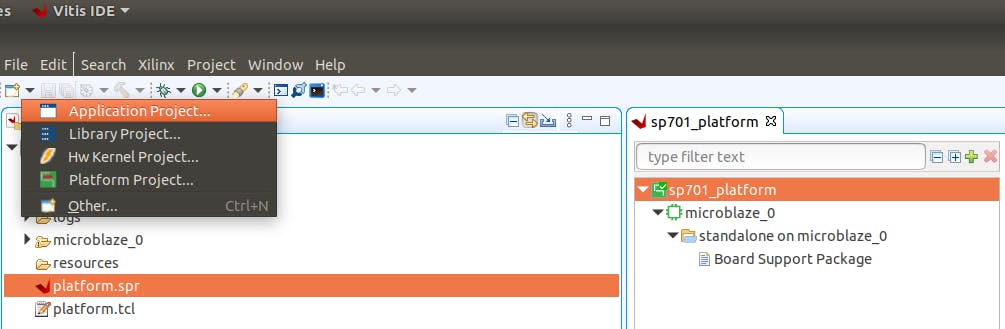

配置和构建平台项目后,基于它创建一个新的应用程序项目。选择新建>应用程序项目...

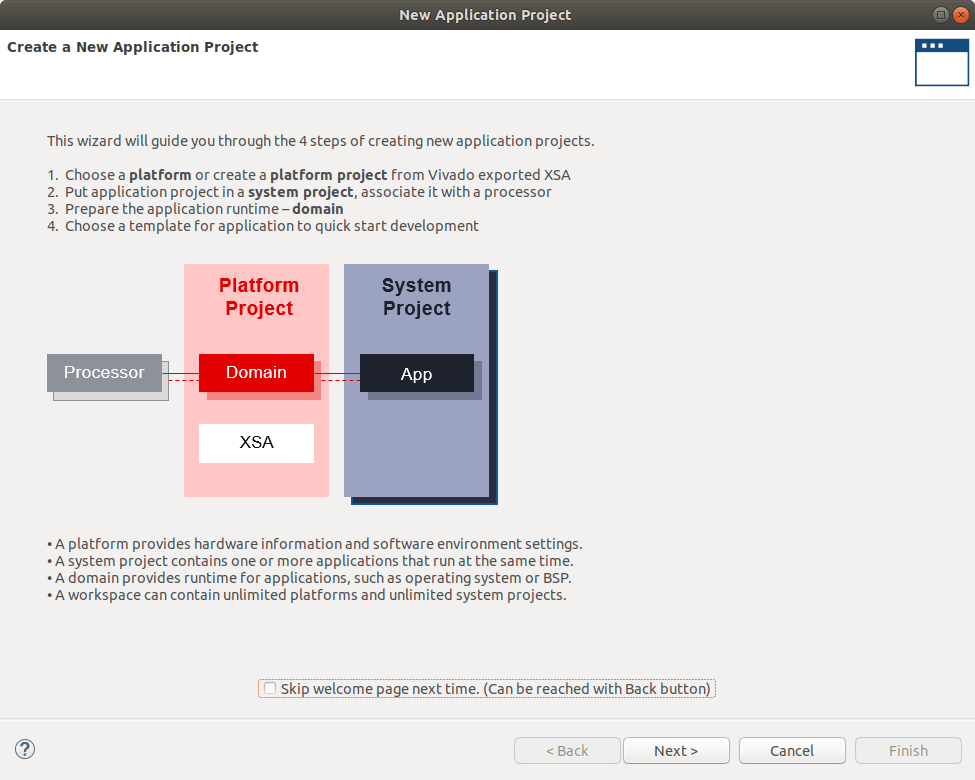

在弹出窗口中,您可以跳过第一张幻灯片(它是我们生成应用程序项目的步骤大纲)。选择上一步中创建的平台项目作为应用程序的基础,然后单击Next 。

根据需要命名应用项目,Vitis 将自动为其生成系统项目并将其与 MicroBlaze 软处理器相关联(假定它是唯一可运行的目标)。单击下一步。

同样,由于没有操作系统,域将是standalone 。在 Vitis 中创建新应用项目的最后一步是选择一个项目模板,以完成初始启动中的一些基础工作。正如我之前提到的,这个项目正在使用 lwIP 回显服务器应用程序模板。选择它并单击完成。

注意:如果您忘记修改 BSP 以启用 lwip211 库,Finish 按钮将变灰,并且窗口顶部会出现一条警告消息,告诉您库丢失。

同样,Vitis 将为设计生成应用程序项目和基础代码。

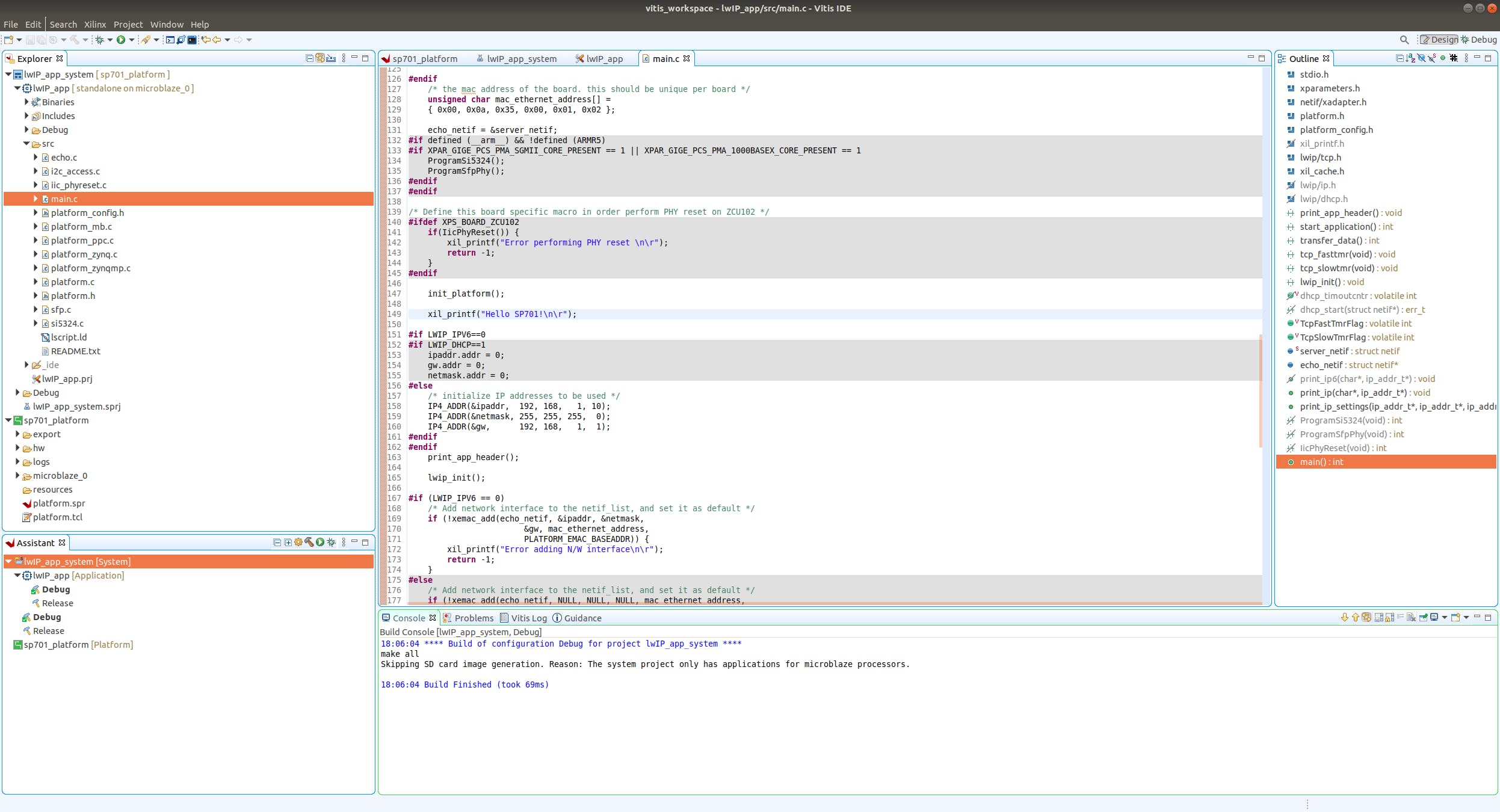

默认代码有很好的注释,所以请随意打开/src/main.c阅读它并添加任何所需的自定义代码。

为应用程序项目运行构建。

应用调试

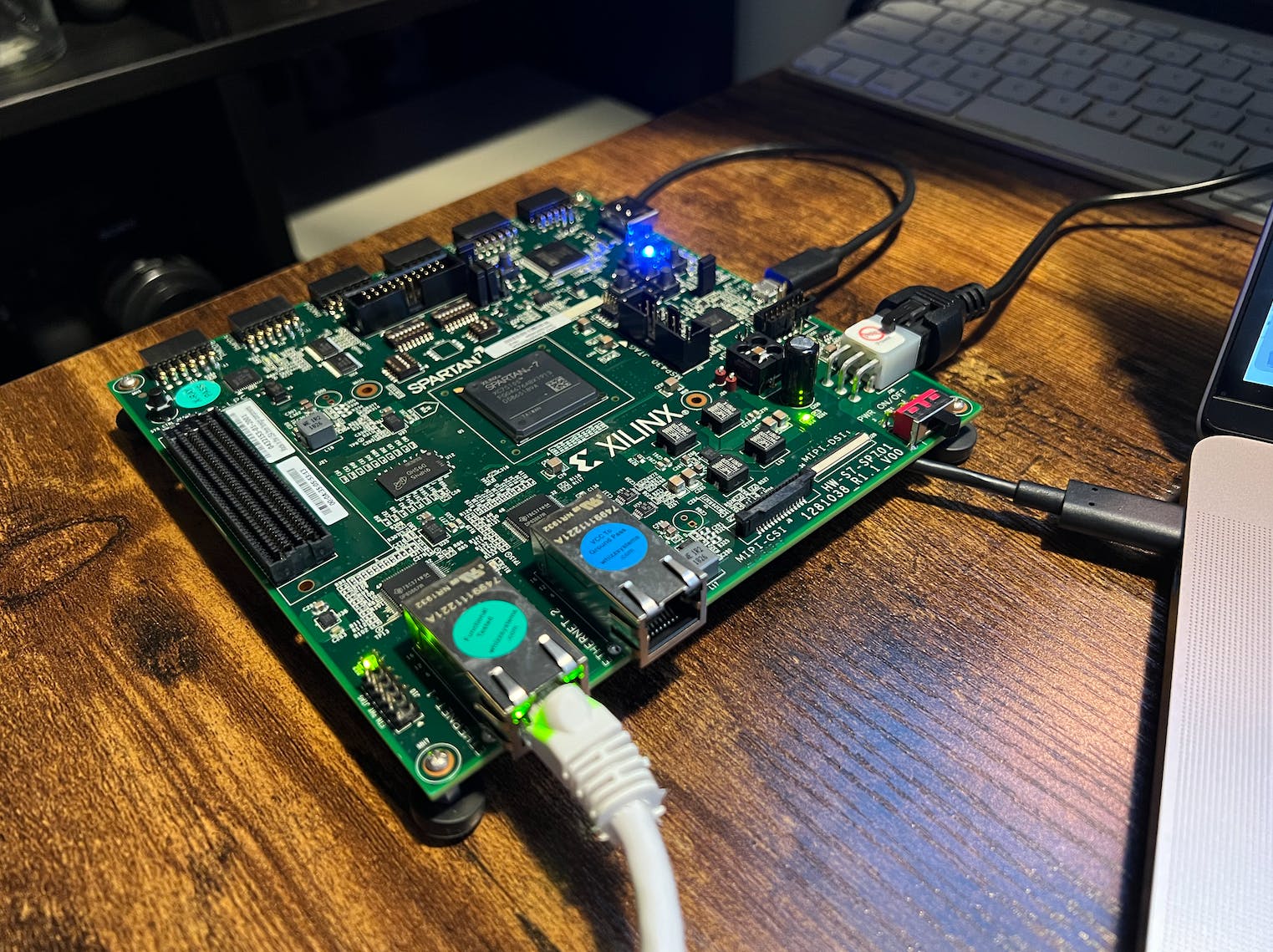

通过使用以太网电缆将 SP701 开发板连接到您的路由器来设置 SP701 开发板,将 USB 连接到 UART 端口 J5 到您的主机 PC,然后插入墙上适配器为 SP701 板供电。通过将 SW11 设置为 ON 位置来打开电路板。

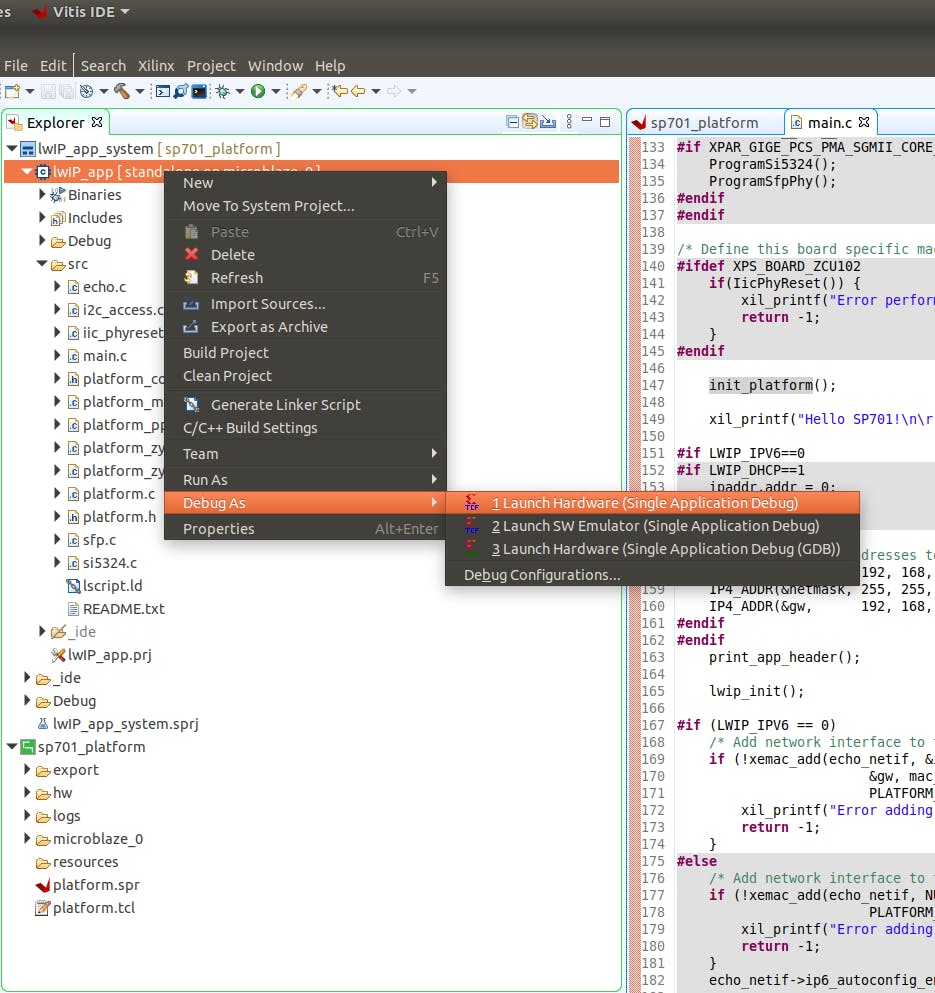

通过在资源管理器窗口中右键单击应用程序名称,然后选择Debug As > Launch Hardware (Single Application Debug) ,在 Vitis 中启动 lwIP 服务器应用程序的调试运行。

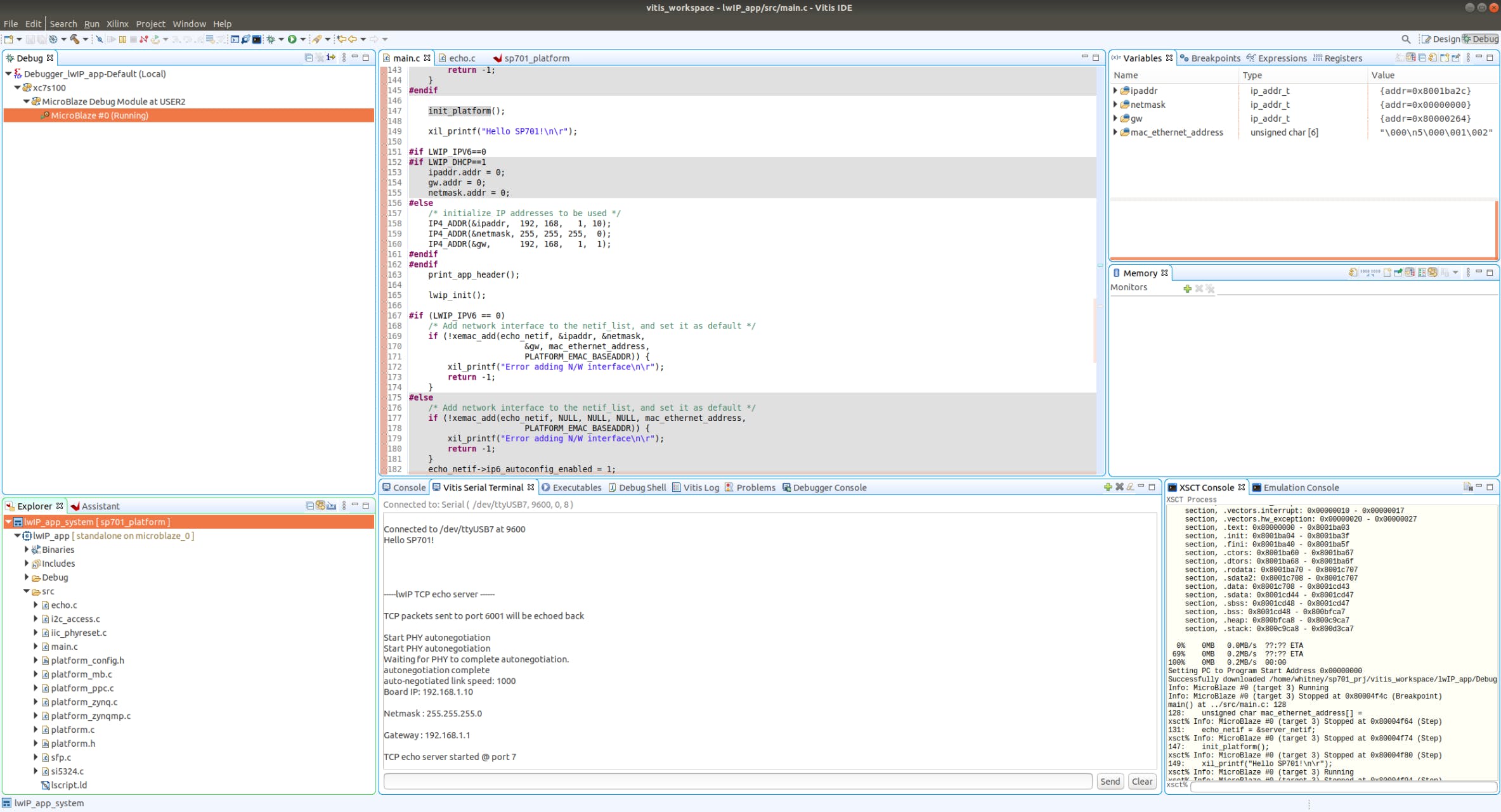

然后,Vitis 将从开发视图切换到调试视图,将比特流编程到 FPGA 上,启动 MicroBlaze,然后设置断点,使其在进入 lwIP 应用程序的主要功能后立即停止。

此时,您可以像在任何其他调试器中一样选择逐步执行/结束/退出,或者您可以单击运行/恢复/F8 (所有这些都位于菜单栏中)让应用程序正常运行随时暂停和单步执行的选项。

您还需要连接到 SP701 的 UART 串行输出。您可以使用您选择的任何串行终端应用程序执行此操作,或使用 Vitis 中的内置终端应用程序。调试视图底部有一组选项卡,包括Console 、Vitis Serial Terminal 、Executables 、Debug Shell 、Vitis Log 、Problems和Debugger Console 。

切换到Vitis 串行终端选项卡并点击+按钮。将有三个枚举串口,选择三个中的第一个(例如,如果有 ttyUSB0、ttyUSB1 和 ttyUSB2,则选择 ttyUSB0)。并以 9600 的波特率和默认 UART 设置连接到它。

现在单击运行将启动回显服务器侦听它在端口号 7 上建立的端口,如 UART 接口上的串行输出所证明的那样。这将告诉您 SP701 板的本地 IP 和链接状态。

主机 PC 回显客户端

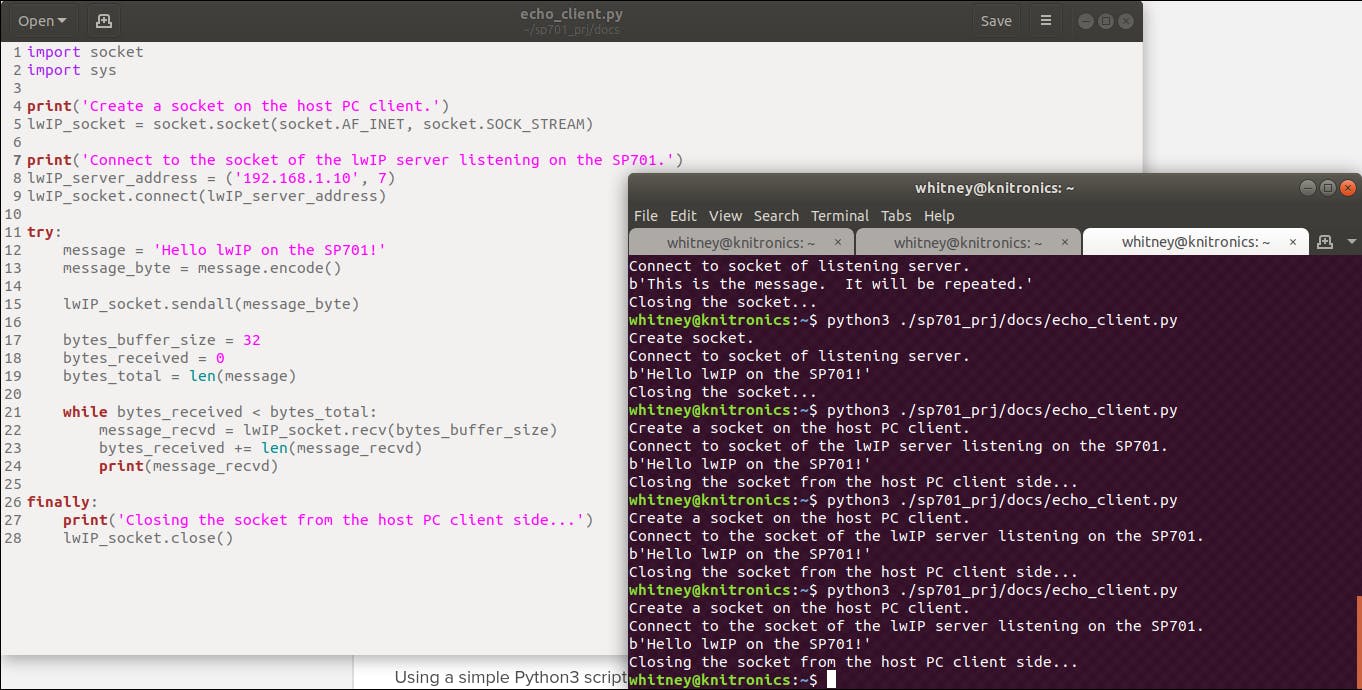

为了测试 SP701 上的 lwIP 回显服务器,我在 Python3 中拼凑了一个简单的回显客户端脚本,我从与 SP701 位于同一本地网络的 PC 上运行该脚本。

该脚本在 SP701 的本地 IP(默认为 192.168.1.10)的端口 7 上作为客户端打开一个套接字,然后将一个字节数据包发送到回显服务器。

发送数据包后,回显服务器会等待,直到收到与发送出去的字节数相同的返回字节,然后打印出接收到的数据包。一旦接收到预期的字节数,echo 客户端就会关闭套接字。关闭套接字很重要,因为如果您不这样做并尝试再次运行脚本,它将挂起,因为套接字资源从未被释放。

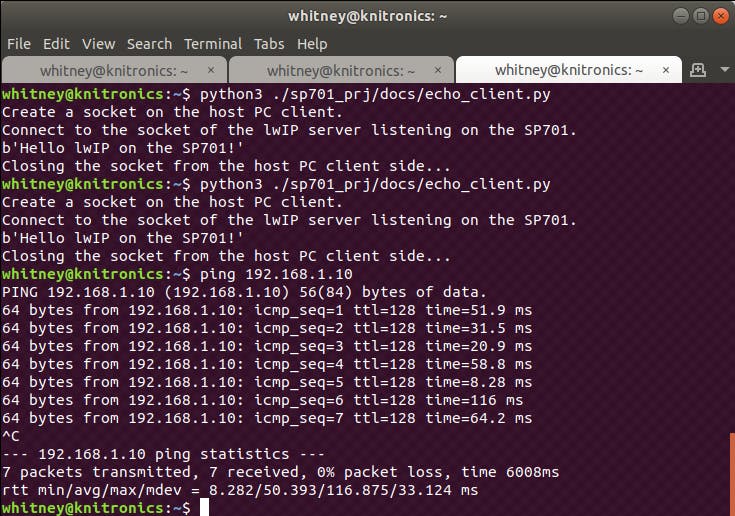

作为对连接的进一步测试,您还可以从 PC 的命令行 ping SP701:

我认为这将是启动和运行 lwIP 的一个很好的停止点(我试图将我的项目帖子保持在易于消耗的长度)。在未来的项目中,我将通过在回显服务器中添加自定义函数来对此进行扩展,因此请保留此书签。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章