层次化的UVM TLM连接

描述

封装和层次结构

TLM接口的使用将验证环境中的每个组件与其他组件隔离。验证环境实例化一个组件,并完成其ports/exports的连接,不需要进一步了解验证组件具体的实现。

较小的验证组件可以组合成较大的验证组件,此时上一级组件就是一个简单的引出包含多个子组件的容器。

层次化连接

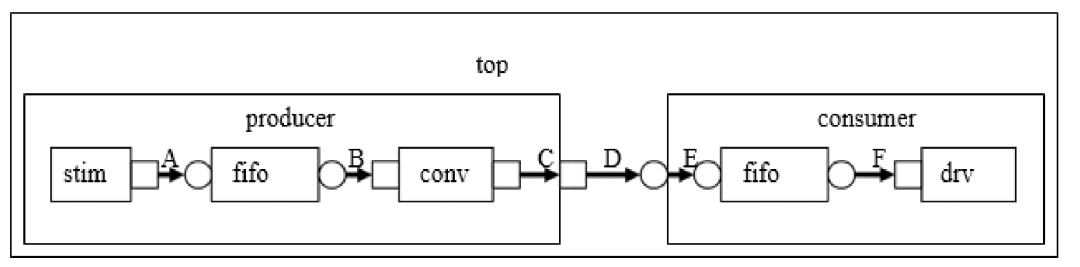

建立跨层次连接涉及到一些额外的问题,考虑下图所示的分层设计。

这个设计的层次包含两个组件,producer和consumer。producer包含三个组件,stim、fifo和conv。consumer包含两个组件,fifo和drv。这两个fifo都是uvm_tlm_fifo 组件的例化。

从顶层角度看,producer的put_port与consumer的put_export相连。在上图中,A、B、D和F是标准的 peer-to-peer连接。连接A的代码为:

stim.put_port.connect(fifo.put_export);

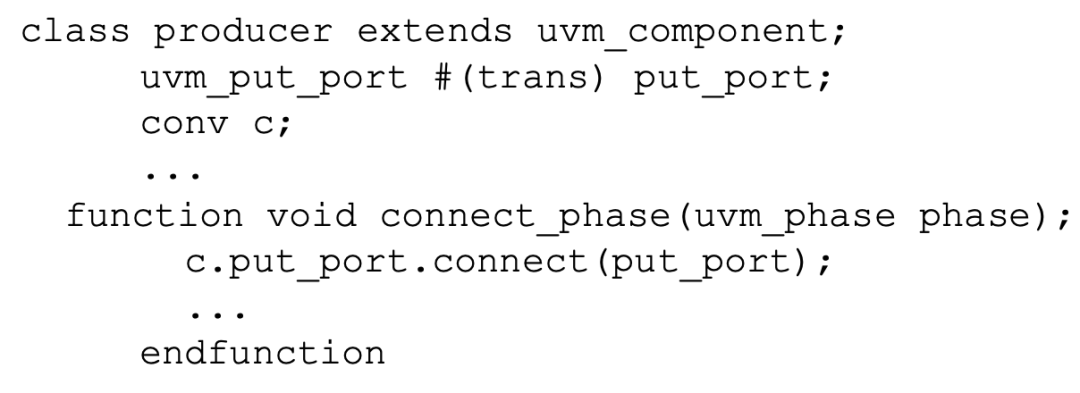

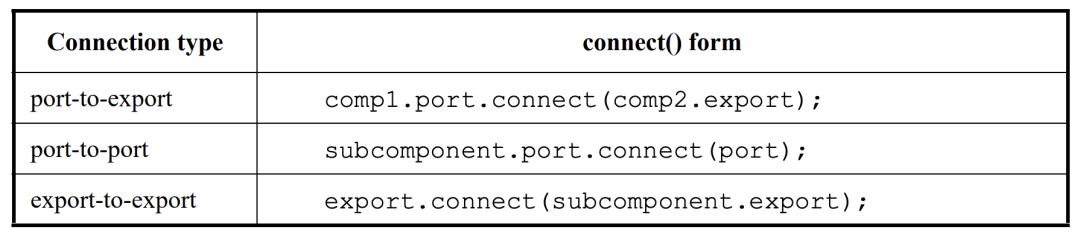

连接C和E有所不同,C是port-to-port的连接,E是export-to-export的连接。这两种连接对于完成层次化连接是必要的。

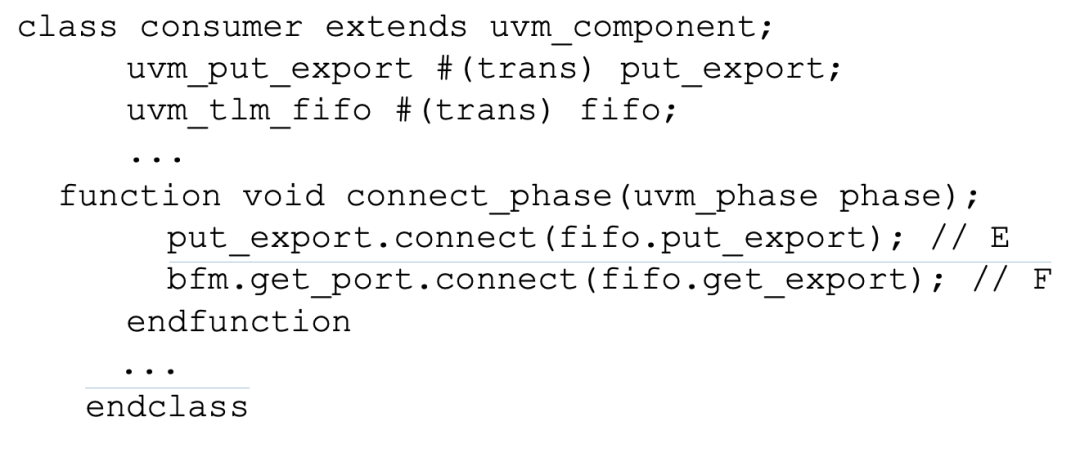

连接E的代码为:

连接C代码为

连接类型

port.connect()方法的参数可以是一个export和port,这取决于连接的性质(即peer-to-peer或者hierarchical)。

export.connect()的参数总是一个子组件的export。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

一文详解UVM设计模式2023-08-06 4888

-

UVM中基于SOCKET通信的TLM2.0介绍2023-06-25 4373

-

Easier UVM Code Generator Part 4:生成层次化的验证环境2023-06-06 2399

-

创建UVM Driver2023-05-30 1545

-

UVM Transaction-Level验证组件2023-05-29 1542

-

UVM TLM的基本概念介绍2023-05-24 3149

-

典型的UVM Testbench架构2023-05-22 3566

-

谈谈UVM中的uvm_info打印2023-03-17 2529

-

ASIC芯片设计之UVM验证2022-11-30 2397

-

请问一下在UVM中的UVMsequences是什么意思啊2022-04-11 5553

-

什么是uvm?uvm的特点有哪些呢2022-02-14 1880

-

数字IC验证之“什么是UVM”“UVM的特点”“UVM提供哪些资源”(2)连载中...2021-01-21 4384

-

集成级的UVM寄存器模型2017-09-15 1011

-

关于层次化符号的管脚的一个疑问2014-03-08 6232

全部0条评论

快来发表一下你的评论吧 !