TSV工艺及设备技术

描述

由于摩尔定律逐渐接近其物理极限,为进一步追求速度、功耗、功能与制造成本的平衡,后道封装更加强调封装集成度、I/O引脚密度及功能集成度,因此SiP、2.52D/3D集成及WLP成为未来集成电路后道封装工艺的发展重点。 当前最主要的封装形式仍然为倒装键合和引线键合,先进封装(包括2.5D集成、Fan-out WLP/PLP等)已经进入市场并占据一定市场份额,3D集成是当前技术研究热点。2018年底,英特尔发布了首个商用3D集成技术:FOVEROS混合封装。

传统的集成电路后道工艺设备主要包括:划切设备、减薄设备、键合设备、测试分选设备等。SiP、2.5D/3D集成、WLP等先进封装技术大量采用了前道工艺中的光刻、刻蚀、金属化、平坦化等工艺设备,集成电路前后道工艺呈现融合发展的态势。集成电路后道工艺设备的发展需要满足未来SiP、2.5D/3D集成、WLP等先进封装技术发展的需求。

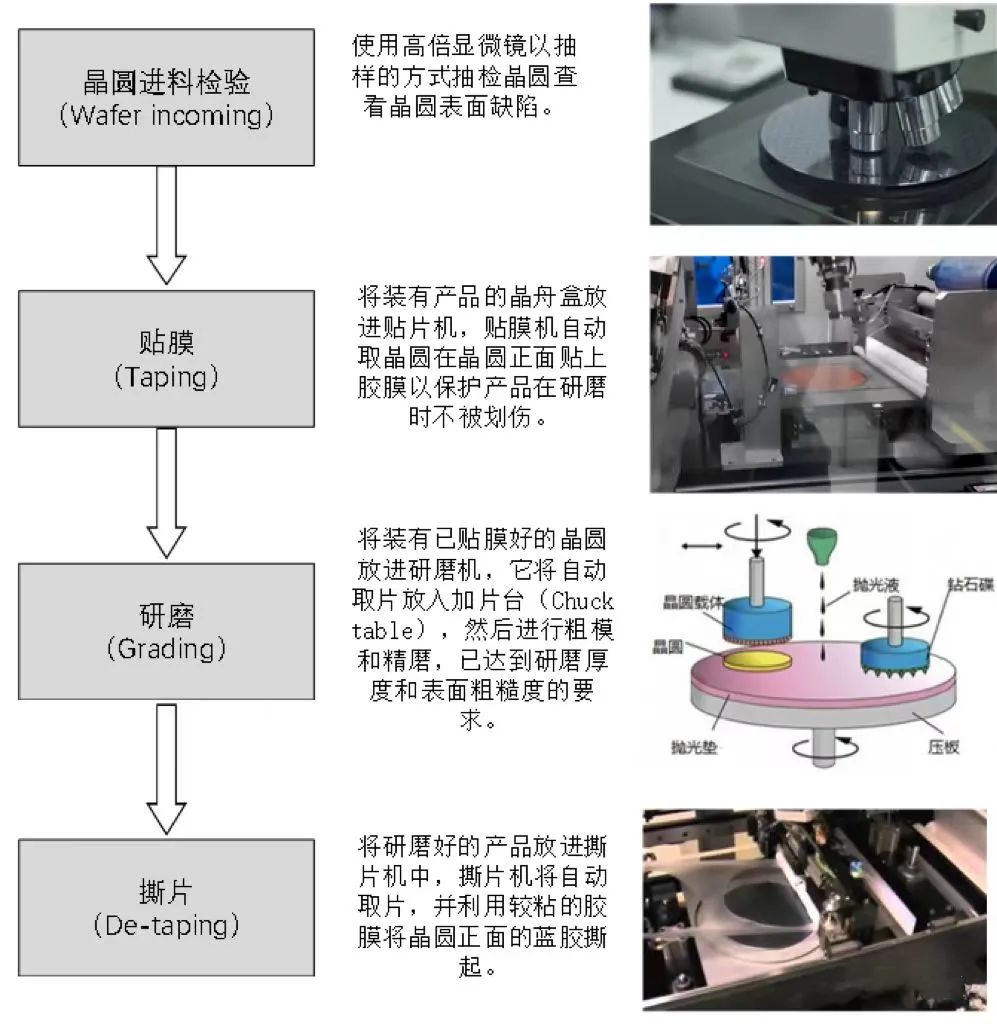

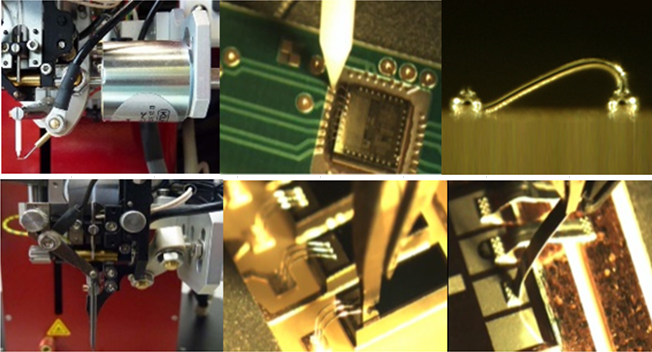

主要技术挑战 (1)超薄晶圆减薄及划切设备。代工厂出厂的硅晶圆厚度一般为0.7~0.8 mm,为保证芯片小尺寸封装的要求,硅晶圆在封装中一般需要通过背面研磨/抛光过程进行减薄。当前大生产中引线键合芯片的减薄工艺可达30 μm,倒装芯片的减薄工艺一般在50 μm左右,晶圆减薄设备已经相对成熟,可以支持直到2030年的减薄工艺需求。  超薄晶圆划切可能导致芯片的卷曲和碎裂,传统的机械划切和激光划切在划切质量和成本等方面都面临着极大的挑战。一种新兴的等离子体划切技术近年来逐渐受到关注:等离子体划切技术与干法刻蚀技术相近,利用等离子体物理轰击和化学反应在硅片表面形成深而细的沟槽,从而达到分割芯片的目的。相对于传统划切技术,等离子体划切具有三大优点:一是芯片侧壁无损伤,没有应力导致的芯片弯曲;二是可以实现多条线的批量划切,减少工艺时间;三是划切通道窄,减少材料损失。 (2)引线键合设备。目前,引线键合仍然是主流的芯片互联方式,占全部封装市场的77%左右,其中用于系统级封装的引线键合市场增长迅速。当前引线键合工艺及设备的发展趋势主要包括四个方面:一是降低成本(主要通过引线材料的变革,由Au线逐渐变更为Ag、Cu线);二是提高产能(近年来,除提升键合机定位平台电机速度外,键合工艺的优化在提升键合设备产能中发挥的作用越来越重要);三是互联密度更大(主要通过新的封装结构和工艺实现);四是采用智能引线键合机(智能引线键合机将实现精确的工艺控制、缺陷检测和可追溯性,从而缩短封装产品的研发时间、提高良率和产能,是未来先进引线键合技术发展的主要驱动力之一)。

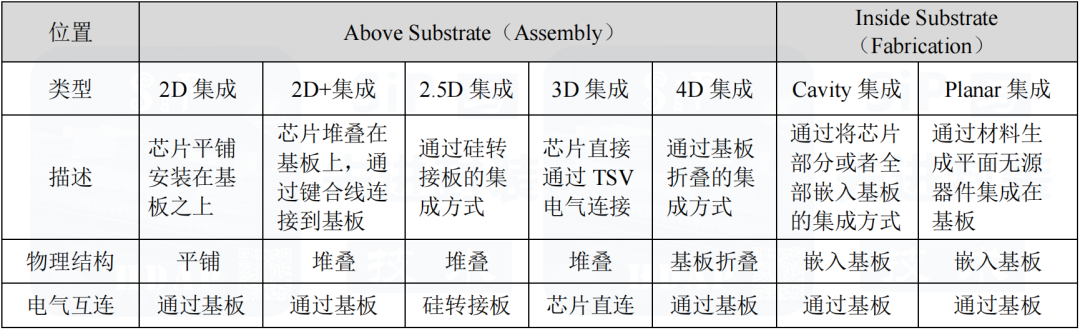

超薄晶圆划切可能导致芯片的卷曲和碎裂,传统的机械划切和激光划切在划切质量和成本等方面都面临着极大的挑战。一种新兴的等离子体划切技术近年来逐渐受到关注:等离子体划切技术与干法刻蚀技术相近,利用等离子体物理轰击和化学反应在硅片表面形成深而细的沟槽,从而达到分割芯片的目的。相对于传统划切技术,等离子体划切具有三大优点:一是芯片侧壁无损伤,没有应力导致的芯片弯曲;二是可以实现多条线的批量划切,减少工艺时间;三是划切通道窄,减少材料损失。 (2)引线键合设备。目前,引线键合仍然是主流的芯片互联方式,占全部封装市场的77%左右,其中用于系统级封装的引线键合市场增长迅速。当前引线键合工艺及设备的发展趋势主要包括四个方面:一是降低成本(主要通过引线材料的变革,由Au线逐渐变更为Ag、Cu线);二是提高产能(近年来,除提升键合机定位平台电机速度外,键合工艺的优化在提升键合设备产能中发挥的作用越来越重要);三是互联密度更大(主要通过新的封装结构和工艺实现);四是采用智能引线键合机(智能引线键合机将实现精确的工艺控制、缺陷检测和可追溯性,从而缩短封装产品的研发时间、提高良率和产能,是未来先进引线键合技术发展的主要驱动力之一)。  (3)倒装键合设备。相对引线键合,倒装键合是高密度封装技术的主要发展方向,有助于实现堆叠芯片和三维封装工艺,在2.5D/3D集成、晶圆级封装、系统级封装等封装技术领域均有广泛应用。 目前倒装芯片的互联方式主要包括热超声(采用金球凸点,Gold stud)、回流焊(采用锡球凸点,Solder bump)和热压(采用铜柱凸点,Copper pillar)三种键合工艺。热超声倒装键合设备基于成熟的引线键合技术,主要用于I/O密度较低的芯片中;回流焊工艺设备通过热回流将蘸有助焊剂的芯片焊接在基板上,是相对主流的倒装焊设备;热压工艺设备主要面向铜柱凸点和微铜柱凸点,凸点密度更高,代表着倒装设备的发展方向,热压工艺设备最大的技术挑战是设备的装片精度(提高装片精度会牺牲工艺速度,从而增大工艺成本)。 除以上三种主要倒装键合技术外,正在开发的先进倒装技术包括基于热压工艺设备的无凸点Cu-Cu直接键合技术。 (4)2.5D/3D集成。2.5D集成是传统的2D封装(两个裸片在封装体内水平排布)的升级,指两个或更多的裸片以倒装键合的形式在基板上水平排布。3D集成指两个或更多的裸片相互堆叠,并直接互联。2.5D/3D集成技术相对传统的2D封装,可实现更高的性能、更低的能耗、更低的延迟、以及更小的芯片尺寸。 2.5D/3D集成都离不开TSV(硅通孔)、倒装键合等封装技术,TSV工艺是关键,相关设备发展是重点。TSV是通过芯片和芯片之间、晶圆和晶圆之间制造垂直通孔,在通孔中电镀铜实现垂直方向上芯片的互联,主要包括通孔刻蚀(使用深反应离子束刻蚀或激光打孔设备)、绝缘层/介电层沉积(CVD设备)、阻挡层/种子层沉积(PVD设备)、通孔镀Cu(ECD设备)、多余Cu去除(CMP设备)等工艺步骤,可见,TSV技术主要基于集成电路前道设备实现。

(3)倒装键合设备。相对引线键合,倒装键合是高密度封装技术的主要发展方向,有助于实现堆叠芯片和三维封装工艺,在2.5D/3D集成、晶圆级封装、系统级封装等封装技术领域均有广泛应用。 目前倒装芯片的互联方式主要包括热超声(采用金球凸点,Gold stud)、回流焊(采用锡球凸点,Solder bump)和热压(采用铜柱凸点,Copper pillar)三种键合工艺。热超声倒装键合设备基于成熟的引线键合技术,主要用于I/O密度较低的芯片中;回流焊工艺设备通过热回流将蘸有助焊剂的芯片焊接在基板上,是相对主流的倒装焊设备;热压工艺设备主要面向铜柱凸点和微铜柱凸点,凸点密度更高,代表着倒装设备的发展方向,热压工艺设备最大的技术挑战是设备的装片精度(提高装片精度会牺牲工艺速度,从而增大工艺成本)。 除以上三种主要倒装键合技术外,正在开发的先进倒装技术包括基于热压工艺设备的无凸点Cu-Cu直接键合技术。 (4)2.5D/3D集成。2.5D集成是传统的2D封装(两个裸片在封装体内水平排布)的升级,指两个或更多的裸片以倒装键合的形式在基板上水平排布。3D集成指两个或更多的裸片相互堆叠,并直接互联。2.5D/3D集成技术相对传统的2D封装,可实现更高的性能、更低的能耗、更低的延迟、以及更小的芯片尺寸。 2.5D/3D集成都离不开TSV(硅通孔)、倒装键合等封装技术,TSV工艺是关键,相关设备发展是重点。TSV是通过芯片和芯片之间、晶圆和晶圆之间制造垂直通孔,在通孔中电镀铜实现垂直方向上芯片的互联,主要包括通孔刻蚀(使用深反应离子束刻蚀或激光打孔设备)、绝缘层/介电层沉积(CVD设备)、阻挡层/种子层沉积(PVD设备)、通孔镀Cu(ECD设备)、多余Cu去除(CMP设备)等工艺步骤,可见,TSV技术主要基于集成电路前道设备实现。  TSV工艺及设备技术在持续提升中,主要挑战和发展方向包括:高密度、高深宽比刻蚀、绝缘层和金属层的低温工艺、高速通孔填充、持续降低成本等。 (5)晶圆级封装(WLP)。晶圆级封装是在晶圆上直接进行裸芯片封装,再切割形成独立的芯片。晶圆级封装可减少封装材料及工序,同时具有轻薄短小的特点,是封装技术发展方向之一。晶圆级封装作为一种新型封装形式,其制备过程同样需要基于键合、减薄、TSV等封装技术和设备。 晶圆级封装最主要的发展趋势是由晶圆级向板级发展:为了追求更高的生产效率进而降低成本,晶圆级封装从传统的以200 mm/300 mm晶圆形式封装向长方形板级封装发展,长方形基板尺寸从300 mm×300 mm、457 mm×610 mm、510 mm×515 mm提升至600 mm×600 mm。从设备角度来说,主要的挑战在于基板形状的变化,很多基于圆形基板的设备(如旋转涂胶设备)等,需要做适应性改造。目前韩国三星电机(SEMCO)和纳沛斯(Nepes)公司都在开展板级封装设备的研发。

TSV工艺及设备技术在持续提升中,主要挑战和发展方向包括:高密度、高深宽比刻蚀、绝缘层和金属层的低温工艺、高速通孔填充、持续降低成本等。 (5)晶圆级封装(WLP)。晶圆级封装是在晶圆上直接进行裸芯片封装,再切割形成独立的芯片。晶圆级封装可减少封装材料及工序,同时具有轻薄短小的特点,是封装技术发展方向之一。晶圆级封装作为一种新型封装形式,其制备过程同样需要基于键合、减薄、TSV等封装技术和设备。 晶圆级封装最主要的发展趋势是由晶圆级向板级发展:为了追求更高的生产效率进而降低成本,晶圆级封装从传统的以200 mm/300 mm晶圆形式封装向长方形板级封装发展,长方形基板尺寸从300 mm×300 mm、457 mm×610 mm、510 mm×515 mm提升至600 mm×600 mm。从设备角度来说,主要的挑战在于基板形状的变化,很多基于圆形基板的设备(如旋转涂胶设备)等,需要做适应性改造。目前韩国三星电机(SEMCO)和纳沛斯(Nepes)公司都在开展板级封装设备的研发。

-

TSV制造工艺概述2025-10-13 4471

-

TSV工艺中的硅晶圆减薄与铜平坦化技术2025-08-12 2163

-

TSV技术的关键工艺和应用领域2025-08-05 3707

-

TSV制造技术里的关键界面材料与工艺2025-08-01 2573

-

TGV和TSV技术的主要工艺步骤2025-06-16 2353

-

TSV以及博世工艺介绍2025-04-17 3291

-

先进封装中TSV工艺需要的相关设备2025-02-19 2581

-

用于2.5D与3D封装的TSV工艺流程是什么?有哪些需要注意的问题?2024-04-17 4724

-

一文解锁TSV制程工艺及技术2024-04-11 10302

-

TSV 制程关键工艺设备技术及发展2024-03-12 2783

-

TSV关键工艺设备及特点2023-02-17 3213

-

TSV工艺流程与电学特性研究2022-06-16 4277

-

深度解读TSV 的工艺流程和关键技术2017-11-24 66915

-

3D封装与硅通孔(TSV)工艺技术2011-12-07 2912

全部0条评论

快来发表一下你的评论吧 !