资料下载

PwFPGA第5部分 - DE0 Nano上的乒乓游戏

描述

这是一个由 5 部分组成的博客,以下是链接:

第 1 部分:FPGA 基础知识

第 2 部分:在 Spartan 6 FPGA 上使用 Xilinx ISE 的组合逻辑

第 3 部分:在 Cyclone-IV FPGA 上使用 Quartus Prime 的顺序逻辑

第 4 部分:在 Artix-7 FPGA 上使用 Vivado 的组合逻辑与顺序逻辑

第 5 部分:最终项目 - DE0 Nano 开发板上的 Pong 游戏

主意:

该项目旨在通过应用本博客前面部分中学到的所有概念来构建一个简单的 Pong 游戏(单人游戏)。

乒乓球游戏的输入(用户控制)将通过旋转编码器,输出可以在 VGA 监视器中看到。

概念:

1. 旋转编码器:-

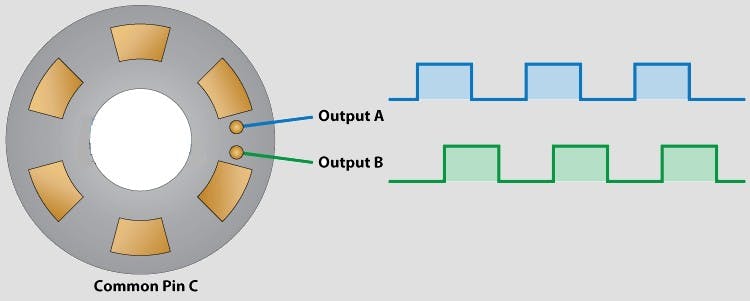

这是旋转编码器的内部接线。黄色表示 VCC,灰色表示 GND。当编码器旋转时,两个输出在 1 和 0 之间切换。

根据脉冲的位置,我们可以确定方向,我们可以将脉冲数作为该方向的计数。

让蓝色波形为输出 1,绿色为输出 2。

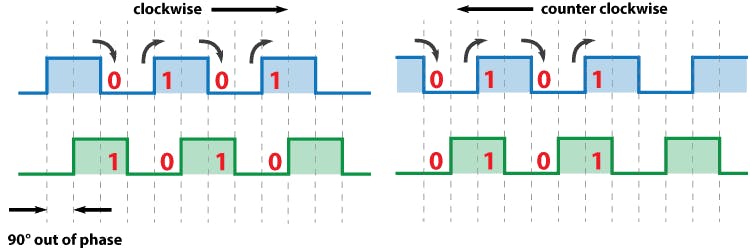

那么我们如何确定方向呢?如果您非常仔细地观察波形,您会注意到在输出 1 的每个上升沿,如果输出 2 为低电平,那么它是顺时针方向的。

在输出 1 的上升沿,如果输出 2 为 HIGH,那么我们可以说它是逆时针的,但这种方法在现实生活中解码信号并不可靠。

我们如何解码信号?

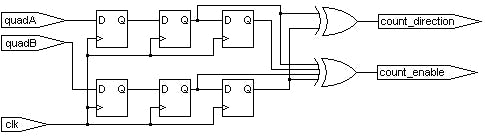

答案 - 正交解码器。

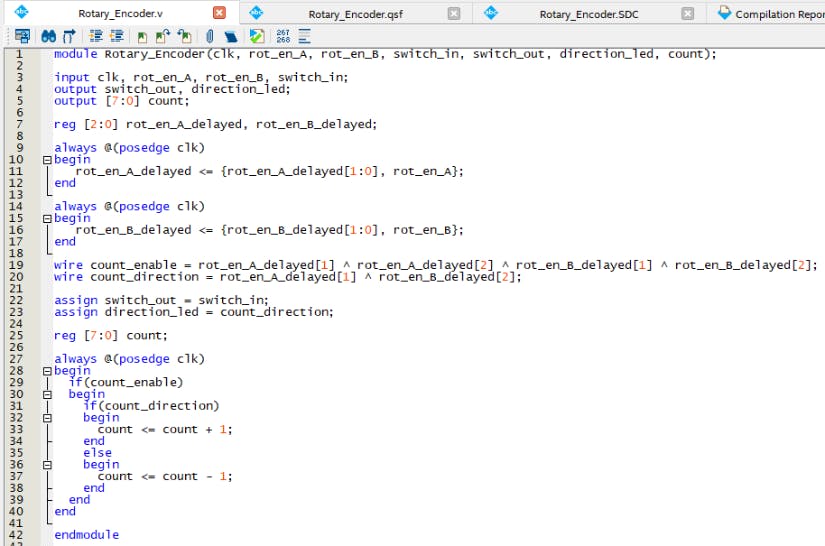

正交解码器的设计:

测试设计:

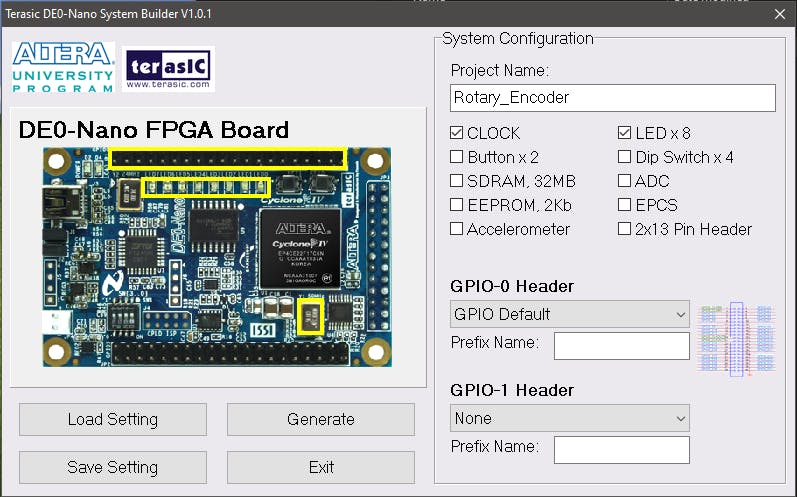

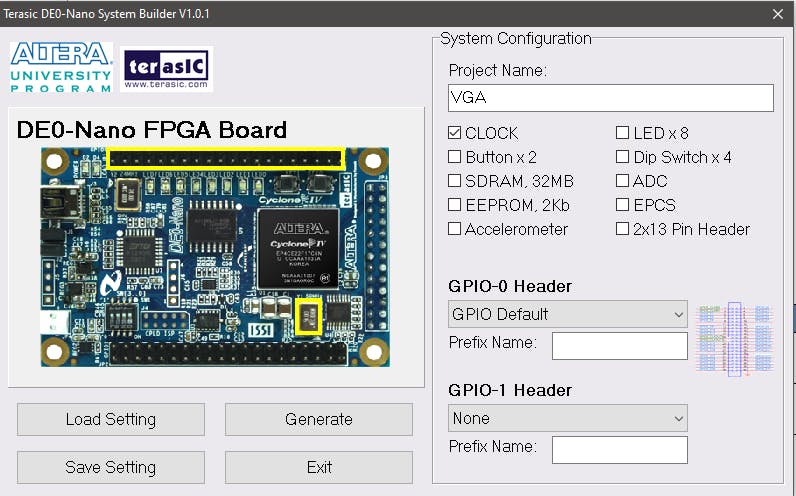

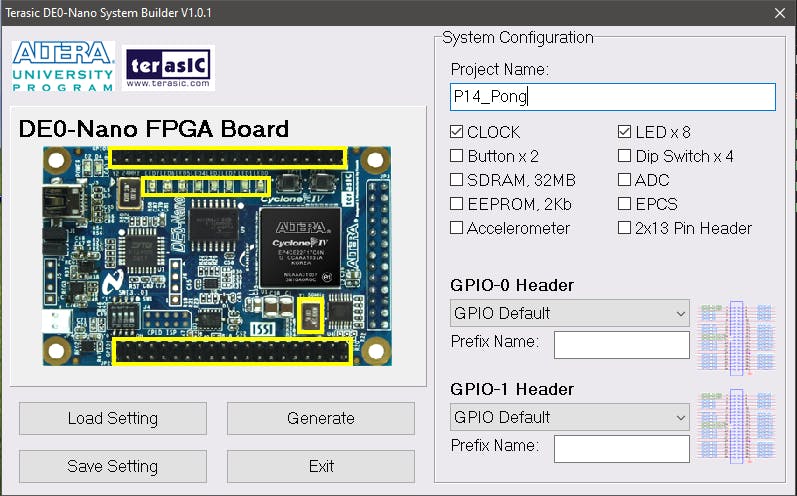

我们将使用 Terasic System Builder 为 Quartus Prime 构建项目。

我们将使用 8 个板载 LED 作为计数器的输出,使用 1 个 RGB LED 作为旋转编码器的方向并检查旋转编码器的开关。

您可以通过查看本博客系列的第 3 部分来熟悉 Quartus Prime 软件。

验证码:

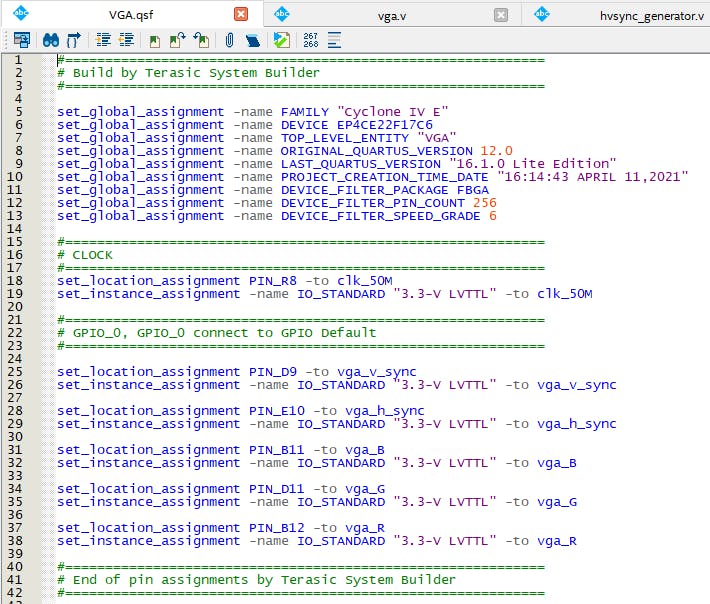

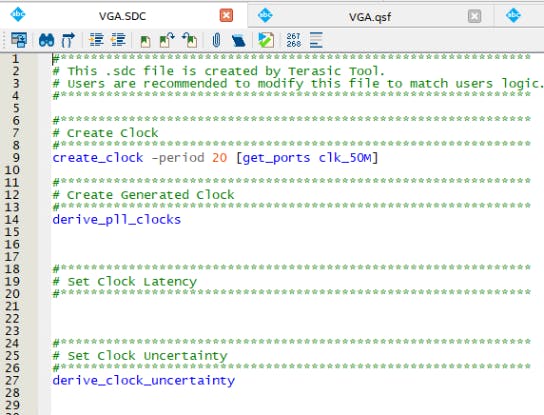

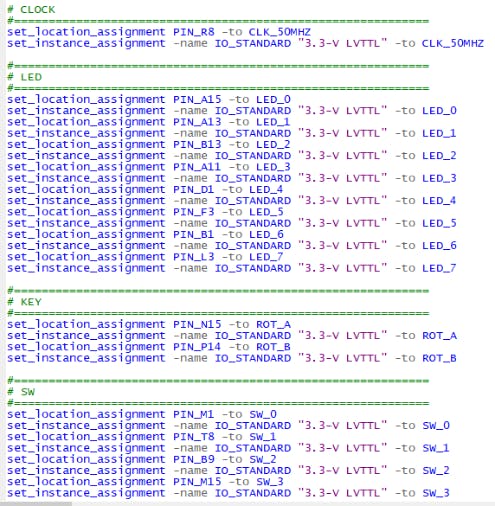

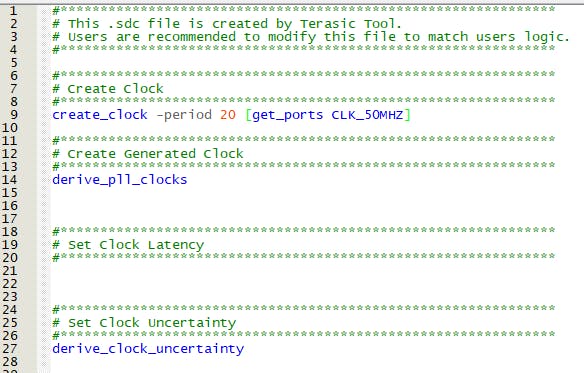

QSF 文件和 SDC 文件:

。

好吧,这个术语对您来说应该非常熟悉,因为我们可能至少使用过一次 VGA 监视器,或者甚至现在可能正在使用它。

1987 年首次与 IBM PS/2 系列计算机一起推出,之后它被广泛用于几乎所有带 DVI 的 PC,直到 2003 年 HDMI 出现,之后由于更高的分辨率和更好的帧速率,它被广泛采用,到了当年2015 年有超过 40 亿台设备使用 HDMI。

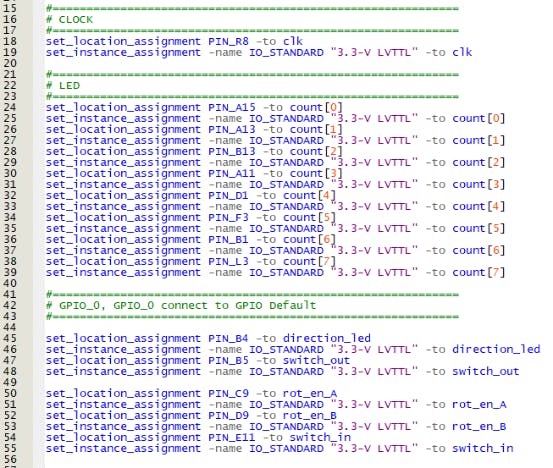

让我们看一下VGA Pinout:

VGA有5种主要信号,分别是红、绿、蓝、水平同步和垂直同步。

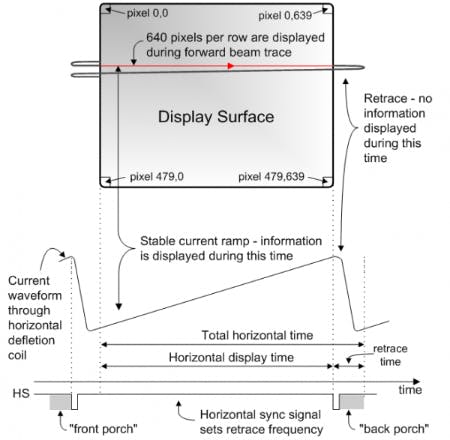

来自多伦多大学的有用信息:

“VGA监视器可以被认为是一个像素网格,其中每个像素是一个可以设置为特定颜色的图片元素。有480行,每行由640个像素组成。(在本项目中使用)VGA接口串行工作,也就是说,每个像素的颜色信息一个接一个地发送,而不是一次发送。

颜色可以使用由每种基本颜色(红、绿、蓝)的强度组成的三元组来表示。监视器期望这些值是模拟的,因此使用了 DAC(数模转换器)。

需要认识到的一个重要事实是 VGA 显示器没有内存,因此不会存储写入其中的像素信息。相反,必须将像素连续发送到显示器以实现稳定的图像。VGA 适配器确实有内存,将负责不断地发送像素信息。”

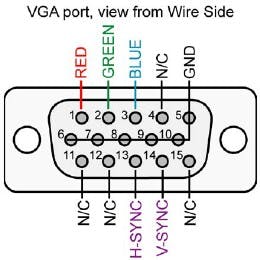

让我们看一下时序图以了解有关该协议的更多信息:

测试VGA协议:

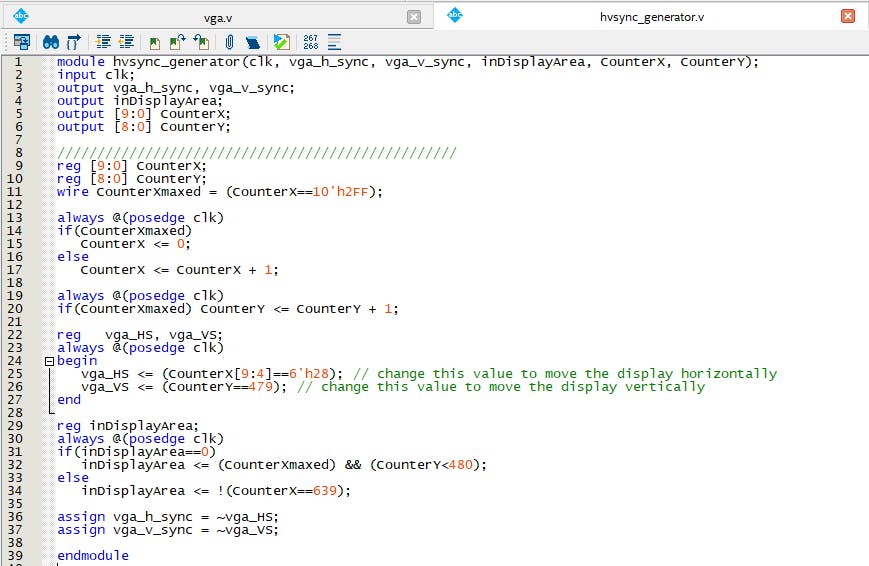

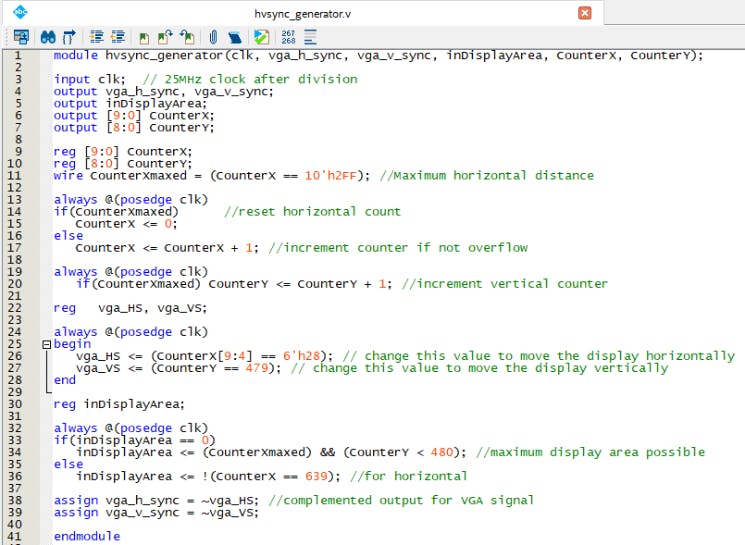

我将使用 Verilog 模块为 VGA 生成水平同步和垂直同步

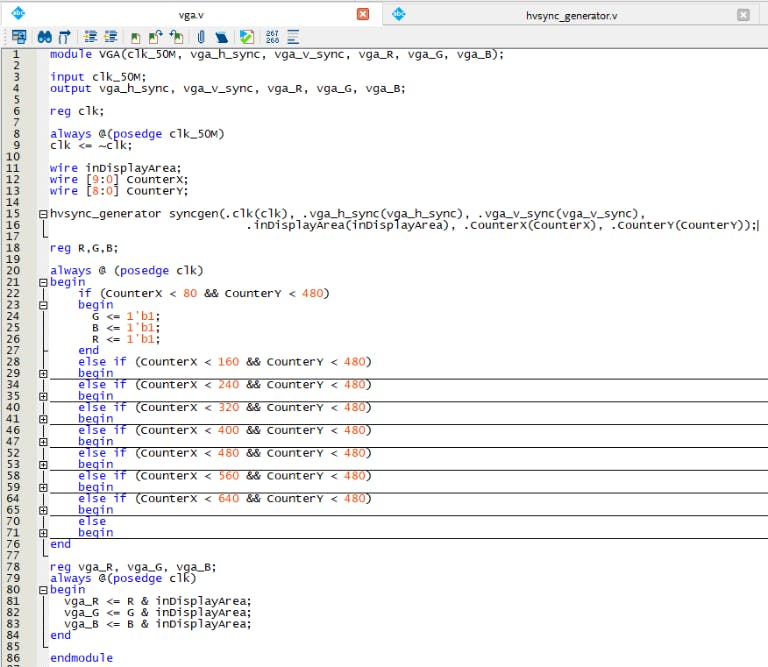

现在,一旦我们有了这个模块,我们就可以在显示器上绘制任何形状。

所需时钟为 25MHz,因此首先将板载 50MHz 除以 2 得到 25MHz。

hvsync_generator 模块将在 VGA(顶部)模块中实例化。数字 160、240 表示监视器中的水平位置,480 是监视器中可能的最大垂直距离。

R-1、G-1、B-1对应白色,R-1、G-0、B-0对应红色,R-1、G-1、B-0对应黄色,以此类推上。

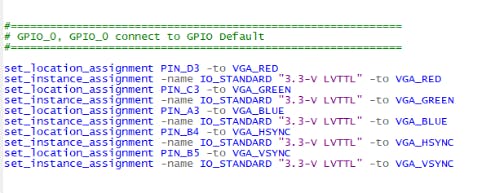

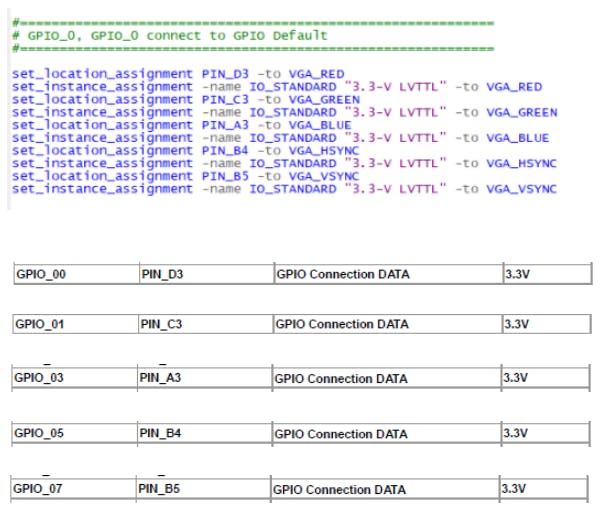

约束文件和SDC文件:

测试 VGA 输出:

现在我们已经学习并测试了旋转编码器和 VGA 模块,让我们开始构建乒乓球游戏。

3. 乒乓游戏的制作:

1.首先创建一个文件,用于生成水平同步和垂直同步信号并固定显示区域

2.接下来添加乒乓球游戏的代码,如以下步骤所述

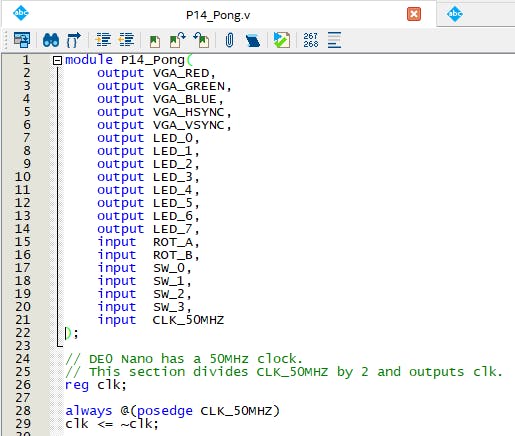

声明输入和输出,然后声明分频器,如博客系列的第 3部分所述

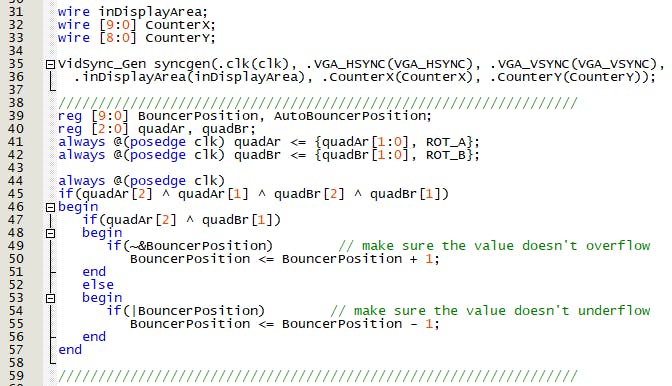

3. 接下来实例化水平同步和垂直同步信号的模块,并编写旋转编码器的代码,如本博客前面所述。

然后我们根据计数器值移动弹跳器,计数器值可以通过旋转编码器递增或递减

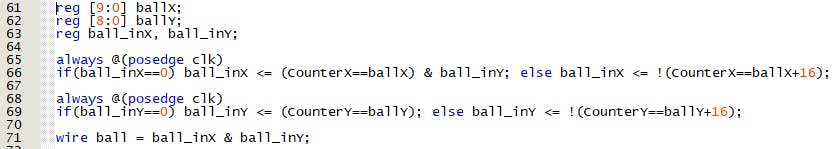

4. 在这一步中,让我们编写将在乒乓球比赛中使用的球的代码:

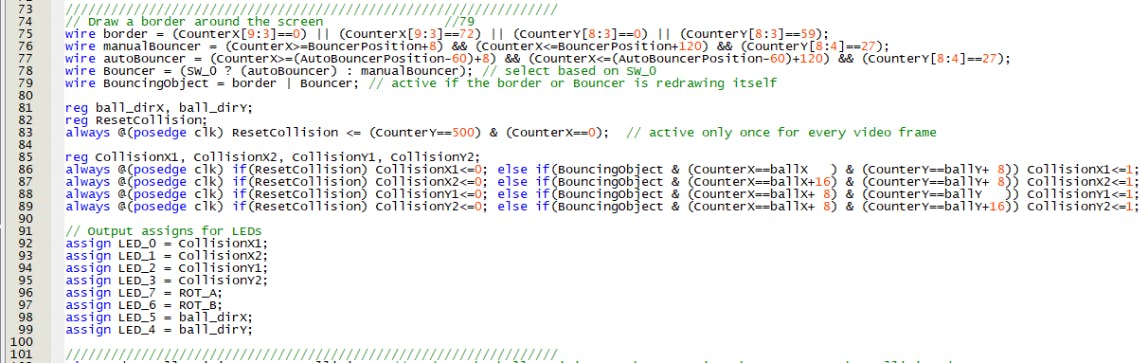

5.根据滑动开关,选择弹跳器是手动还是自动移动,根据球的位置,反转球与任何物体碰撞的方向。

观察碰撞和旋转编码器旋转的方向,设置输出到板载 LED

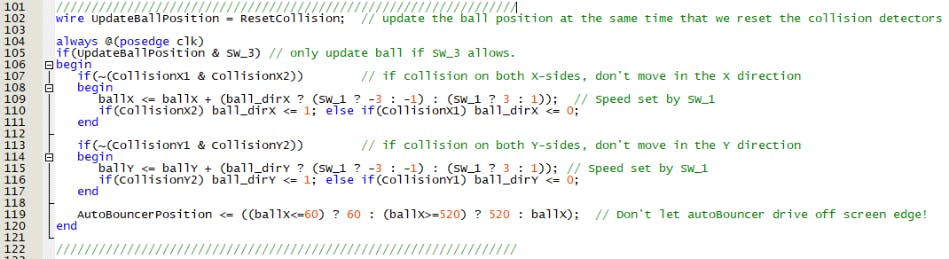

6.接下来编写代码,每次碰撞时更新球的位置并重置碰撞检测器

7. 最后根据开关位置改变颜色,并将 RGB 信号分配给各自的输出,并仅在显示器的总区域内显示。

8.现在写约束文件和SDC文件

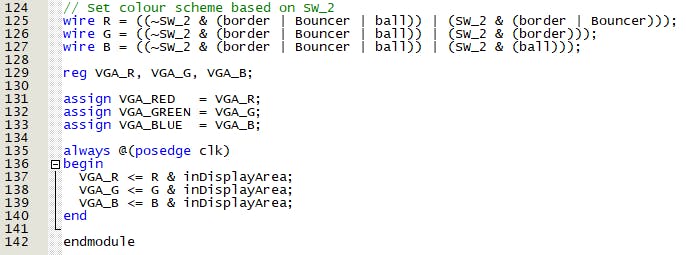

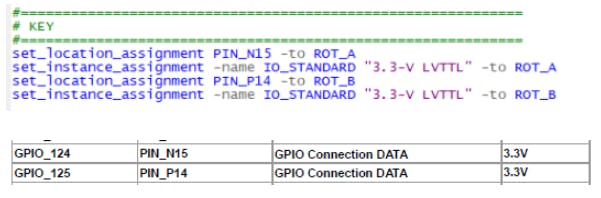

约束文件:

SDC 文件:

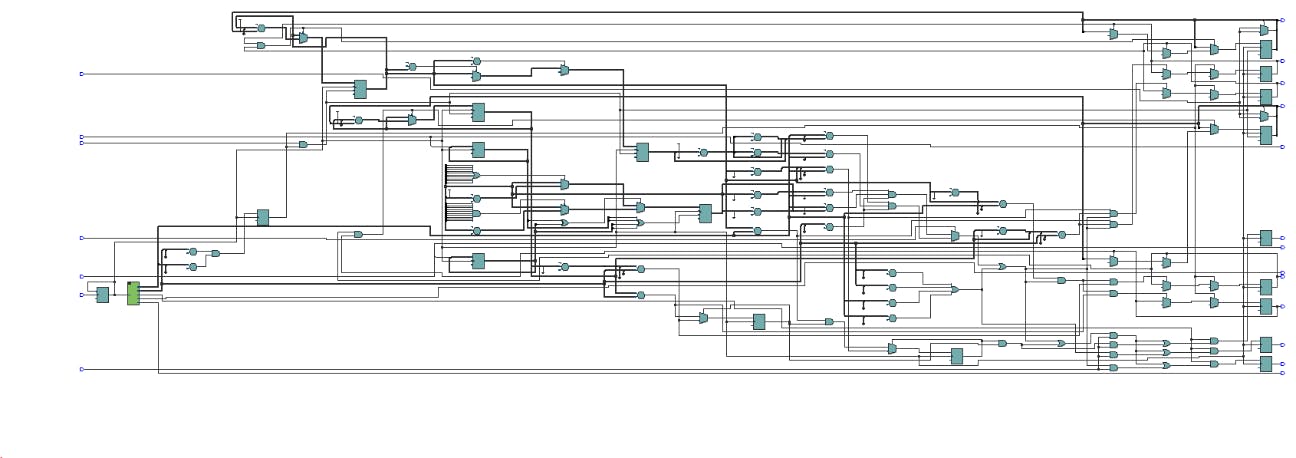

综合逻辑图:

分析起来太复杂了,但它确实有效!

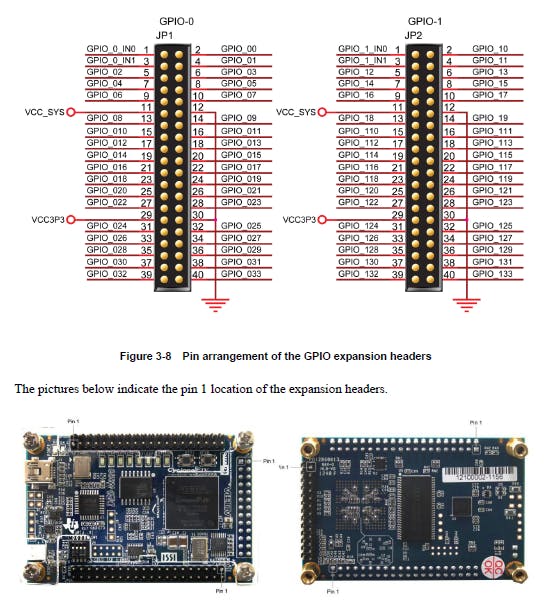

连接:

查看下面给出的约束和图像,以了解有关如何连接模块的更多信息。

VGA:

在 Pmod VGA 中,您会注意到它支持 12 位,但在这个项目中,我们只使用 3 位,红色一位,绿色一位,蓝色一位。

将 DE0 Nano 的 Red 引脚连接到 DAC 中权重最高的 Pmod 的 R3 其余位将在 Pmod 内部接地。

以同样的方式将绿色连接到 G3,将蓝色连接到 B3。在 Pmod 中水平同步到 HS 和垂直同步到 VS。将 Pmod 的 VCC 和 GND 连接到 DE0 Nano 中的相应引脚。

旋转编码器:

按照约束文件中的规定,将旋转编码器的数据引脚连接到 ROT_A 和旋转编码器的 Clk 引脚到 ROT_B 输入。

将旋转编码器的 VCC 和 GND 连接到 DE0 Nano 中的相应引脚。

你完成了!

对 FPGA 进行编程并提供连接(请参阅引脚分配手册),您将看到球和滑块。确保启用所需的开关以查看操作。

乒乓球游戏的最终输出

参考:

1. https://how2electronics.com/construction-working-rotary-encoder/

2. https://reference.digilentinc.com/reference/pmod/pmodvga/reference-manual

3. https://reference.digilentinc.com/learn/programmable-logic/tutorials/vga-display-congroller/start

5. https://numato.com/kb/simple-vga-design-example-for-telesto/

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章