传统封装 Vs.先进封装的区别及优势

制造/封装

描述

华金证券,孙远峰、王海维、王臣复

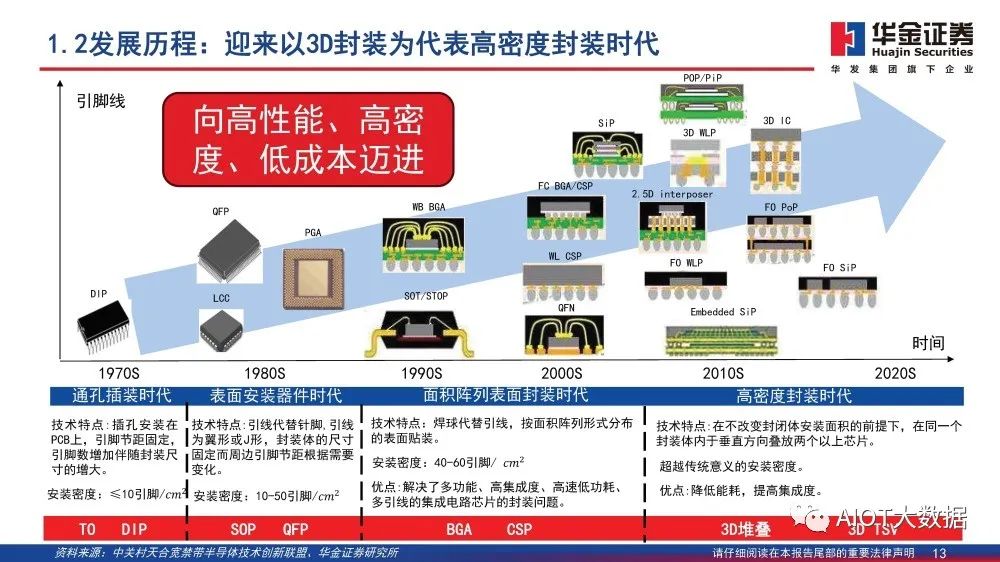

先进封装:打破IC发展限制,向高密度封装时代迈进

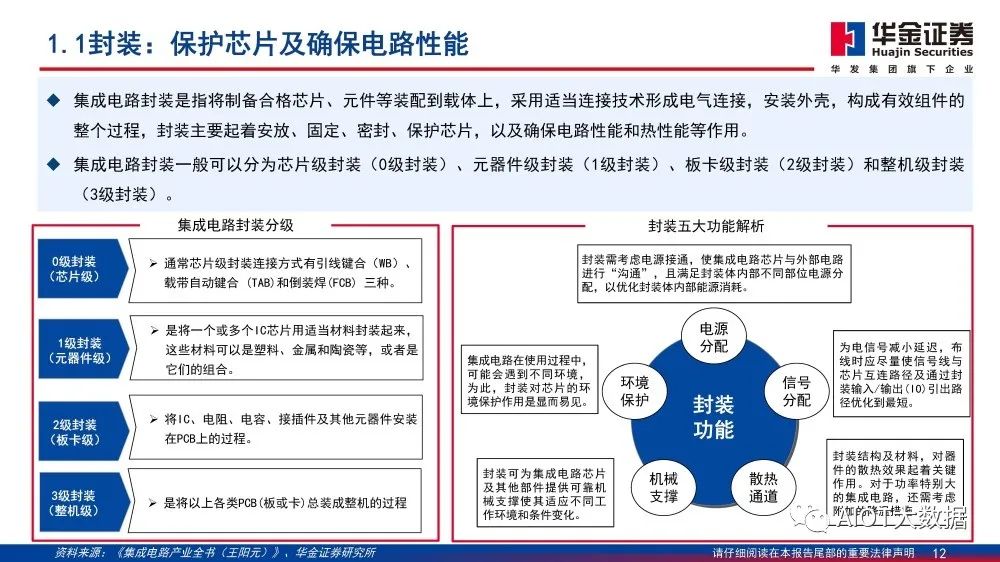

封装:保护芯片及确保电路性能

集成电路封装是指将制备合格芯片、元件等装配到载体上,采用适当连接技术形成电气连接,安装外壳,构成有效组件的整个过程,封装主要起着安放、固定、密封、保护芯片,以及确保电路性能和热性能等作用。 集成电路封装一般可以分为芯片级封装(0级封装)、元器件级封装(1级封装)、板卡级封装(2级封装)和整机级封装(3级封装)。

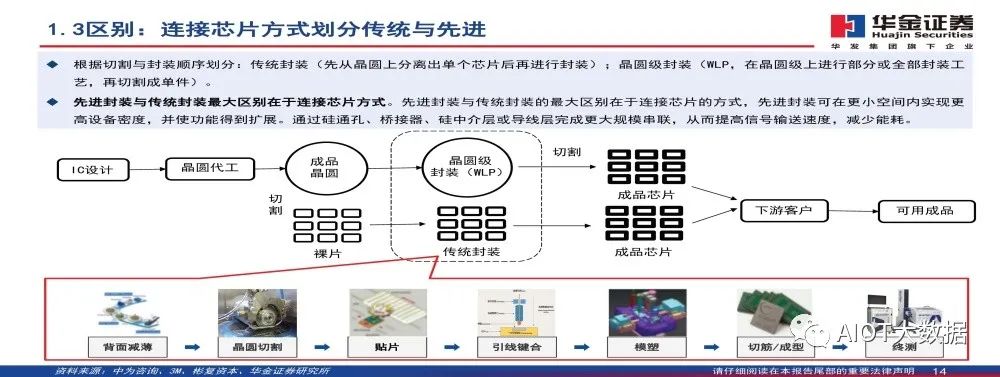

区别:连接芯片方式划分传统与先进

根据切割与封装顺序划分:传统封装(先从晶圆上分离出单个芯片后再进行封装);晶圆级封装(WLP,在晶圆级上进行部分或全部封装工艺,再切割成单件)。 先进封装与传统封装最大区别在于连接芯片方式。先进封装与传统封装的最大区别在于连接芯片的方式,先进封装可在更小空间内实现更高设备密度,并使功能得到扩展。通过硅通孔、桥接器、硅中介层或导线层完成更大规模串联,从而提高信号输送速度,减少能耗。

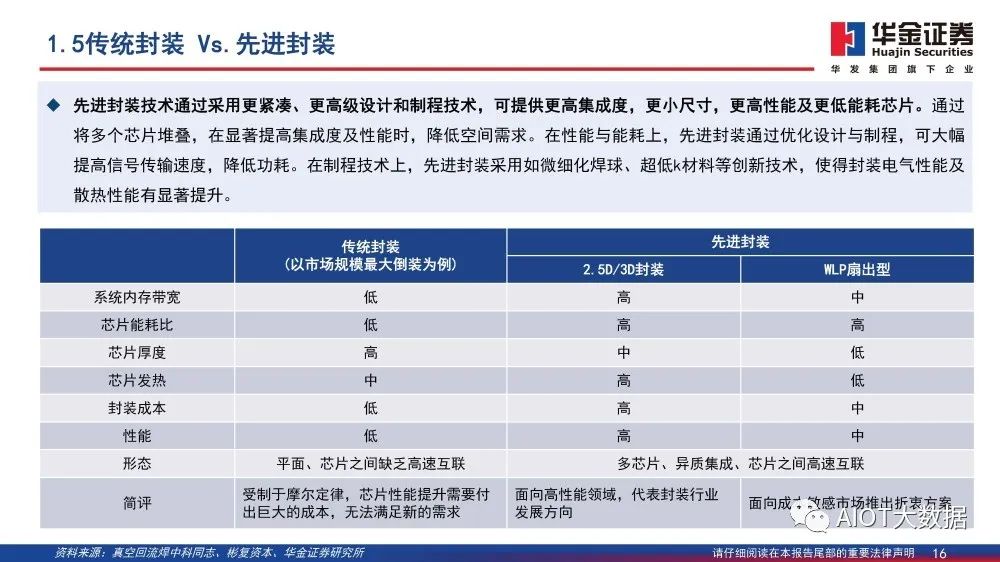

传统封装 Vs.先进封装

先进封装技术通过采用更紧凑、更高级设计和制程技术,可提供更高集成度,更小尺寸,更高性能及更低能耗芯片。通过将多个芯片堆叠,在显著提高集成度及性能时,降低空间需求。在性能与能耗上,先进封装通过优化设计与制程,可大幅提高信号传输速度,降低功耗。在制程技术上,先进封装采用如微细化焊球、超低k材料等创新技术,使得封装电气性能及散热性能有显著提升。

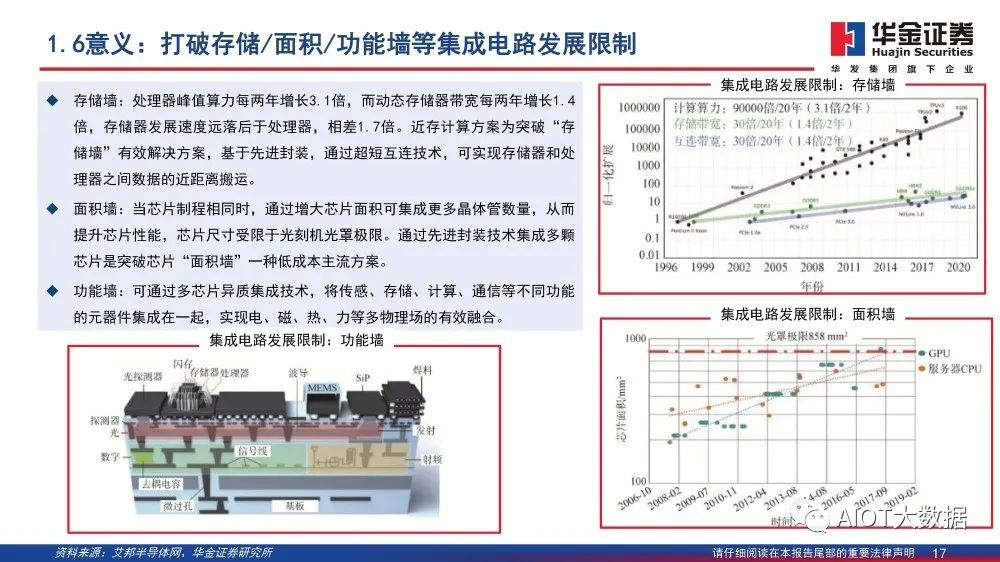

意义:打破存储/面积/功能墙等集成电路发展限制

存储墙:处理器峰值算力每两年增长3.1倍,而动态存储器带宽每两年增长1.4 倍,存储器发展速度远落后于处理器,相差1.7倍。近存计算方案为突破“存 储墙”有效解决方案,基于先进封装,通过超短互连技术,可实现存储器和处 理器之间数据的近距离搬运。 面积墙:当芯片制程相同时,通过增大芯片面积可集成更多晶体管数量,从而 提升芯片性能,芯片尺寸受限于***光罩极限。通过先进封装技术集成多颗 芯片是突破芯片“面积墙”一种低成本主流方案。 功能墙:可通过多芯片异质集成技术,将传感、存储、计算、通信等不同功能 的元器件集成在一起,实现电、磁、热、力等多物理场的有效融合。

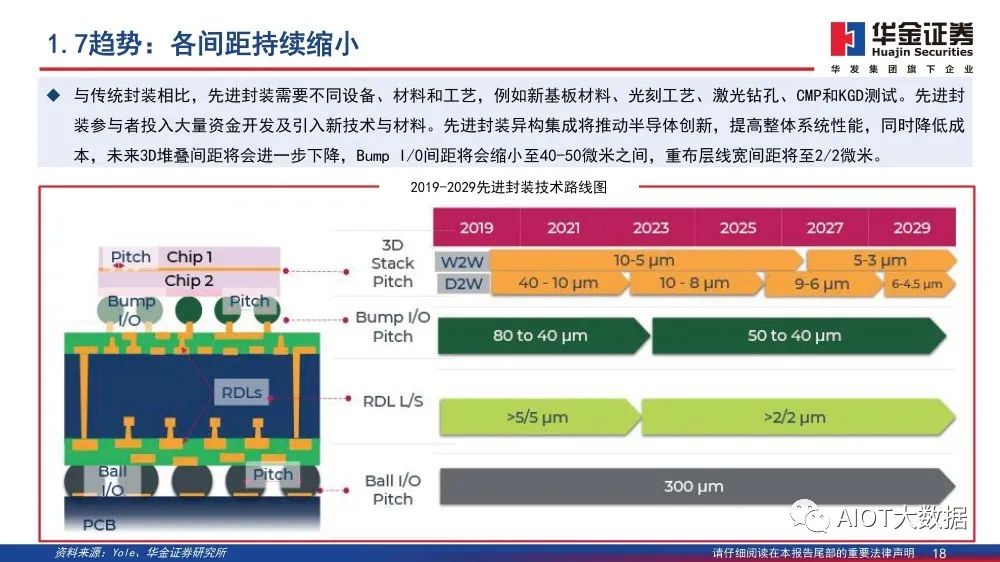

趋势:各间距持续缩小

与传统封装相比,先进封装需要不同设备、材料和工艺,例如新基板材料、光刻工艺、激光钻孔、CMP和KGD测试。先进封装参与者投入大量资金开发及引入新技术与材料。先进封装异构集成将推动半导体创新,提高整体系统性能,同时降低成本,未来3D堆叠间距将会进一步下降,Bump I/0间距将会缩小至40-50微米之间,重布层线宽间距将至2/2微米。

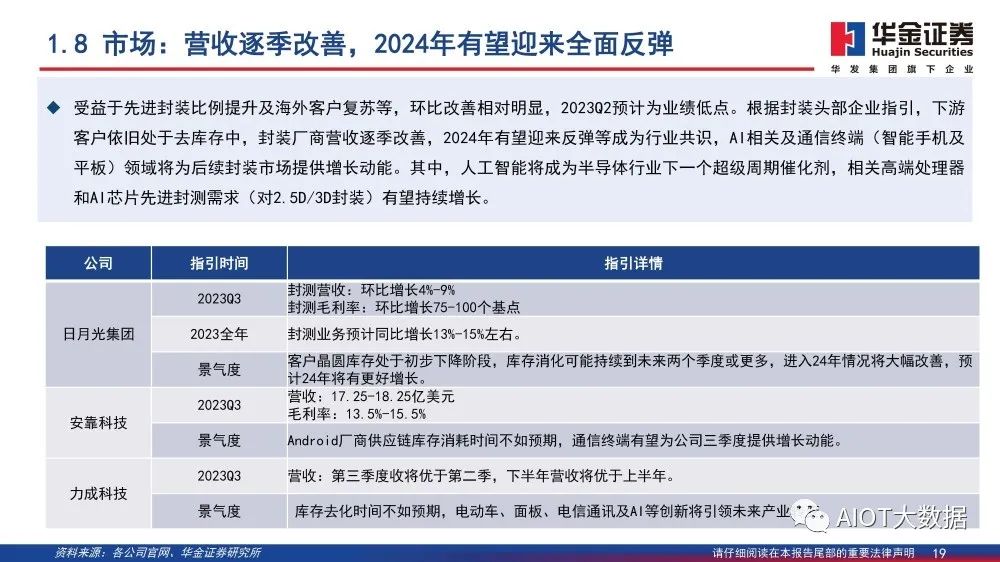

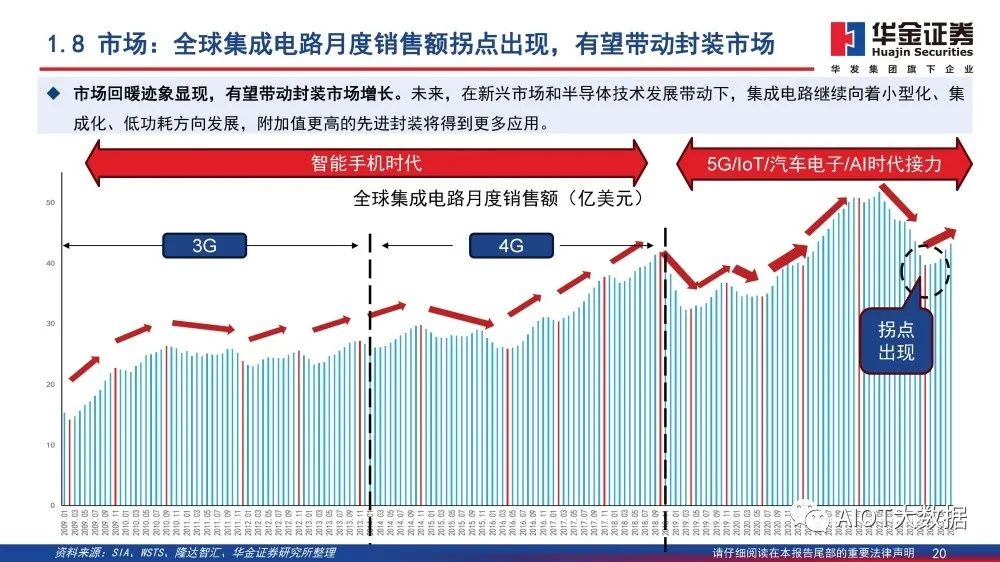

市场:营收逐季改善,2024年有望迎来全面反弹

受益于先进封装比例提升及海外客户复苏等,环比改善相对明显,2023Q2预计为业绩低点。根据封装头部企业指引,下游客户依旧处于去库存中,封装厂商营收逐季改善,2024年有望迎来反弹等成为行业共识,AI相关及通信终端(智能手机及平板)领域将为后续封装市场提供增长动能。其中,人工智能将成为半导体行业下一个超级周期催化剂,相关高端处理器和AI芯片先进封测需求(对2.5D/3D封装)有望持续增长。

技术分析:横向连接/纵向堆叠奠定先进封装技术基石

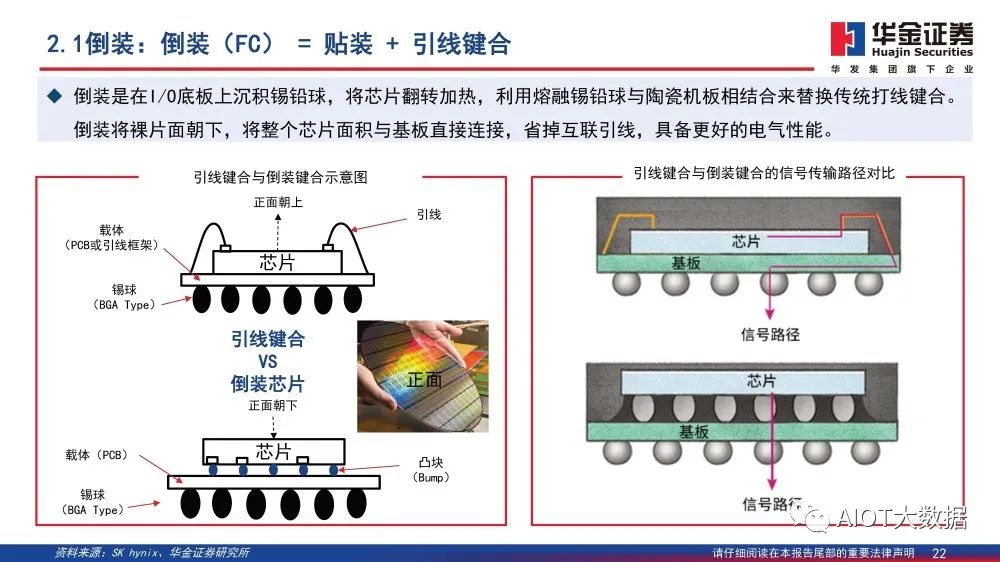

倒装:倒装(FC) = 贴装 + 引线键合

倒装是在I/O底板上沉积锡铅球,将芯片翻转加热,利用熔融锡铅球与陶瓷机板相结合来替换传统打线键合。倒装将裸片面朝下,将整个芯片面积与基板直接连接,省掉互联引线,具备更好的电气性能。

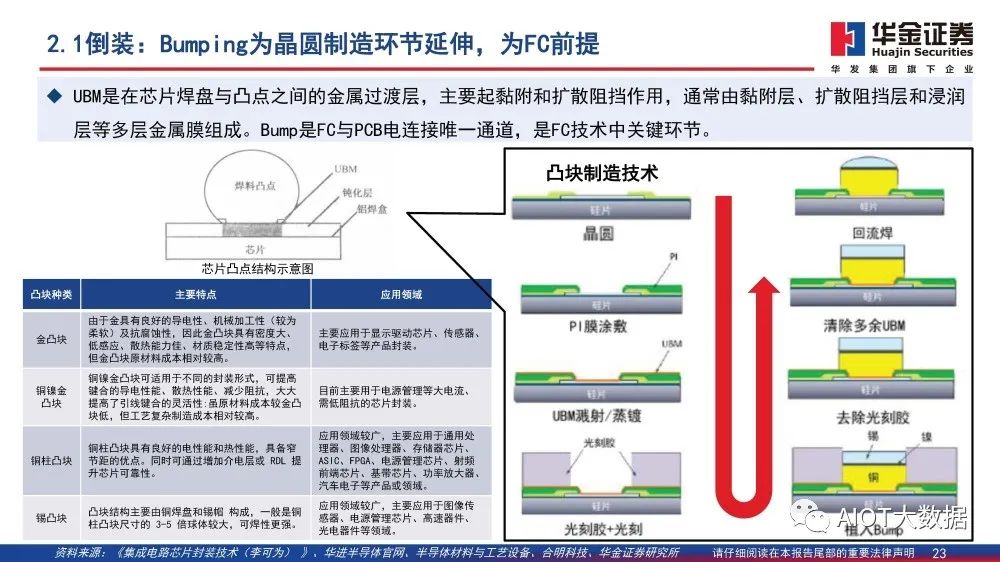

UBM是在芯片焊盘与凸点之间的金属过渡层,主要起黏附和扩散阻挡作用,通常由黏附层、扩散阻挡层和浸润层等多层金属膜组成。Bump是FC与PCB电连接唯一通道,是FC技术中关键环节。

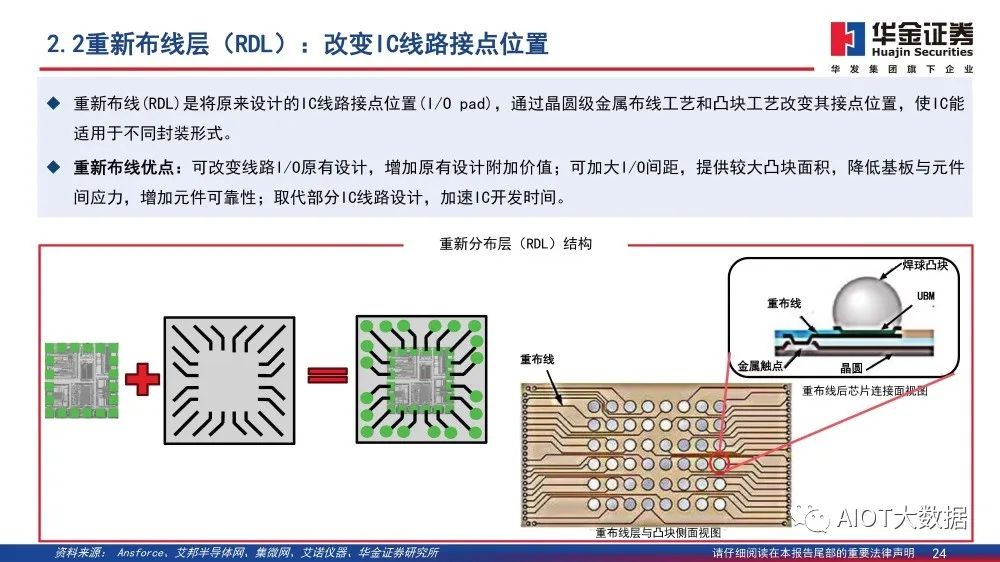

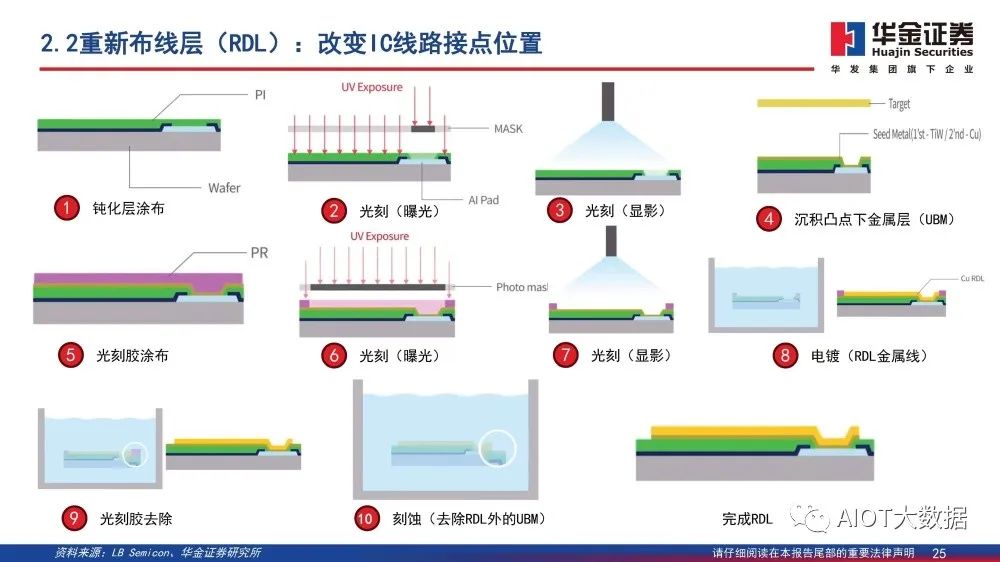

重新布线层(RDL):改变IC线路接点位置

重新布线(RDL)是将原来设计的IC线路接点位置(I/O pad),通过晶圆级金属布线工艺和凸块工艺改变其接点位置,使IC能适用于不同封装形式。 重新布线优点:可改变线路I/O原有设计,增加原有设计附加价值;可加大I/O间距,提供较大凸块面积,降低基板与元件间应力,增加元件可靠性;取代部分IC线路设计,加速IC开发时间。

晶圆级封装(WLP):在晶圆上对芯片进行操作

晶圆级封装是指先在整片晶圆上同时对众多芯片进行封装、测试,最后切割成单个器件,并直接贴装到基板或PCB上,生产成本大幅降低。 由于没有引线、键合和塑胶工艺,封装无需向芯片外扩展,使得WLP的封装尺寸几乎等于芯片尺寸。

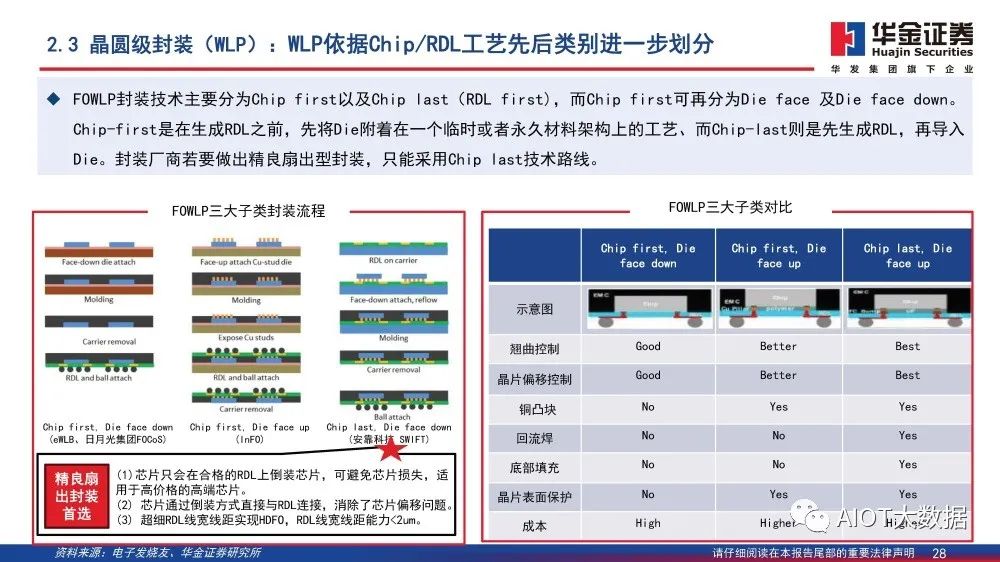

晶圆级封装(WLP):WLP依据Chip/RDL工艺先后类别进一步划分

FOWLP封装技术主要分为Chip first以及Chip last(RDL first),而Chip first可再分为Die face 及Diefacedown。Chip-first是在生成RDL之前,先将Die附着在一个临时或者永久材料架构上的工艺、而Chip-last则是先生成RDL,再导入Die。封装厂商若要做出精良扇出型封装,只能采用Chip last技术路线。

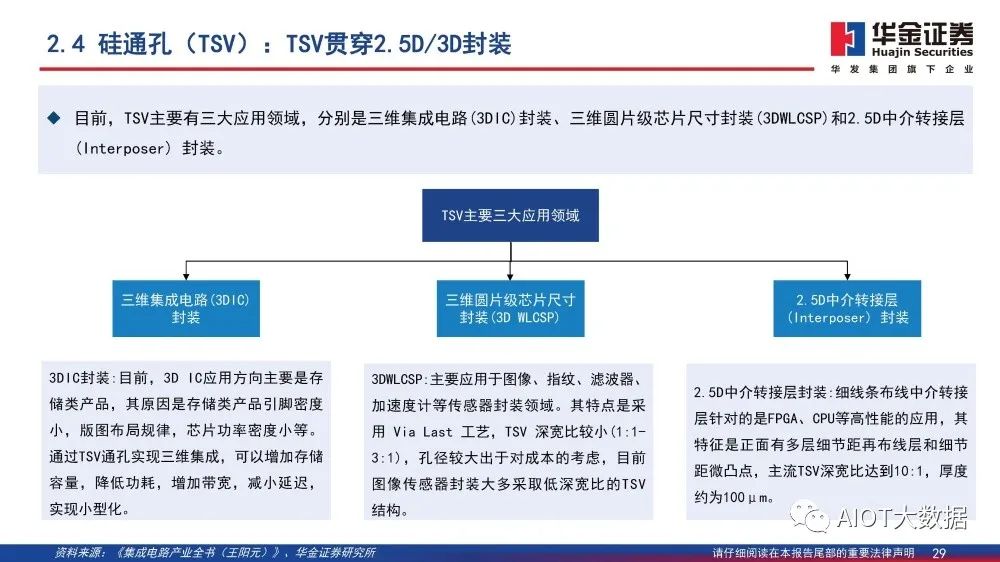

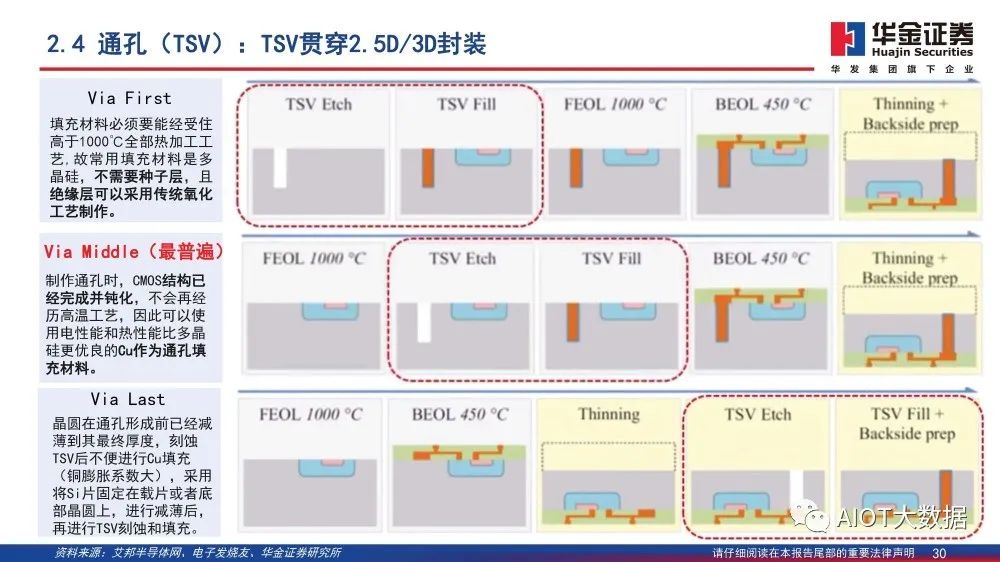

硅通孔(TSV):2.5D封装TSV充当多颗裸片和电路板之间桥梁

中介层是一种由硅及有机材料制成硅基板,是先进封装中多芯片模块传递电信号的管道,可以实现芯片间的互连,也可以实现与封装基板的互连,充当多颗裸片和电路板之间的桥梁。硅中介层是一种经过验证的技术,具有较高的细间距布线能力和可靠的TSV能力,可以实现高密度I/O需求,在2.5D封装中扮演着关键角色。 2.5D集成关键在于中介层Interposer:1)中介层是否采用硅转接板;2)中介层是否采用TSV,在硅转接板上穿越中介层(TSV),在玻璃转接板上穿越中介层(TGV)。

硅通孔(TSV):TSV在2.5D封装中应用实例——CoWoS

CoWoS实质为2.5D封装,依据中介层采用不同技术划分为CoWoS-S、CoWoS-L及CoWoS-R三大技术。CoWoS-S采用硅中介层,为高性能计算应用提供最佳性能及最高晶体管密度;CoWoS-R类似InFO技术,利用RDL中介层进行互连,更强调小芯片间互连;CoWoS-L结合CoWoS-S及InFO技术优点,使用夹层与LSI(局部硅互连)芯片进行互连,使用RDL层进行电源与信号传输,提供最灵活集成。

混合键合(HB):混合键合利用范德华力实现

混合键合是通过分子间作用力(范德华力) 实现,使用化学机械抛光对大马士革布线层进行表面处理,CMP过程还可以减少Cu线路腐蚀和Cu凹陷。当Cu和Si�2的光滑界面相互接触时形成范德华力。为增强表面结合力,通常需要增加等离子体活化工序,然后再通过高精度倒装热压工序,实现多界面之间混合键合。 HB技术简化3D堆叠布线层,与含有TSV的3D堆叠技术相比,HB工艺中铜触点pitch size少于10微米,可实现更高互联密度HB技术,且可直接省略再布线,使设计难度降低,避免再布线及倒装回流焊可提高可靠性。

板级埋入式封装:无需Si中介层及TSV工艺

EMIB是将带有多层导电金属(back end of line,BEOL)互连的超 薄硅片埋入有机封装基板的最上层,通过焊球与倒装芯片的连接, 以实现两个或多个芯片之间的局部高密度互连。与传统封装中在基 板表面贴装芯片或元件不同,板级埋入式封装直接将芯片或元件嵌 入基板中间,因此它具有更短的互连路径、更小的体积、更优的电 热性能及更高的集成度。与台积电的CoWoS-S封装相比,EMIB封装既不需要TSV工也不需要Si 中介层,因此其具有封装良率高、设计简单、成本更低等优点。

产业链:材料与设备任重道远,先进封装粲然可观

封装材料:各类半导体材料集中度较低,国产替代呈现两极分化

先进封装发展拉动封装材料需求,2027年市场规模有望达300美元。根据SEMI数据,2022年全球半导体材料市场收入增长8.9%达727亿美元,其中封装材料市场规模为280亿美元,同比增长6.3%,其中有机基板领域增长积极推动封装材料市场;介电材料和底部填充的发展推动对扇入和扇出晶圆级封装 (FOWLP)、倒装芯片和 2.5D/3D 封装的强劲需求。使用RDL(重新分布层)硅中介层和有机中介层等新型基板技术也是封装解决方案关键增长动力,2027年全球半导体封装材料市场预计达到298亿美元。

高端基板:先进封装带动高端基板需求,国产化亟待突破

先进封装技术带动ABF载板需求。先进封装能协助芯片整合在面积不变下,促成更高效率,透过芯片间互联封装技术,完成来自不同制程、不同材料各个芯片置于中介层基板之上进行整合,要将这些芯片整合在一起,就是需要更大ABF载板来放置。FCBGA凭借内部采FC、外部采BGA的封装方式,成为目前主流的封装技术,作为ABF载板应用较多的封装技术,FCBGAI/O数量达到32-48,因而拥有非常优异的性能与成本优势。此外,2.5D封装I/O数量是2D FC封装数倍以上,在显著提升高阶芯片效能同时,所需的ABF载板也变得更为复杂。Intel嵌入式封装技术,I/O数高达250-1000,提高芯片互连密度,并且将硅中介层内嵌于ABF,增加ABF面积、层数与制作难度,将消耗更多ABF产能。

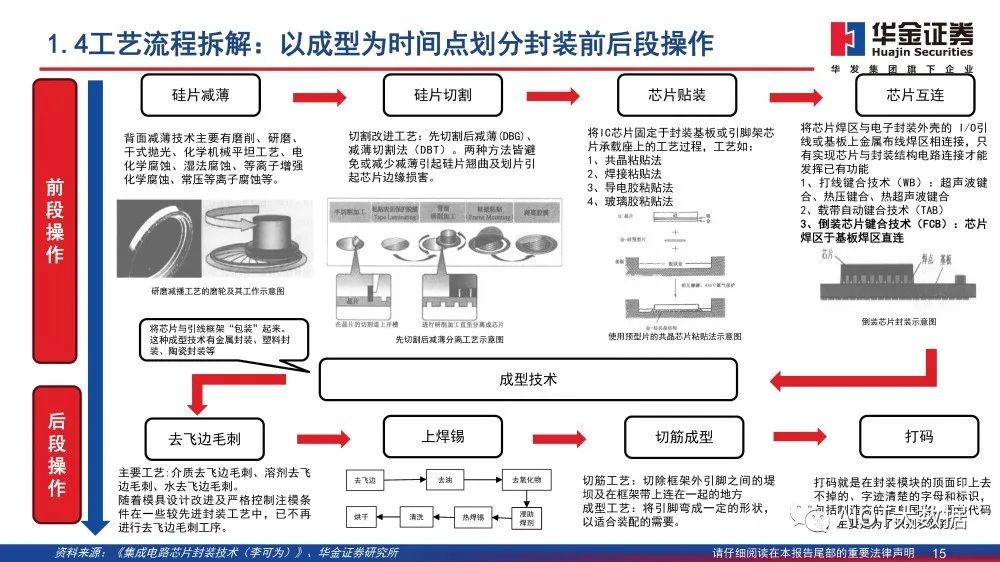

先进封装设备:晶圆划片前融入封装工艺步骤,前道设备需求加剧

先进封装处于晶圆制造与封测中的交叉区域。先进封装要求在晶圆划片前融入封装工艺步骤,具体包括应用晶圆研磨薄化、线路重排(RDL)、凸块制作(Bumping)及三维硅通孔(TSV)等工艺技术。先进封装更多在晶圆层面上进行,采用前道制造方式来制作后道连接电路,工艺流程的相似性使得两者使用设备也大致相同,其中倒装就要采用植球、电镀、光刻、蚀刻等前道制造的工艺,2.5D/3D封装TSV技术就需要***、涂胶显影设备、湿法刻蚀设备等,从而使得晶圆制造与封测前后道制程中出现中道交叉区域。

先进封装:2027年先进封装市场规模有望达650亿美元

先进封装市场有望达650亿美元,芯片倒装占比最大,芯片嵌入式封装增速最快。根据Yole数据,2021年全球先进封装市场规模为374亿美元,其中芯片倒装占比最大为70%,2.5D/3D封装次之;2027年全球先进封装市场规模预计为650亿美元,其中芯片倒装占比为66%(较2021年下滑4pcts),2.5D/3D占23%,约150亿美元,芯片嵌入式增速最快,21-27年CAGR为24%。

行业现状:制造与IDM厂商入驻先进封装,开辟中道工艺

台积电:前段(CoW/WoW)+后段(oS/InFO) = 3D Fabric

下游应用多点爆发挑战计算极限,更快,更节能芯片需求增加。随着云计算、大数据分析、人工智能、神经网络训练、人工智能推理、先进智能手机移动计算及自动驾驶等应用领域不断发展,需要更快、更节能的芯片来满足计算需求。在3D芯片堆叠方面,台积电在系统整合芯片(TSMC-SoIC)技术加入微凸块,以支持更具成本敏感度应用;CoWoS平台得以实现先进逻辑及高带宽存储器整合,适用于人工智能、机器学习及数据中心等HPC应用;整合型扇出层叠封装技术(InFO_PoP)及InFO-3D支持移动应用,InFO-2.5D则支持HPC小芯片整合。

三星:I-Cube2.5D=I-Cube S + I-Cube E + H-Cube

I-CUBE S是一种异构技术,将一块逻辑芯片与一组高带宽存储器 (HBM) 裸片水平放置在一个硅中介层上,实现高算力、高带宽数据传输及低延迟等特点;I-Cube E技术采用硅嵌入结构,不仅具有硅桥精细成像优势,也同时拥有PLP(面板级封装技术)大尺寸、无硅通孔 (TSV) 结构的RDL中介层等特点;H-Cube是一种混合基底结构,将精细成像的ABF基底和HDI(高密度互连)基底技术相结合,可在I-Cube 2.5D封装中实现较大封装尺寸。

Intel:嵌入式多芯片互连桥(EMIB)为Intel2.5D封装亮点

结构简单及信号干扰低是英特尔主导开发EMIB路线主要优势,应用这一技术,封装过程中无需制造覆盖整个芯片硅中介层,以及遍布在硅中介层上大量硅通孔(TSV),而只需使用较小硅桥在裸片间进行互联即可。与普通封装技术相比,由芯片I/O 至封装引脚连接并未发生变化,而无需再通过TSV或硅中介层进行走线。在降低不同裸片间传输延时同时也减少信号传输干扰。

安靠科技:深度布局TSV-less工艺(FOWLP,Chip last, Die face down)

SLIM及SWIFT方案均采用TSV-less工艺,简化2.5D TSV硅中介层运用时PECVD及CMP工序。SLIM利用前道代工,在硅片表面的无机介质层上制作1µm,甚至亚微米金属布线,再用有机介质层制作金属布线,通过倒装互连、芯片塑封后,刻蚀去掉硅片,再制作BGA,完成三维集成。SWITT特点是在Carrier基板上制作多层布线,与芯片通过微凸点倒装,然后塑封,通过穿透模塑料高铜柱实现三维垂直互连,进一步在背面再做一层布线,用于与上封装体进行高密度互连。

应用与需求:芯粒IP复用延续摩尔定律,新建晶圆厂与产线扩产共促封测需求

Chiplet:大道至简,芯粒IP复用构建高集成度芯片

Chiplet(芯粒,也叫小芯片)将一类满足特定功能Die(裸片)通过Die-to-Die内部互联技术将多个模块芯片与底层基础芯片封装在一起,形成一个系统芯片(Soc芯片),从而实现一种新形式IP复用。 Chiplet技术背景下,可将大型单片芯片划分为多个相同或者不同小芯片,这些小芯片可以使用相同或者不同工艺节点制造,再通过跨芯片互联及封装技术进行封装级别集成,降低成本的同时获得更高的集成度。

应用: 5G/物联网/高性能运算/智能驾驶/XR等带动先进封装需求

从长期来看,先进封装技术必将随着终端应用的升级和对芯片封装性能的提升而蓬勃发展。随着新技术演进,以2.5D/3D为代表的先进封装工艺已深入大多数高端芯片生产。

应用:手机与消费领域为先进封装最大应用领域

手机与消费领域仍为先进封装最大应用领域,电信与基础设施占比增速最快。根据Yole数据,2022年,移动和消费者占先进封装市场总量70%,预计2022年至2028年复合年增长率为7%,到2028年将占先进封装收入61%。电信和基础设施领域增长最快,预计2022年至2028年复合年增长率约为17%,预计到2028年将占先进封装市场27%;预计2028年汽车占市场9%,而其他(医疗、工业和航空航天/国防等领域)将占3%。

需求:中国晶圆厂独占鳌头,预计至2024年底建立50座大型晶圆厂

中国晶圆厂数目独占鳌头,韩国系后起之秀。根据电子工程专辑数据,截至2021年底中国(包含中国台湾)晶圆厂数目为78座,成为世界上拥有最多晶圆厂国家,美国(46)、日本(44)分别排名第二、第三。近年来韩国加大集成电路投资规模,2014年超过德国成为世界第四大晶圆制造国家,截至2021年底韩国拥有25座晶圆厂,后发动力不可小觑。根据SEMI数据,预计至2024年底,中国将新建立50座大型晶圆厂,其中中国台湾预计投入19座。

报告节选:

编辑:黄飞

-

传统封装和先进封装的区别在哪2023-08-28 3570

-

HRP晶圆级先进封装替代传统封装技术研究(HRP晶圆级先进封装芯片)2023-11-30 4396

-

传统封装和先进封装的区别2024-01-16 2972

-

#硬声创作季 【科普向】传统封装与先进封装有何差异?——为什么需要先进封装Mr_haohao 2022-10-21

-

传统封装你了解多少,小白快捷学习 | 第1集 #传统封装 #先进封装 #芯片封装 #华芯邦 #孔科微电子 2025-01-21

-

Current vs. Voltage Feedback Amp2017-03-24 1161

-

轴向vs.径向引线:他们真正的区别是什么?2019-07-02 21686

-

先进封装对比传统封装的优势及封装方式2020-10-21 33373

-

什么是先进封装?先进封装和传统封装区别 先进封装工艺流程2023-08-11 5554

-

什么是先进封装?和传统封装有什么区别?2023-08-14 3087

-

HRP晶圆级先进封装替代传统封装技术研究2023-11-18 997

-

先进封装与传统封装的区别2024-07-18 7476

-

先进封装的重要设备有哪些2024-10-28 2491

-

半导体传统封装与先进封装的对比与发展2025-07-30 2232

-

半导体先进封装和传统封装的本质区别2026-03-31 2098

全部0条评论

快来发表一下你的评论吧 !