解析扇入型封装和扇出型封装的区别

电子说

描述

技术前沿:扇出型板级封装FOPLP

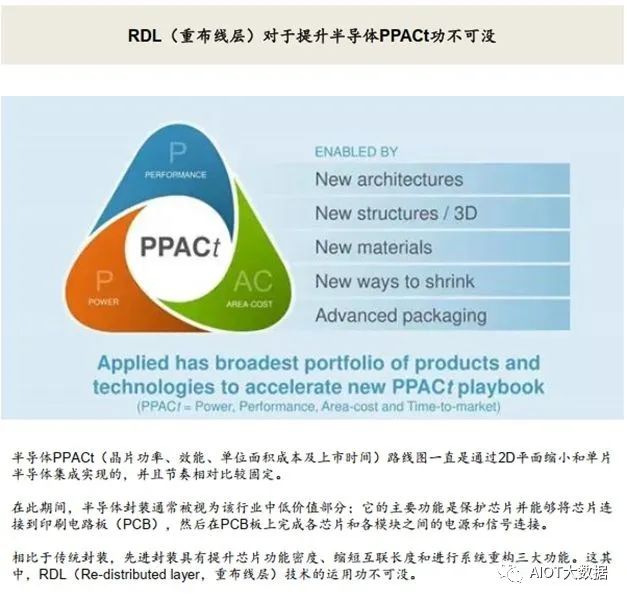

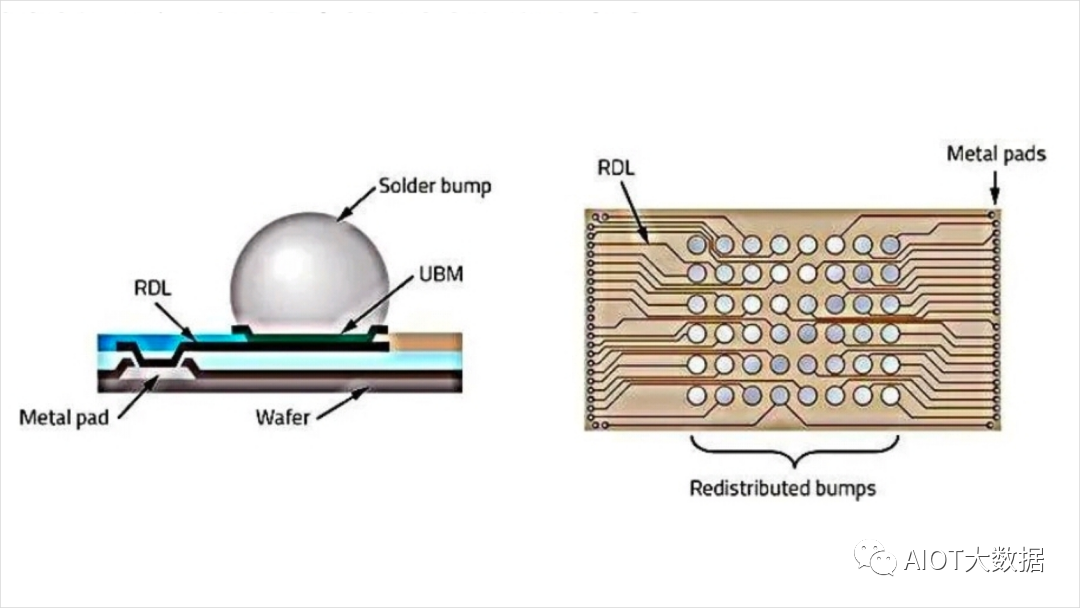

扇出型封装一般是指,晶圆级/面板级封装情境下,封装面积与die不一样,且不需要基板的封装,也就是我们常说的FOWLP/FOPLP。扇出型封装的核心要素就是芯片上的RDL重布线层(可参考下面图表说明),通过RDL替代了传统封装下基板传输信号的作用,使得扇出型封装可以不需要基板而且芯片成品的高度会更低,所以扇出型封装的发明初衷其实是降低成本,而且由于扇出型封装在封装面积上没有扇入那么多限制,整个封装设计也会变得更加灵活和“自由”。因此扇出封装最先在一些小面积、低性能的领域被推广开来。

随着扇出型封装技术自身的发展,越来越多人认识到这个技术不应该只用于低成本低性能领域,它有巨大的潜力,在行业公司不断努力的推动下,扇出型封装今天已经成为了先进封装技术的代表之一,已经可以被广泛用于高性能领域。

经过多年的发展和沉淀,半导体芯片IC封装技术已经越来越成熟,如今已有数百种封装类型。而在这数百种封装类型中,扇出型封装日益火热起来,其更被认为是延续和超越摩尔定律的关键技术方案。

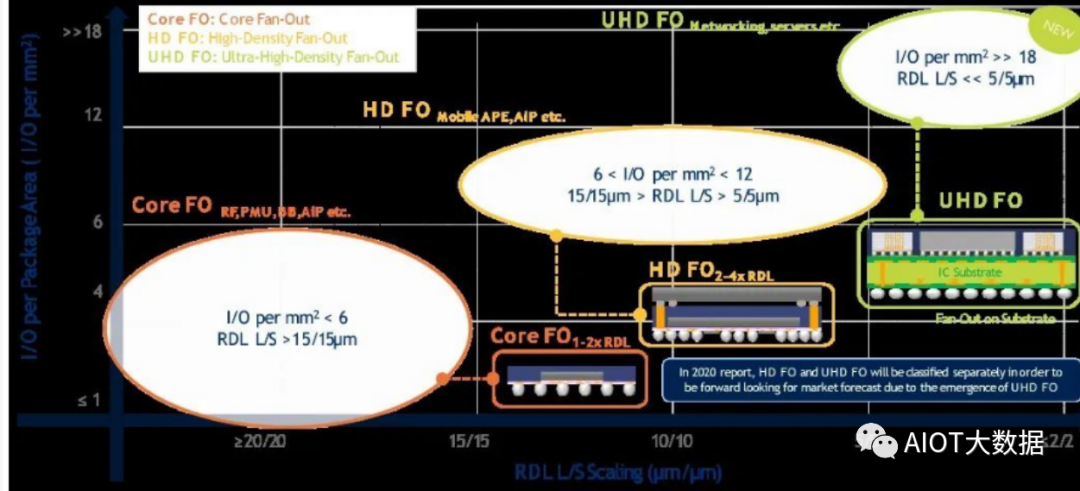

CoreFO,HDFO,UHDFO在I/O以及RDLL/S对比

扇入型封装和扇出型封装区别

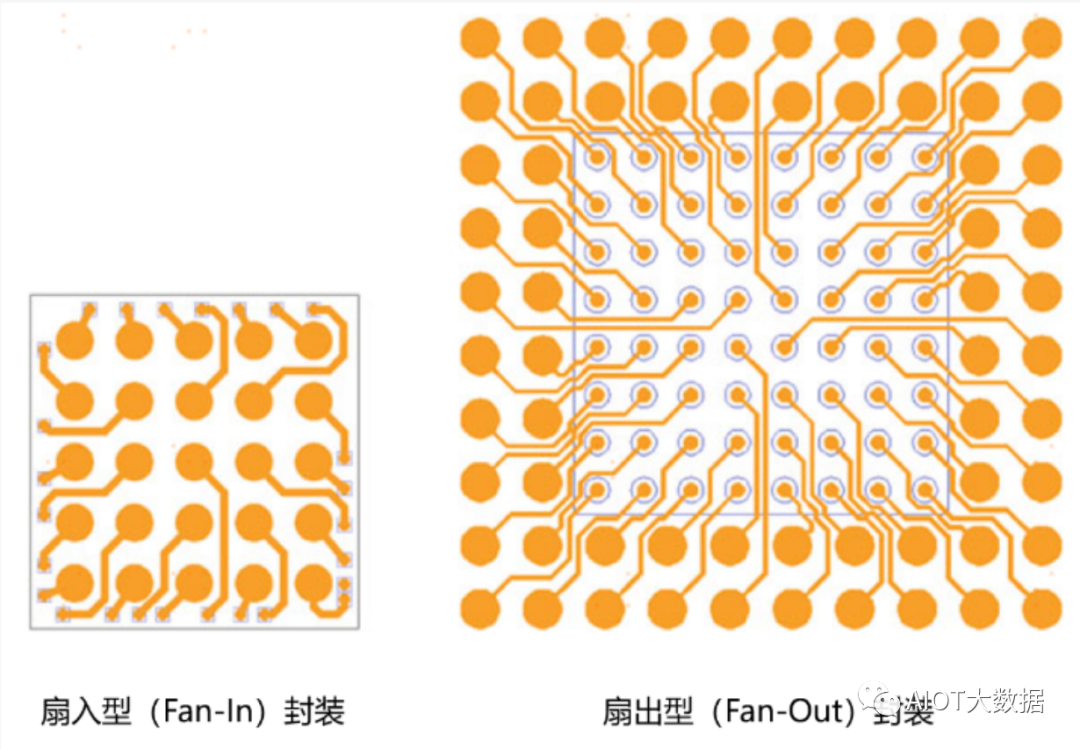

谈到扇出型(Fan-Out)封装,必然会联系到扇入型(Fan-In)封装。扇入型(Fan-In)封装工艺流程大致描述为,整片晶圆芯片进行封装测试,之后再切割成单颗芯片,封装尺寸与芯片尺寸大小相同。

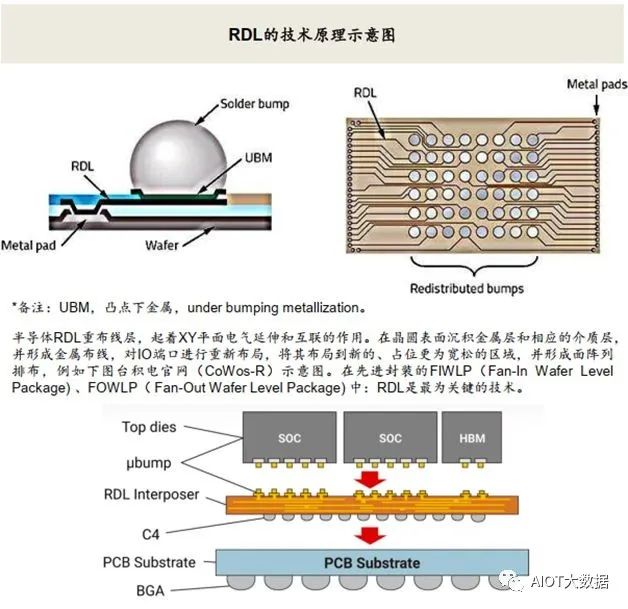

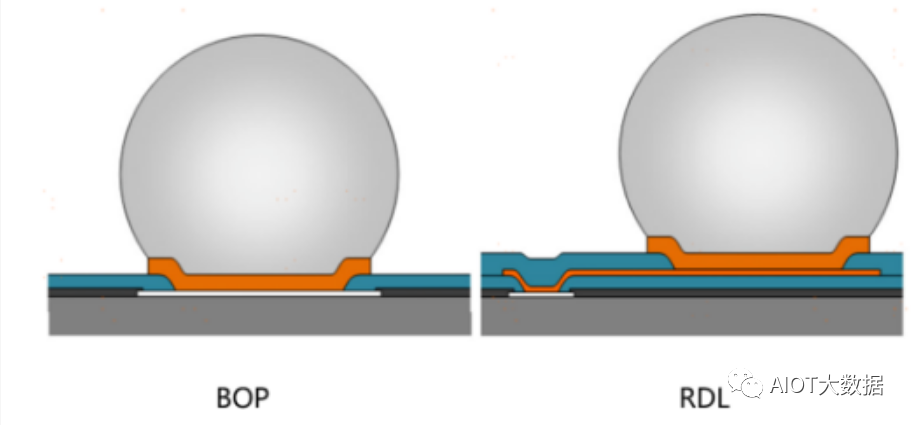

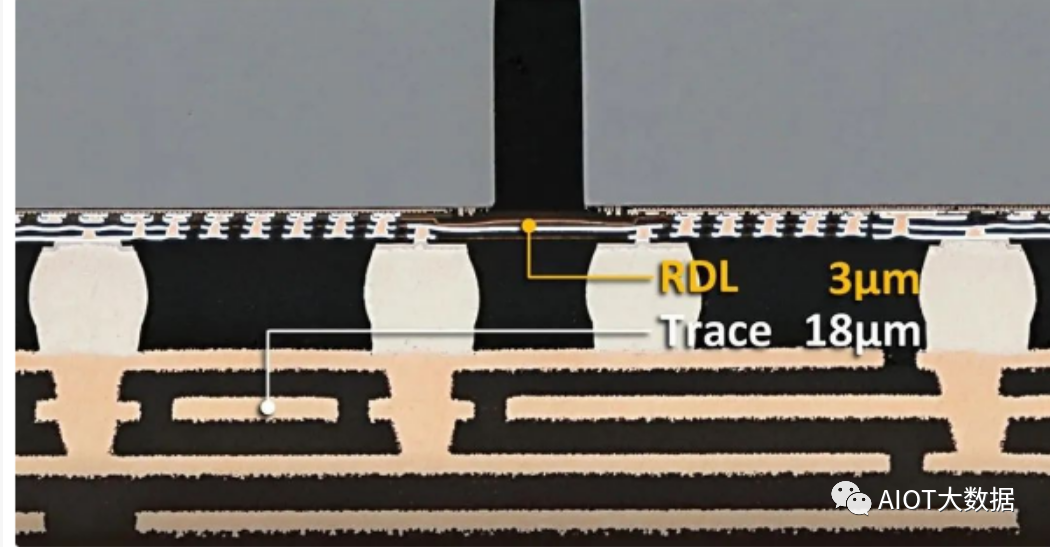

常见的Fan-In(WLCSP)通常可以分为BOP(BumpOnPad)和RDL(RedistribuTIonLayer)。BOP封装结构简单,Bump直接生长在Alpad上;如果Bump位置远离Alpad,则需要通过RDL将Alpad与Bump相连。

随着I/O数量的增加,芯片尺寸无法容纳所有I/O时,扇出型封装由此衍生而来。扇出型封装基于重组技术,芯片被切割完毕后,将芯片重新嵌埋到重组载板(8寸,12寸wafercarrier或者600mmX580mm等大尺寸面板),按照与扇入型封装工艺类似的步骤进行封装测试,然后将重组载板切割为单颗芯片,芯片外的区域为Fan-Out区域,允许将球放在芯片区域外。

扇入型封装和扇出型封装区别两者最大的差异为RDL布线,在扇入型封装中,RDL向内布线,而在扇出型封装中,RDL既可向内又可向外布线,所以扇出型封装可以实现更多的I/O。

扇出型封装细解

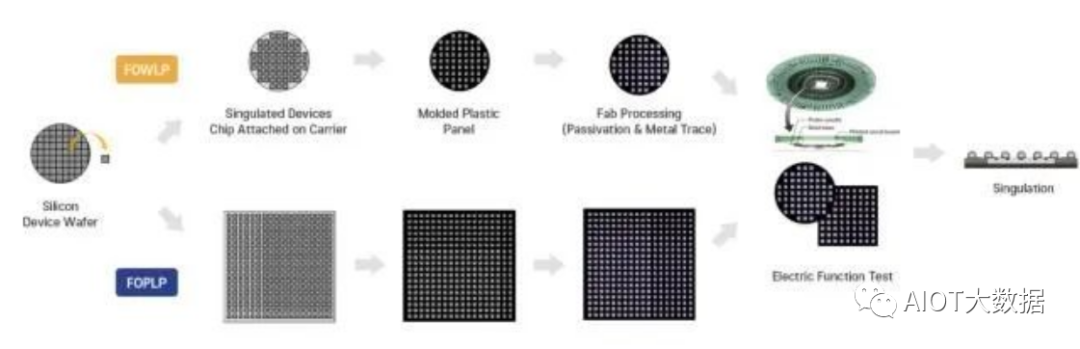

扇出型封装目前存在两大技术分支,即扇出型晶圆级封装(FOWLP)以及扇出型面板级封装(FOPLP)。

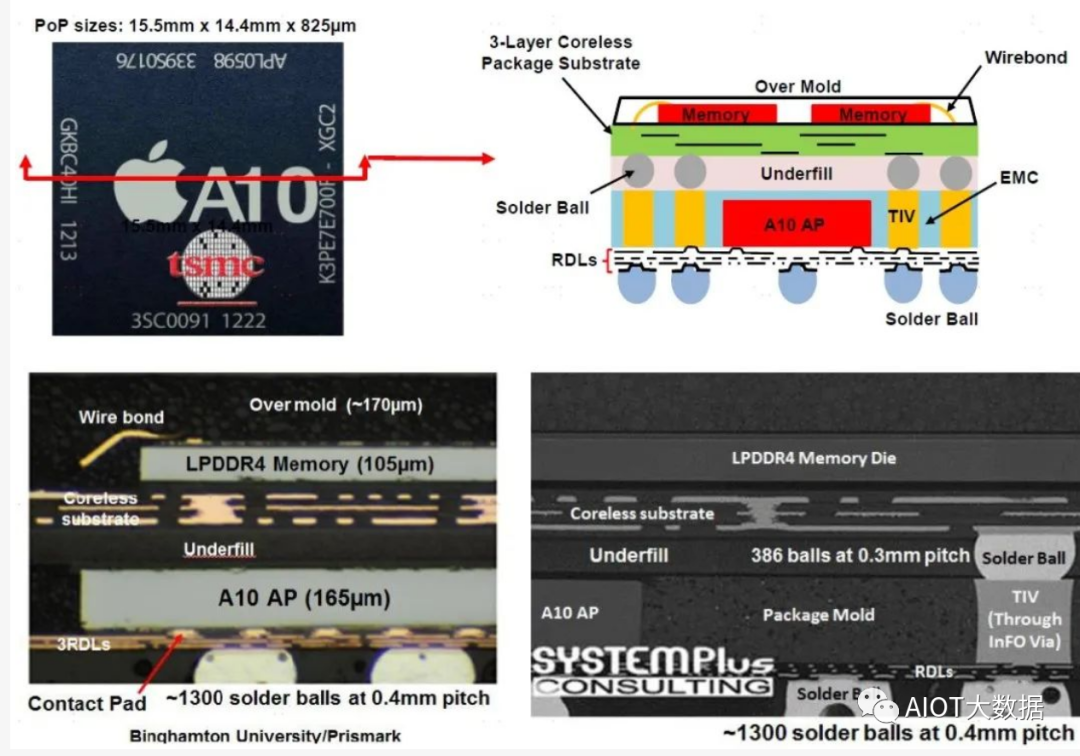

FOWLP封装2009年量产,但彼时只应用于手机基带芯片。真正转折点是2016年,iPhone7系列A10处理器采用TSMC基于FOWLP开发的集成扇出型芯片堆叠(IntegratedFan-OutPackageonPackage,InFO-PoP)封装,此后扇出型(Fan-Out)封装成为热点,各大手机OEM厂商争相追求HDFO(High-DensityFan-Out)封装。

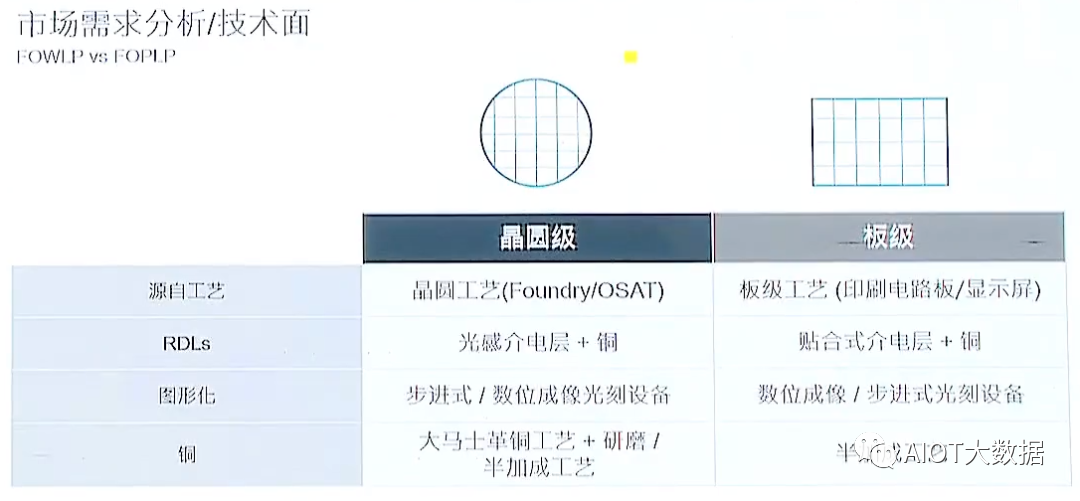

FOWLP与FOPLP工艺对比

iPhone7系列A10处理器InFO-PoP

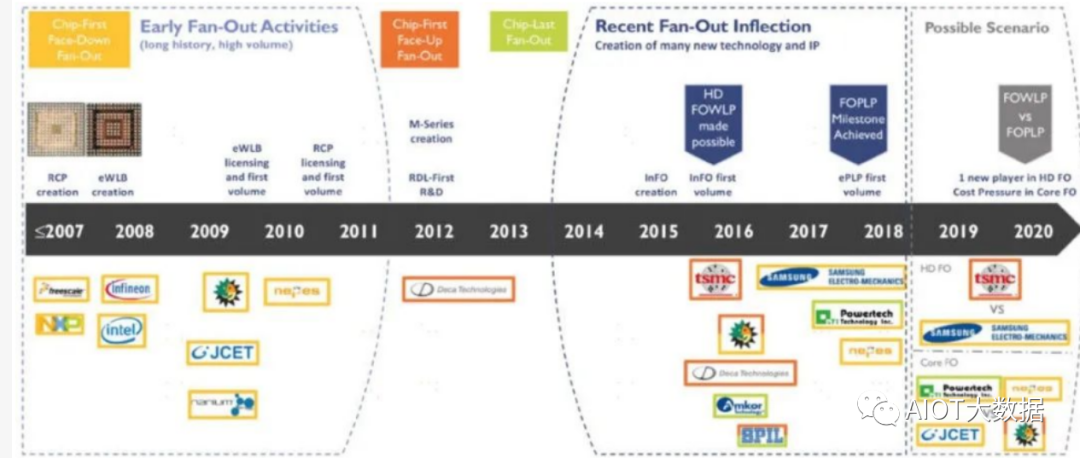

扇出型封装技术演进

FOWLP封装技术

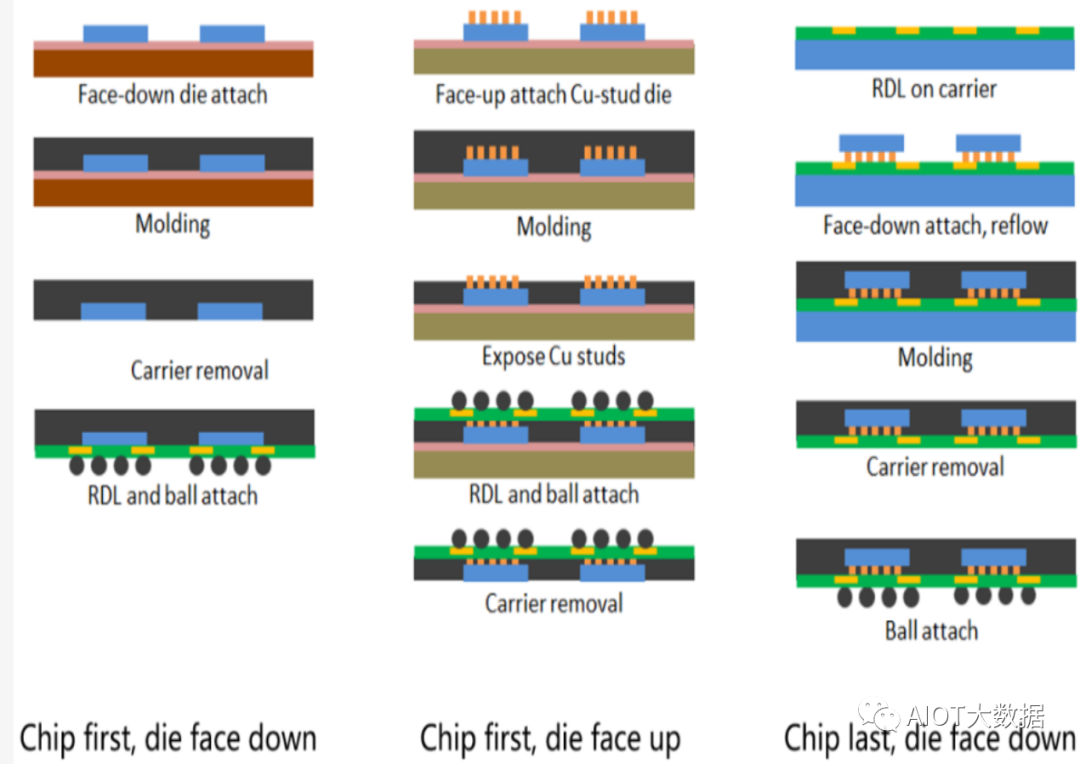

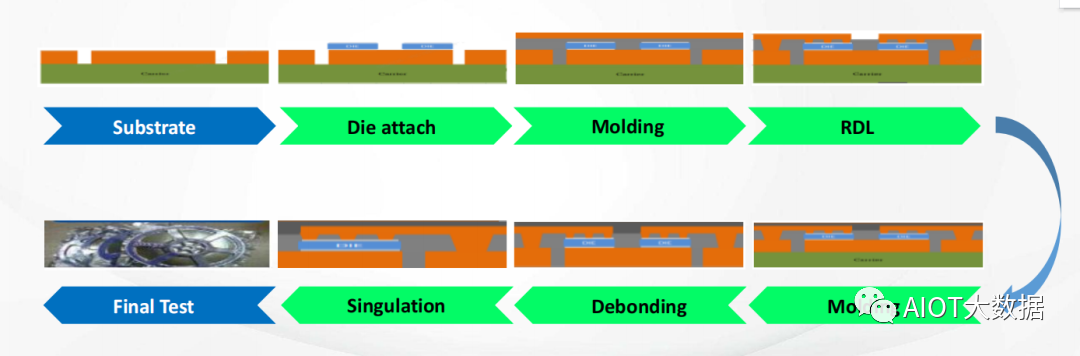

FOWLP封装技术主要分为Chipfirst以及Chiplast,而Chipfirst可再分为Diefaceup(如DecaTechnologiesM-Series封装)以及Diefacedown(RCP以及eWLB封装等),Chiplast形式又被称为RDLfirst,大致封装流程可参考下图:

☆Chipfirst,diefacedown封装技术

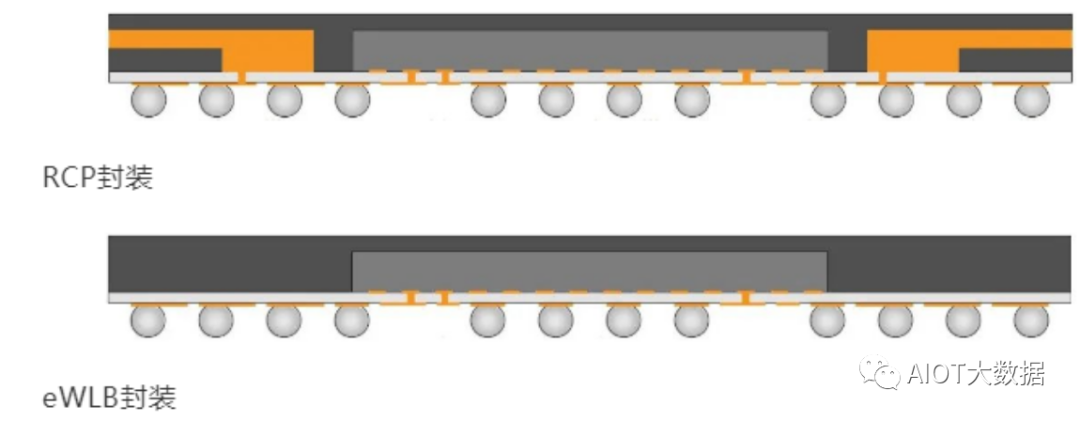

飞思卡尔于2006年左右推出重分布封装(ReconsTItutedChipPackage:RCP),英飞凌于2007年左右推出嵌入式晶圆级BGA(EmbeddedWaferLevelBGA:eWLB)。

RCP与eWLB均为Chipfirst,diefacedown封装,工艺流程类似,与eWLB不同的是,RCP包括一个铜框架层,有助于改善wafermolding过程中芯片偏移,另外可提供电磁屏蔽和散热。

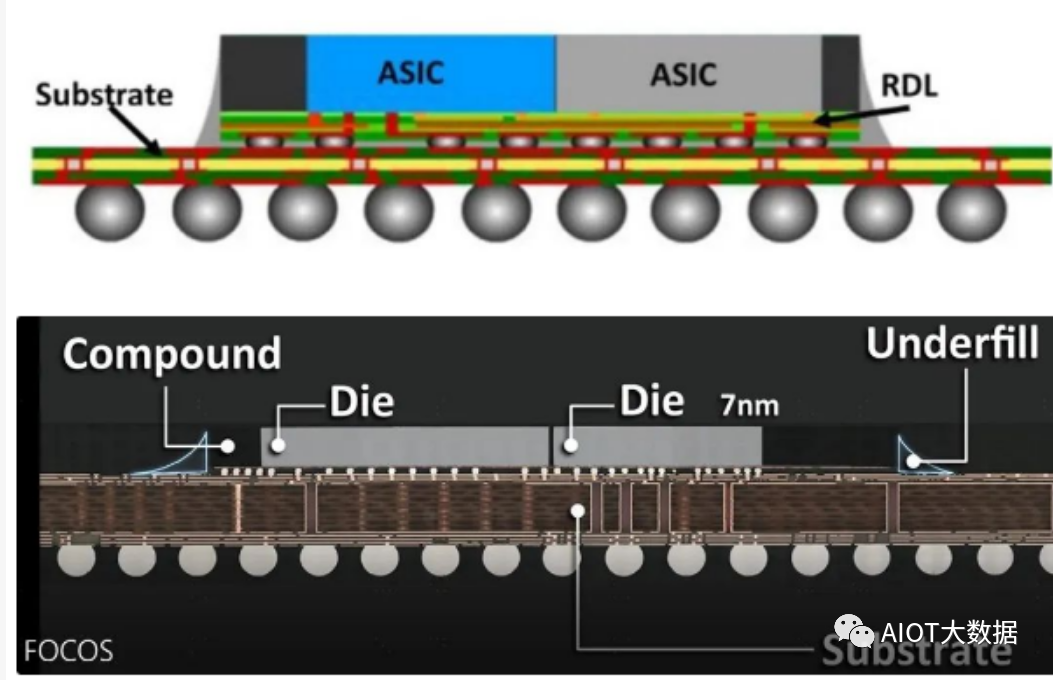

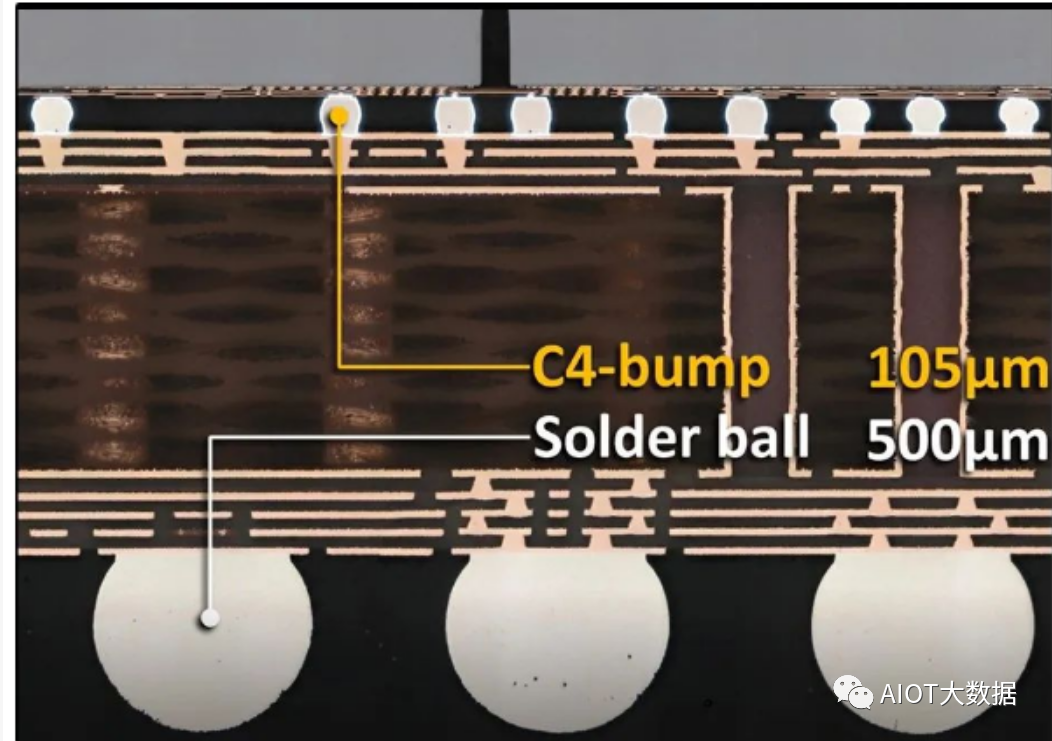

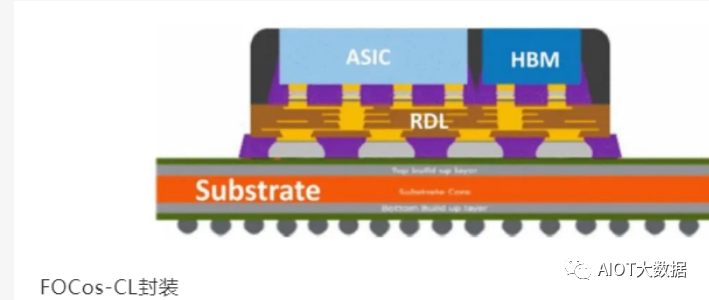

日月光自研的FOCos(Fan-OutChiponSubstrate)封装同样支持Chipfirst,diefacedown封装技术。

FOCos-CF封装

☆Chipfirst,diefaceup封装技术

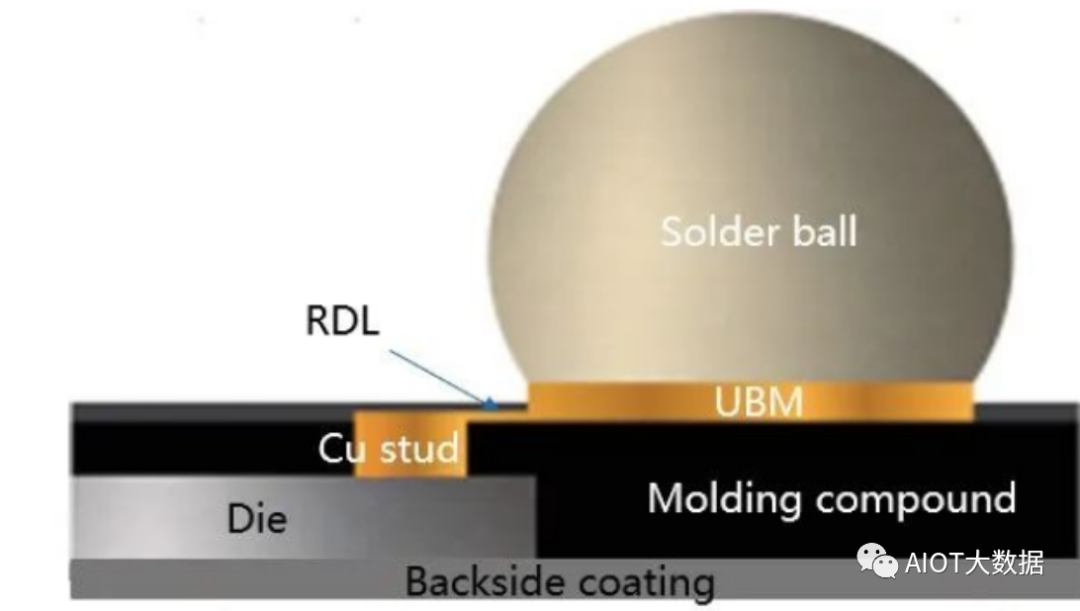

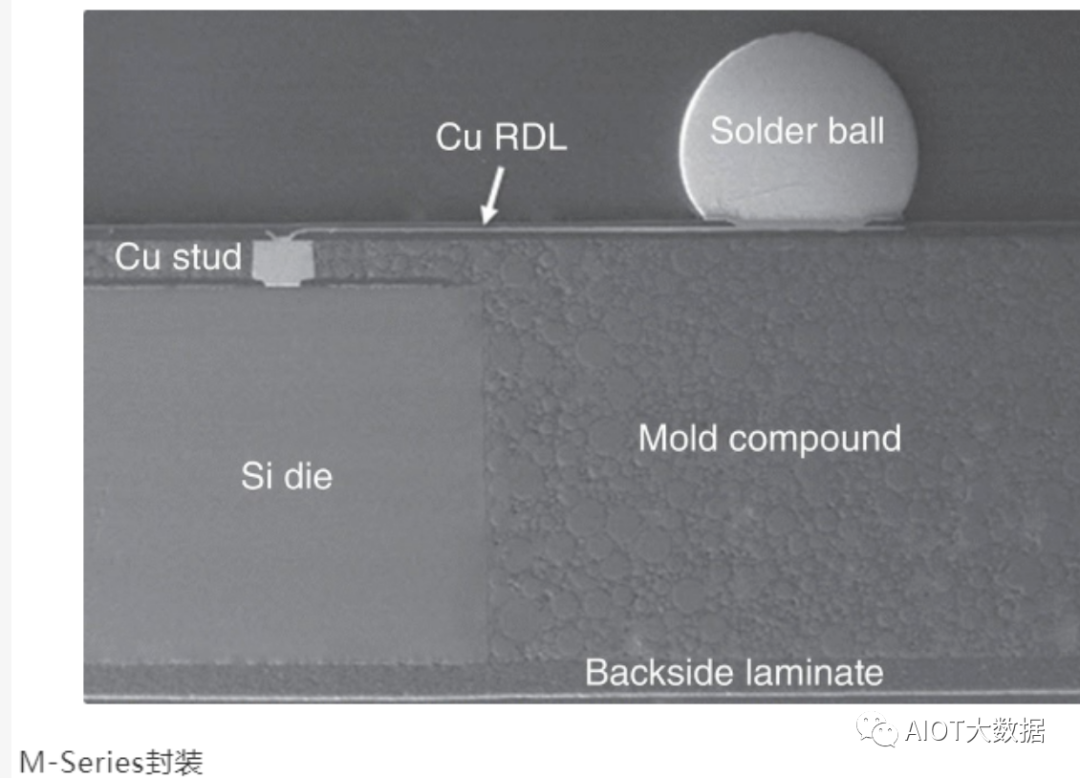

M-Series封装技术由DecaTechnologies提出,TSMC于2016年推出的InFO封装,同样采用Chipfirst,diefaceup封装技术。

Chipfirst,diefaceup主要优点:

(1)芯片背面贴DAF重组,贴装后偏移较小;

(2)芯片背面贴装,避免了Chipfirst,facedown情况下芯片边缘由切割引入的不平整贴装问题;

(3)更加平坦化,Wafermolding后进行Grinding研磨动作,消除了从芯片表面到Moldingcompound表面的不平整性。

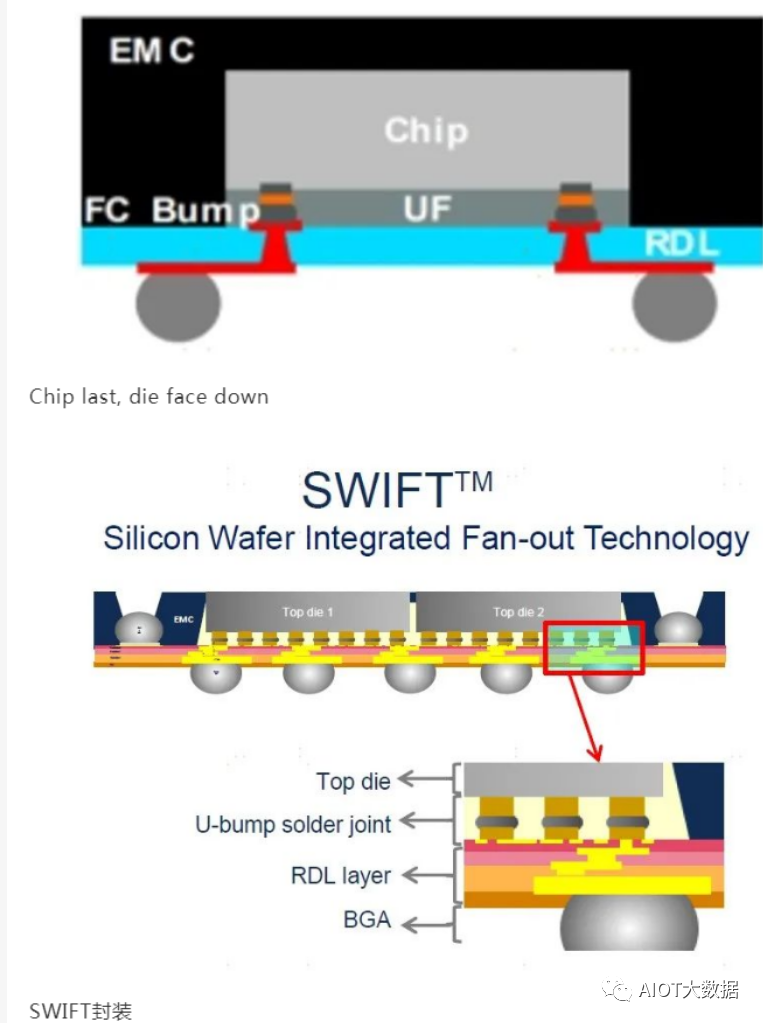

☆Chiplast(orRDLfirst),diefacedown封装形式

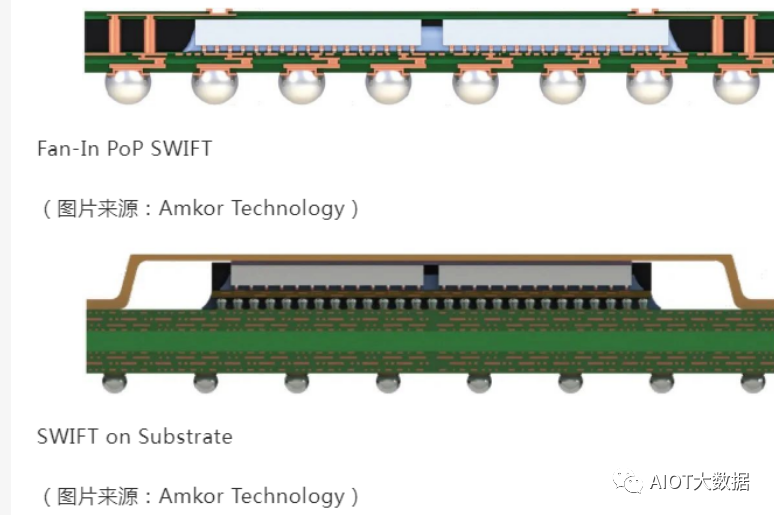

2006年左右由NECElectronicsCorporaTIon提出,Amkor于2015年推出的SWIFT(SiliconWaferIntegratedFan-OutTechnology)封装采用RDLfirst技术,RDL线宽线距能力≤2um,μbumppitch40um,SWIFT封装可实现多芯片集成的3DPOP封装以及无需TSV(TSV-Less)具有成本优势的HDFO高密度扇出型封装,适用于高性能CPU/GPU,FPGA,MobileAP以及MobileBB等。

日月光自研的FOCos(Fan-OutChiponSubstrate)封装同样支持Chiplast,diefacedown封装技术。

Chiplast(orRDLfirst),diefacedown主要优点:

(1)芯片只会在合格的RDL上倒装芯片,可避免芯片损失,适用于高价格的高端芯片;

(2)芯片通过倒装方式直接与RDL连接,消除了芯片偏移问题;

(3)超细RDL线宽线距实现HDFO,RDL线宽线距能力≤2um。

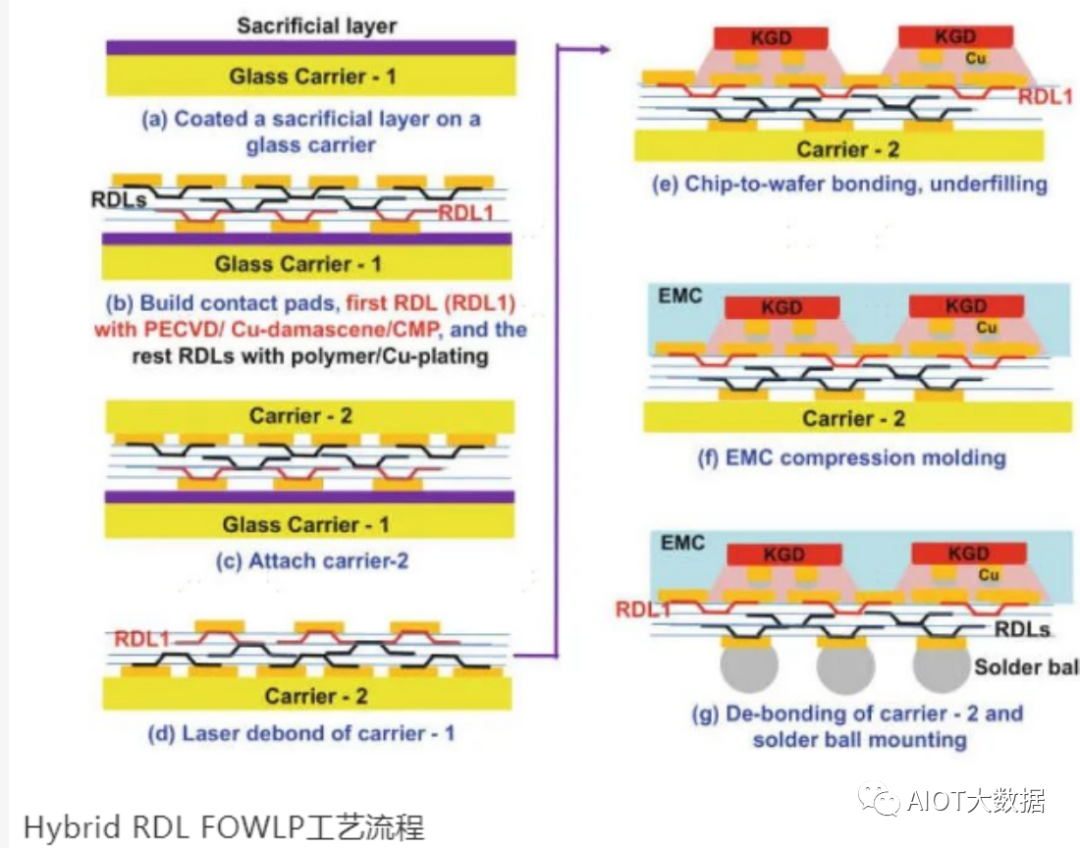

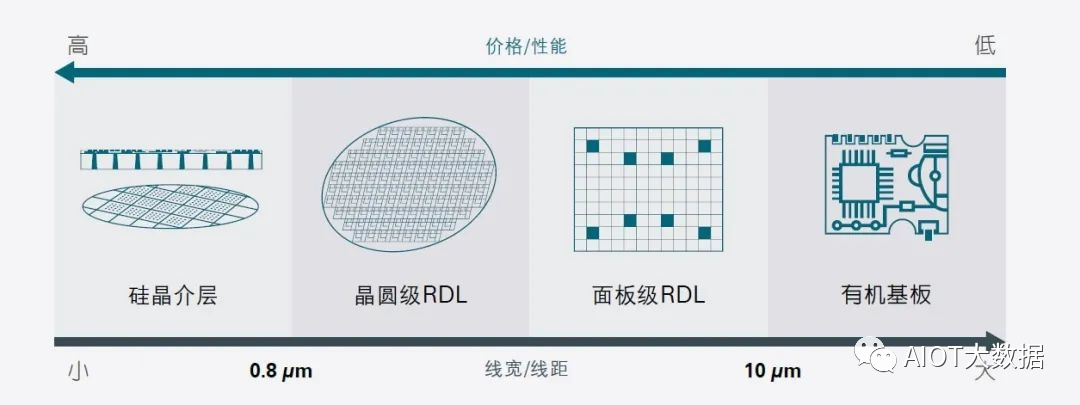

RDL制作方式可分为3种:第一种方式是通过PECVD制作SiO2或者SiN介电层以及Cu大马士革方法制作RDL,RDL线宽线距能力≤2um;第二种方式是通过Polyimide制作介电层以及电镀铜制作RDL,RDL线宽线距能力>2um;第三种方式结合了前两种方式,又称为HybridRDL。

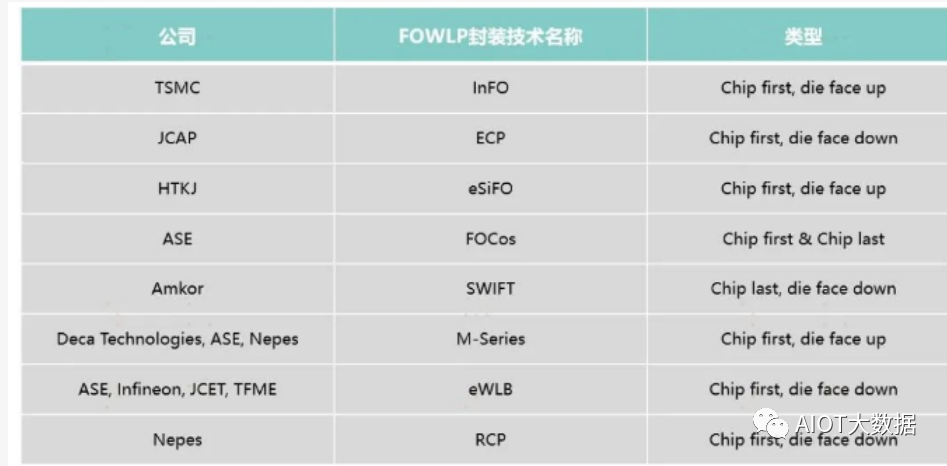

☆支持FOWLP封装技术主流公司

目前业内主流封装厂以及TSMC都基于不同的技术特点开发出各自的FOWLP技术,如下图所示。艾为基于自身产品的特点以及封装厂的技术优势,很早就已经开始关注FOWLP技术,并已经开始在一些产品上采用部分封装厂的FOWLP技术,艾为目前采用FOWLP封装技术的产品主要应用在电压转换器、音频功率放大器、负载开关等。

FOPLP封装技术

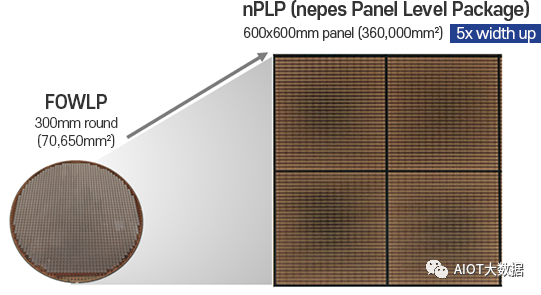

FOPLP封装流程与FOWLP类似,IC载板由8寸/12寸wafercarrier转换为大尺寸面板,以610mmX457mm尺寸面板为例,面积为12寸wafercarrier的3.9倍,单片产出数量为FOWLP的3.9倍,成本优势较大。

FOPLP封装技术的发展保持着高度的关注,目前也已经开始在部分产品上尝试FOPLP技术,在不久的将来也会推出基于FOPLP封装技术的产品。

扇出型(Fan-Out)封装等先进封装成为延续摩尔定律的关键封装技术,也为Chiplet技术提供了很好的基础,可实现芯片体积微小化以及多芯片高密度集成,扇出型(Fan-Out)封装关键挑战点在于更小的微凸块间距(μbumppitch:40um-30um-20um-10um),新型键合方式(TCB&NCP,TCB&NCF,HybridBonding等),以及更大的互连密度(RDLL/S:2/2um-1/1um-0.5/0.5um)。

新突破

随着全球范围内的芯片短缺问题日益严重和地缘政治局势日益紧张,先进封装技术在集成电路封装市场中的地位变得越来越重要。2022年,先进封装市场已经占据了整个集成电路封装市场的48%,并且这个市场份额还在稳步增长。作为后摩尔时代提升芯片性能的关键,先进封装技术的格局正在发生深刻的变化,这可能会给长久以来形成的封装价值链带来一定的风险和挑战。

根据封装技术的不同,Sowotech可以将先进封装主要分为两大类:基于XY平面延伸的先进封装技术和基于Z轴延伸的先进封装技术。在Chiplet级封装中还将其细分为晶圆级封装(WLP)和面板级封装(PLP)。

FOPLP技术是FOWLP技术的延伸,它在更大的方形载板上进行Fan-Out制程,因此被称为FOPLP封装技术。与FOWLP工艺类似,FOPLP技术可以将封装的前后段制程整合在一起,使其成为一次封装制程,从而可以大幅度降低生产和材料的各项成本。

在新兴应用场景的消费支撑下,FOPLP技术因兼具大产能及成本优势,是功率半导体、传感器、通信等车规级/芯片生产的最佳解决方案。电动车持续带动国产车规级芯片市场需求,将促进板级封装技术同步发展。

消费者对电子产品的高便携性和多功能化追求,以及市场对AIoT、5G和智能驾驶IC结构紧凑、性能更好且更具成本效益的需要,导致了先进封装技术的繁荣。过去数年,扇出型封装是成长最为快速的先进封装技术,扇出面板级封装(FOPLP)是晶圆级扇出封装的延伸,正在成为占领有具体需求的新兴市场。

扇出面板级封装(FOPLP)是指将半导体芯片重新分布在大面板上而不是使用单独封装的先进封装技术。FOPLP能够将多个芯片、无源元件和互连集成在一个封装内,与传统封装方法相比,该技术提供了更大的灵活性、可扩展性和成本效益。

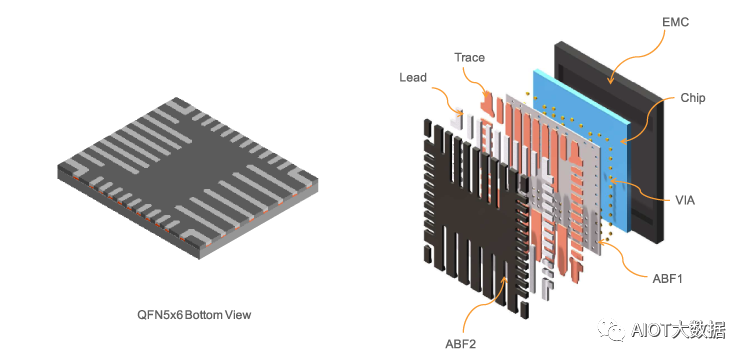

图源:Nepes

图源:Manz

对于FOPLP而言,采用方形面板作为封装载板来代替采用晶圆作为载板封装。这些方形载板的材质可以选择金属、玻璃和高分子聚合物材料。同时FOPLP利用了较大的基板尺寸。

提供具有成本效益的大尺寸互连,面板级有更高的产出效率、更少的物料损耗和更大的有效曝光面积。

就面积利用率而言,FOPLP高达95%,而FOWLP低于85%;

以主流12"/300mm晶圆与300mm正方形玻璃为载具做扇出型封装,方型载具产量为晶圆的1.4倍。再以主流12”晶圆与主流方形载具尺寸约600mm相比,方形载具产量为晶圆的5.7倍;

Yole数据显示,从200mm过渡到300mm大约能节省25%的成本,从300mm过渡到板级,则能节约66%的成本。

现阶段不需要最先进制程和设备,也不需要太细的线宽/线距;

FOPLP还具有多种性能优势,例如更高的器件密度、改进的电气性能和增强的热管理。

板级封装相比传统封装在提升性能的同时,能够大幅降低成本,因此板级封装会代替传统封装成为Sensor、功率IC、射频、链接模块、PMIC等的最佳解决方案,如汽车中约66%的芯片价值可以使用FOPLP技术生产,是车规级芯片生产的出色解决方案。FOPLP技术具备巨大的成长潜力,预计未来几年将出现显著扩张,Yole数据显示,2022年FOPLP的市场空间大约是11.8亿美元,预计到2026年将增长到43.6亿美元。

面板封装产品结构图源:华润微

面板封装扇出简要工艺流程图源:中科四合

审核编辑:汤梓红

-

扇出型晶圆级封装技术介绍2026-04-10 876

-

扇入型晶圆级封装技术介绍2026-03-09 658

-

晶圆级扇出型封装的三大核心工艺流程2026-02-03 1421

-

扇出型晶圆级封装技术的概念和应用2026-01-04 2194

-

什么是晶圆级扇出封装技术2025-06-05 2891

-

扇入型和扇出型晶圆级封装的区别2024-07-19 3565

-

扇出型封装晶圆级封装可靠性问题与思考2024-04-07 3357

-

扇出型晶圆级封装技术的优势分析2023-10-25 2224

-

一文详解扇出型晶圆级封装技术2023-09-25 3581

-

日月光扇出型封装结构有效提升计算性能2022-11-23 935

-

WLCSP/扇入封装技术和市场动态2021-01-08 12279

-

用于扇出型晶圆级封装的铜电沉积2020-07-07 2894

-

FPGA Fanout-Fanin(扇入扇出)资料解析2017-11-18 18161

-

扇出型封装技术的发展历史及其优势详解2017-09-25 2110

全部0条评论

快来发表一下你的评论吧 !