新型沟槽SiC基MOSFET器件研究

描述

SiC具有高效节能、稳定性好、工作频率高、能量密度高等优势,SiC沟槽MOSFET(UMOSFET)具有高温工作能力、低开关损耗、低导通损耗、快速开关速度等特点,在新能源发电、电动汽车、工业自动化、航空航天等领域具有广泛应用前景。随着SiC材料和制造工艺的进一步发展和成熟,SiC沟槽MOSFET有望取得更大的突破和应用。

近日,第九届国际第三代半导体论坛(IFWS)&第二十届中国国际半导体照明论坛(SSLCHINA)于厦门召开。期间,“碳化硅功率器件及其封装技术”分会上,厦门大学张峰教授做了“新型沟槽SiC基MOSFET器件研究”的主题报告,分享了最新研究进展,涉及SiC MOSFET器件研究进展、SiC UMOSFET研究进展、SiC UMOSFET新结构器件等。

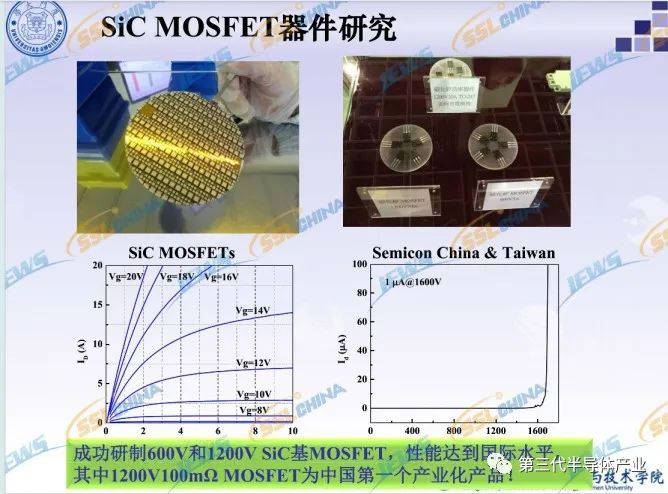

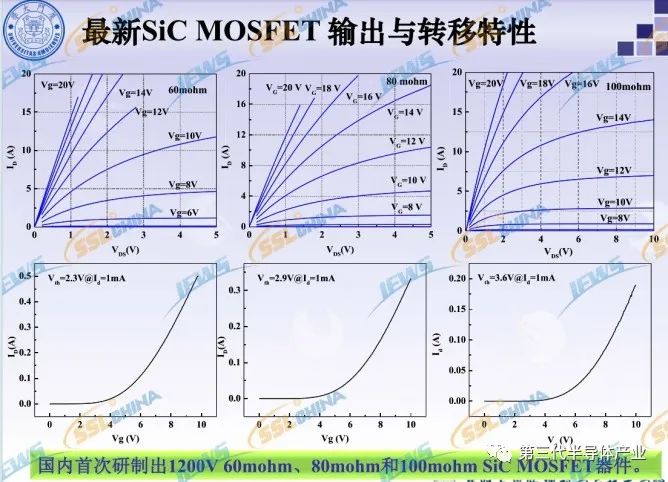

报告指出,SiC MOSFET器件研究方面,成功研制600V和1200V SiC基MOSFET,性能达到国际水平。国内首次研制出1200V 60mohm、80mohm和100mohm SiC MOSFET器件。目前SiC MOSFET的问题涉及栅氧化层的可靠性仍然是SiC MOSFET器件需要解决的关键问题;阈值电压Vth随温度提高下降;栅压非对称性(如-10V—25V);DMOSFET器件沟道迁移率较低,通态电阻较高;UMOSFET器件可靠性亟需提高;1200V以下,沟槽MOSFET将是未来SiC MOSFET器件的发展方向。

从SiC UMOSFET国内外进展来看,SiC UMOSFET在降低比导通电阻和晶圆成本方面更具优势。1200V SiC MOSFET需要5μm以下元胞尺寸。大电流芯片良率降低导致芯片每安培成本居高不下,约为Si IGBT 2-3倍。提高可靠性是未来SiC UMOSFET器件的发展趋势。

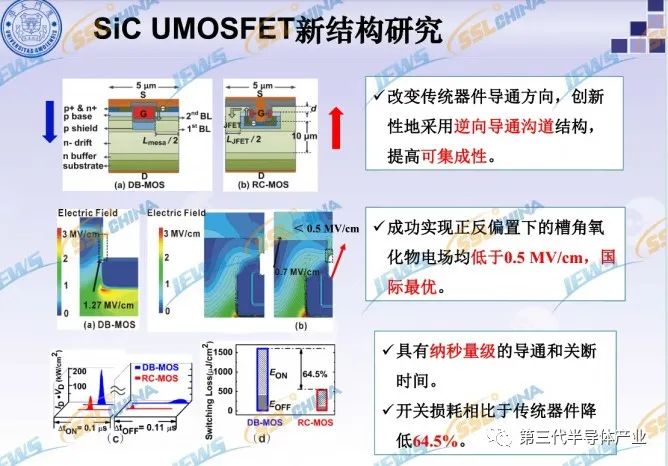

SiC UMOSFET新结构研究方面,涉及改变传统器件导通方向,创新性地采用逆向导通沟道结构,提高可集成性。成功实现正反偏置下的主沟槽槽角氧化物电场均低于0.5 MV/cm,国际领先。具有纳秒量级的导通和关断时间。开关损耗相比于传统器件降低64.5%等。报告中分享了半超结沟槽MOSFET的设计、埋层超结沟槽MOSFET的设计等。

其中,半超结构沟槽MOSFET的设计研究显示,击穿特性与电场分布方面,超结耗尽缓解了屏蔽层拐角处的电场拥挤效应,使GSS-UMOS和NGSS-UMOS的耐压能力分别提升了41%和23%。

米勒电容(电荷)方面,当超结接地时,超结充分耗尽使米勒电容下降了66%,米勒电荷下降了59%。超结浮空时,超结耗尽程度大幅降低引起米勒电容和米勒电荷的增大。

开关特性方面,米勒电容与米勒电荷的下降使器件具有更快的开关时间和更低的开关损耗。开关频率为33 kHz时,GSS-UMOS的开关时间快了25 ns。开关频率为50 kHz时,GSS-UMOS的开关时间快了21 ns。

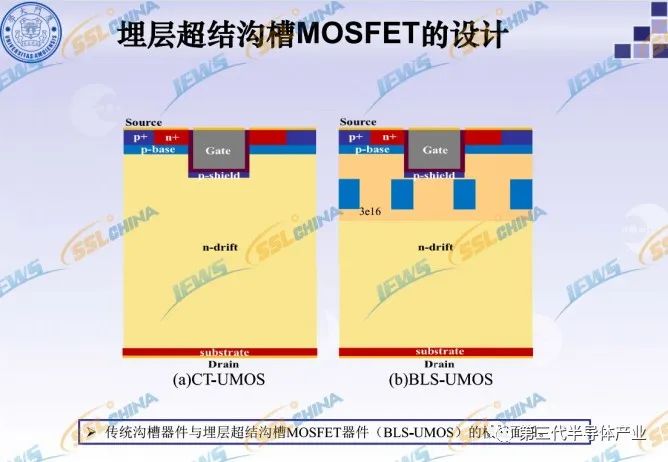

开关特性(损耗)方面,米勒电容与米勒电荷的下降使器件具有更快的开关时间和更低的开关损耗。开关频率为75 kHz时,GSS-UMOS的开关时间加快了25 ns。开关频率的升高使得器件的开关转换效率降低。埋层超结沟槽MOSFET的设计研究显示,转移、输出特性方面,电流传输层使器件反型层沟道加快形成,降低了器件的阈值电压。传输层使器件的电流密度增大,使比导通电阻下降35%。

电流密度方面,CT-UMOS的饱和电流密度为2.7e5 A/cm2,BLS-UMOS的饱和电流密度为5.1e5 A/cm2。高掺杂的N传输层能够更高的电流密度。

击穿特性与电场强度方面,P埋层的耗尽使BLS-UMOS的耐压能力提升40%,同时改善了器件栅极氧化层的可靠性。

米勒电容(电荷)方面,BLS-UMOS埋层与传输层耗尽产生的屏蔽作用,使米勒电容下降40%,米勒电荷下降26%。

审核编辑:刘清

-

沟槽型SiC MOSFET的结构和应用2025-02-02 2643

-

SiC功率器件中的沟槽结构测量2024-10-16 1576

-

沟槽结构SiC MOSFET常见的类型2023-04-01 3612

-

SiC MOSFET的器件演变与技术优势2023-02-27 1544

-

沟槽结构SiC MOSFET几种常见的类型2023-02-16 3623

-

第三代双沟槽结构SiC-MOSFET介绍2023-02-08 3342

-

SiC-MOSFET器件结构和特征2023-02-07 1569

-

SiC MOSFET真的有必要使用沟槽栅吗?2023-01-12 2483

-

【罗姆SiC-MOSFET 试用体验连载】SiC MOSFET元器件性能研究2020-04-24 2154

-

浅析SiC-MOSFET2019-09-17 6418

-

SiC功率器件SiC-MOSFET的特点2019-05-07 5695

-

沟槽结构SiC-MOSFET与实际产品2018-12-05 4843

-

SiC-MOSFET与Si-MOSFET的区别2018-11-30 11048

-

SiC-MOSFET的应用实例2018-11-27 6062

全部0条评论

快来发表一下你的评论吧 !