资料下载

×

基于FPGA数字频率计的设计

消耗积分:1 |

格式:doc |

大小:229KB |

2017-08-04

数字频率计设计要点,代码(电子设计竞赛编程、写论文时可用)

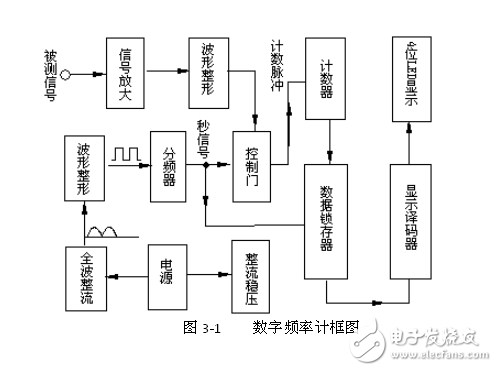

2 对FPGA数字频率计的制作规划

2.1 设计的目的

掌握VHDL语言的基本结构及编程思想,掌握数字频率计的工作原理,掌握数字频率计的VHDL语言编程方法。

2.2 数字频率计的基本原理

数字频率计的主要功能是测量周期信号的频率。频率是单位时间( 1S )内信号发生周期变化的次数。如果我们能在给定的 1S 时间内对信号波形计数,并将计数结果显示出来,就能读取被测信号的频率。数字频率计首先必须获得相对稳定与准确的时间,同时将被测信号转换成幅度与波形均能被数字电路识别的脉冲信号,然后通过计数器计算这一段时间间隔内的脉冲个数,将其换算后显示出来[3]。这就是数字频率计的基本原理。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章