资料下载

×

DBPL编码信号的信号源系统设计方案解析

消耗积分:1 |

格式:rar |

大小:0.4 MB |

2017-10-19

引言

DBPL(Differential BiPhase Level)编码是一种超越传统数字传输极限的编码方式[1]。DBPL编码被广泛应用于以太网、工程测井仪器和铁路应答器等工程应用中。在铁路应答器中,通过DBPL编码传输信号给列车车载处理器,实现对列车运行的控制。

本文设计了一种基于AT89LV51单片机控制的DBPL编码信号的信号源系统,能够产生DBPL编码信号;同时设计了系统的电源管理模块,保证系统的正常供电。

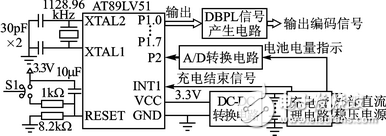

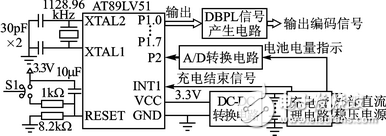

1 信号源系统的设计

该信号源由时钟复位模块、DBPL信号产生电路、DCDC转换电路、充电管理电路和A/D转换电路组成。单片机AT89LV51控制编码模块产生DBPL信号;充电管理电路对系统所用电池进行充电管理,保证电池的充分充电;DCDC转换电路为单片机以及编码逻辑产生稳定电压的供电;A/D转换电路采集电池电量信息,并告知单片机处理。信号源系统设计框图如图1所示。

图1 信号源系统设计框图

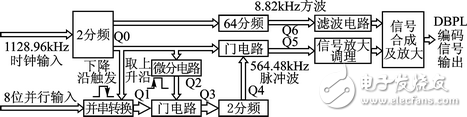

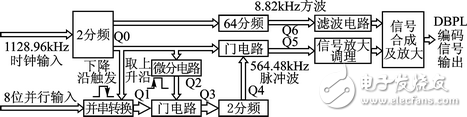

1.1 DBPL信号产生电路

本设计中,DBPL信号[2]由作为能量载波的正弦波与脉冲编码信号合成。脉冲编码信号采用DBPL编码,平均传输速率为564.48 kb/s;能量载波为正弦波,信号频率为8.82 kHz。该模块的输入为8位待编码的并行二进制数据,与AT89LV51单片机的P1.0~P1.7相接,由单片机控制提供输入。DBPL信号产生电路原理图如图2所示。

图2 DBPL信号产生电路原理图

其中,并行转串行电路采用一片8位并串转换移位寄存器74166和一片计数器74163,计数器74163采用模8计数。当计数器计满8个数时,清零计数器,重新开始计数;计数期间,8位并行数据按照时钟节拍输出。2分频及64分频采用计数器74163实现。微分电路采用D触发器及门电路实现。并串转换输出Q1经过非门与微分电路取得的上升沿Q2相与,得出Q3,经过D触发器实现2分频输出Q4,最后Q0与Q4异或求得编码输出。输出8.82 kHz的方波和564.48 kHz的脉冲波,再分别进行滤波、放大调理,然后合成为最终所要得到的DBPL信号。

DBPL(Differential BiPhase Level)编码是一种超越传统数字传输极限的编码方式[1]。DBPL编码被广泛应用于以太网、工程测井仪器和铁路应答器等工程应用中。在铁路应答器中,通过DBPL编码传输信号给列车车载处理器,实现对列车运行的控制。

本文设计了一种基于AT89LV51单片机控制的DBPL编码信号的信号源系统,能够产生DBPL编码信号;同时设计了系统的电源管理模块,保证系统的正常供电。

1 信号源系统的设计

该信号源由时钟复位模块、DBPL信号产生电路、DCDC转换电路、充电管理电路和A/D转换电路组成。单片机AT89LV51控制编码模块产生DBPL信号;充电管理电路对系统所用电池进行充电管理,保证电池的充分充电;DCDC转换电路为单片机以及编码逻辑产生稳定电压的供电;A/D转换电路采集电池电量信息,并告知单片机处理。信号源系统设计框图如图1所示。

图1 信号源系统设计框图

1.1 DBPL信号产生电路

本设计中,DBPL信号[2]由作为能量载波的正弦波与脉冲编码信号合成。脉冲编码信号采用DBPL编码,平均传输速率为564.48 kb/s;能量载波为正弦波,信号频率为8.82 kHz。该模块的输入为8位待编码的并行二进制数据,与AT89LV51单片机的P1.0~P1.7相接,由单片机控制提供输入。DBPL信号产生电路原理图如图2所示。

图2 DBPL信号产生电路原理图

其中,并行转串行电路采用一片8位并串转换移位寄存器74166和一片计数器74163,计数器74163采用模8计数。当计数器计满8个数时,清零计数器,重新开始计数;计数期间,8位并行数据按照时钟节拍输出。2分频及64分频采用计数器74163实现。微分电路采用D触发器及门电路实现。并串转换输出Q1经过非门与微分电路取得的上升沿Q2相与,得出Q3,经过D触发器实现2分频输出Q4,最后Q0与Q4异或求得编码输出。输出8.82 kHz的方波和564.48 kHz的脉冲波,再分别进行滤波、放大调理,然后合成为最终所要得到的DBPL信号。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章