资料下载

×

ARM与DSP双核组成的OMAP5910嵌入式系统分析

消耗积分:1 |

格式:rar |

大小:0.4 MB |

2017-10-25

开放式多媒体应用平台(Open Multimedia Application Platform,OMAP)处理器系列包括应用处理器及集成的基带应用处理器,具有高性能、实时处理及超低功耗的特点,广泛应用于PDA、Web记事本、远程通信和医疗器械等。

OMAP5910处理器是由TI公司的应用最为广泛的TMS320C55x DSP内核与低功耗、增强型ARM925微处理器组成的双核应用处理器,是OMAP系列的最新成员。TMS320C55x系列可提供对低功耗应用的实时多媒体处理的支持,而ARM925 MPU 可满足控制和接口方面的处理需要。OMAP5910处理器同时拥有二种产品的最佳性能,包括TI TMS320C55x DSP内核的实时处理性能与低功耗、TI增强型ARM925微处理器的灵活性,且通过优化处理器间的通信机制,使设计者可同时享受这二种处理器的最大优点。基于双核结构,OMAP5910具有极强的运算能力和极低的功耗,一方面产品性能高、省电,另一方面同其他OMAP处理器一样,采用开放式、易于开发的软件设施,支持广泛的操作系统,如Linux、Windows、WinCE、Nucleus、Palm OS、VxWorks、Java等。此外,还可以通过API及用户熟悉且易于使用的工具优化其应用程序。

1 OMAP5910的结构及特点

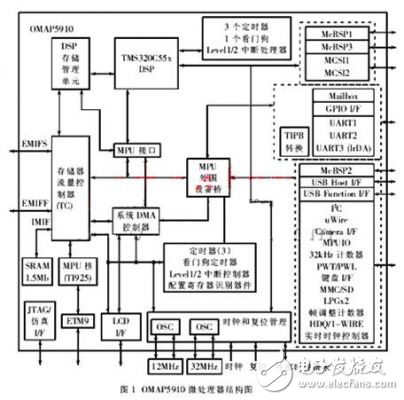

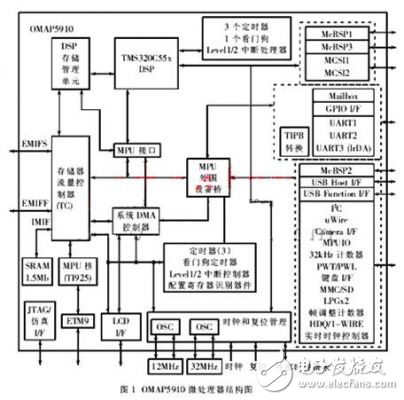

OMAP的结构图如图1所示。

1.1 OMAP5910处理器的主要特点

(1)高性能。采用低功耗、高性能的32位ARM9TDMI内核和TMS320-C55x DSP内核,工作频率高达150MHz;采用5级的整数流水线结构;支持多媒体处理技术,采用的是TMS320C55x DSP内核,增强了对视频和音频的解码能力。

(2)低功耗。多电源管理模式,双内核电压供给为1.6V;ARM9TDMI内核具有16KB指令和8KB数据Cache,TMS320C55x DSP内核具有24KB的指令Cache;支持2.75V的存储器和3.3V的I/O接口。

(3)I/O扩展。有4个16位的FLASH/SRAM的存储空间,1个16位的SDRAM存储空间。

(4)外围控制接口。9通道系统可配置DMA控制器;LCD控制器,支持专用的LCD DMA方式,并支持STN(passive monochrome,俗称单彩)、TFT(active color,俗称真彩)、STN(passive color,俗称伪彩)显示;串行端口(3个UARTs、IrDA、I2C、3个McBSPs、2个MCSIs、MicrowireTM、PWT、PWL、uWire、HDQ/1-Wire);USB接口;支持MMC/SD卡。

(5)时钟控制。时钟源:32.768kHz的振荡器;12MHz/13MHz的振荡器;可编程的内核锁相环。

(6)电源管理。Awake模式(正常运行模式)、Big-sleep模式(省电模式)、Deep-sleep(省电模式)模式。

(7)封装形式。289脚GZG BGA封装或GDY BGA封装。1.2 TI925T(ARM9TDMI)内核

TI925T(ARM9TDMI)内核是采用5阶段管道化流水线32位的RISC处理器架构的体系结构,并采用ARM9作内核,同时配备Thumb扩展。它能够处理32位或者16位的指令和8位、16位、32位的数据。这款新型高性能、低功耗的微构架兼容ARMv4T指令集,并通过采用协处理器CP15使体系结构得到增强。系统中的控制寄存器可通过对协处理器CP15的读写来对MMU、Cache和读写缓存控制器进行存取操作。这种微构架在ARM核的周围提供了:指令与数据存储器管理单元,指令、数据和写缓冲器,性能监控、调试和JTAG单元以及协处理器接口,MAC协处理器和内核存储总线。

TI925T 的MMU具有2个64个项的转换旁路缓存器(TLB)用于指令和数据流,每项均可映射存储器的段、大页和小页。为了保证内核周期的存取指令和数据,TI925T包含了分别独立的1个16KB的指令Cache和8KB的数据Cache。二者独立的好处是可以在同一时钟周期内读取指令和数据,而不需要双端口的Cache。指令和数据Cache都是2路相互关联的Cache,以16B为1块进行操作,并采用最小最近使用(LRU)算法以刷新存储。另外,TI925T还提供了写缓冲的性能用于提升内核,其能够缓冲数据的容量高达17字。

1.3 TMS320C55x内核

TMS320C55x内核的主要特点是:有1个64×8位的缓存队列(Instruction Buffer Queue),2个17位×17位的乘法累加单元(MAC),1个40位的算术逻辑单元(ALU),1个16位的算术逻辑单元,1个40位的桶形移位器(Barrel Shifter)和4个40位的加法器。另外还有12条独立的总线,即:3条数据读总线,2条数据写总线,5条数据地址总线,1条程序读取总线和1条程序地址总线。此外,还有用户可以配置的IDLE域。内核主要由4个单元组成:指令缓冲单元(I单元)、程序流单元(P单元)、地址数据流单元(A单元)和数据运算单元(D单元)。

OMAP5910处理器是由TI公司的应用最为广泛的TMS320C55x DSP内核与低功耗、增强型ARM925微处理器组成的双核应用处理器,是OMAP系列的最新成员。TMS320C55x系列可提供对低功耗应用的实时多媒体处理的支持,而ARM925 MPU 可满足控制和接口方面的处理需要。OMAP5910处理器同时拥有二种产品的最佳性能,包括TI TMS320C55x DSP内核的实时处理性能与低功耗、TI增强型ARM925微处理器的灵活性,且通过优化处理器间的通信机制,使设计者可同时享受这二种处理器的最大优点。基于双核结构,OMAP5910具有极强的运算能力和极低的功耗,一方面产品性能高、省电,另一方面同其他OMAP处理器一样,采用开放式、易于开发的软件设施,支持广泛的操作系统,如Linux、Windows、WinCE、Nucleus、Palm OS、VxWorks、Java等。此外,还可以通过API及用户熟悉且易于使用的工具优化其应用程序。

1 OMAP5910的结构及特点

OMAP的结构图如图1所示。

1.1 OMAP5910处理器的主要特点

(1)高性能。采用低功耗、高性能的32位ARM9TDMI内核和TMS320-C55x DSP内核,工作频率高达150MHz;采用5级的整数流水线结构;支持多媒体处理技术,采用的是TMS320C55x DSP内核,增强了对视频和音频的解码能力。

(2)低功耗。多电源管理模式,双内核电压供给为1.6V;ARM9TDMI内核具有16KB指令和8KB数据Cache,TMS320C55x DSP内核具有24KB的指令Cache;支持2.75V的存储器和3.3V的I/O接口。

(3)I/O扩展。有4个16位的FLASH/SRAM的存储空间,1个16位的SDRAM存储空间。

(4)外围控制接口。9通道系统可配置DMA控制器;LCD控制器,支持专用的LCD DMA方式,并支持STN(passive monochrome,俗称单彩)、TFT(active color,俗称真彩)、STN(passive color,俗称伪彩)显示;串行端口(3个UARTs、IrDA、I2C、3个McBSPs、2个MCSIs、MicrowireTM、PWT、PWL、uWire、HDQ/1-Wire);USB接口;支持MMC/SD卡。

(5)时钟控制。时钟源:32.768kHz的振荡器;12MHz/13MHz的振荡器;可编程的内核锁相环。

(6)电源管理。Awake模式(正常运行模式)、Big-sleep模式(省电模式)、Deep-sleep(省电模式)模式。

(7)封装形式。289脚GZG BGA封装或GDY BGA封装。1.2 TI925T(ARM9TDMI)内核

TI925T(ARM9TDMI)内核是采用5阶段管道化流水线32位的RISC处理器架构的体系结构,并采用ARM9作内核,同时配备Thumb扩展。它能够处理32位或者16位的指令和8位、16位、32位的数据。这款新型高性能、低功耗的微构架兼容ARMv4T指令集,并通过采用协处理器CP15使体系结构得到增强。系统中的控制寄存器可通过对协处理器CP15的读写来对MMU、Cache和读写缓存控制器进行存取操作。这种微构架在ARM核的周围提供了:指令与数据存储器管理单元,指令、数据和写缓冲器,性能监控、调试和JTAG单元以及协处理器接口,MAC协处理器和内核存储总线。

TI925T 的MMU具有2个64个项的转换旁路缓存器(TLB)用于指令和数据流,每项均可映射存储器的段、大页和小页。为了保证内核周期的存取指令和数据,TI925T包含了分别独立的1个16KB的指令Cache和8KB的数据Cache。二者独立的好处是可以在同一时钟周期内读取指令和数据,而不需要双端口的Cache。指令和数据Cache都是2路相互关联的Cache,以16B为1块进行操作,并采用最小最近使用(LRU)算法以刷新存储。另外,TI925T还提供了写缓冲的性能用于提升内核,其能够缓冲数据的容量高达17字。

1.3 TMS320C55x内核

TMS320C55x内核的主要特点是:有1个64×8位的缓存队列(Instruction Buffer Queue),2个17位×17位的乘法累加单元(MAC),1个40位的算术逻辑单元(ALU),1个16位的算术逻辑单元,1个40位的桶形移位器(Barrel Shifter)和4个40位的加法器。另外还有12条独立的总线,即:3条数据读总线,2条数据写总线,5条数据地址总线,1条程序读取总线和1条程序地址总线。此外,还有用户可以配置的IDLE域。内核主要由4个单元组成:指令缓冲单元(I单元)、程序流单元(P单元)、地址数据流单元(A单元)和数据运算单元(D单元)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章