资料下载

×

TI_XIO1100NAND的树测试以太网交换机

消耗积分:0 |

格式:rar |

大小:0.09 MB |

2017-10-27

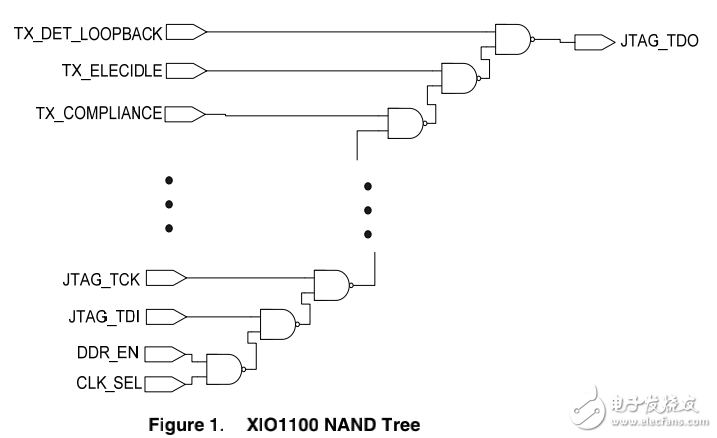

The common method for checking the interconnections between the ICs is to use JTAG

boundary scan. Since the XIO1100 PHY does not support JTAG boundary scan, a NAND-tree

feature has to be employed.

A NAND tree is exactly how it sounds: A number of nested NAND gates in which each I/O pin is

an input to one NAND gate. Figure 1 illustrates a NAND tree. The output of the nested NAND

gates is provided on the JTAG_TDO pin. A NAND-tree feature does not provide 100% coverage

but does allow for checking the connectivity of most I/Os on the XIO1100 PHY.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章