资料下载

×

浅谈TMS320F240的IDE接口仿真器设计方案

消耗积分:1 |

格式:rar |

大小:0.4 MB |

2017-10-29

摘要:

介绍以TMS320F240为核心,设计IDE接口仿零点器的硬件和软件设计方法。突出特点是硬件设计简练实用,监控软件精巧灵活。在设计嵌入式系统调试工具中具有典型性和实用性,对其它系统的调试也借鉴作用。 关键词:仿真器 监控程序 硬件调试 IDE接口 随着航空电子系统数字化的发展,机载嵌入式计算机逐步摆脱了“纯粹嵌入”时代,开始以主要控制角色而显露头脚。其存储系统也和地面计算机系统一样,提出了“海量存储”的要求。借鉴和使用IDE接品时一条重要途径。但在调试时一般缺乏IDE接口主方(Host)控制器。PC机虽然带有两个标准的集成在主板上的IDE接口,但在目前的Widows系统下却是透明的,无法在硬件调试级进行控制驱动。“工欲善其事,必先利其器”。为解决调试工具,笔者在此前自己动手,设计了一个IDE接口仿真器。硬件极其简练实用,软件精巧灵活。介绍出来,与大家切磋。

1 仿真器硬件设计

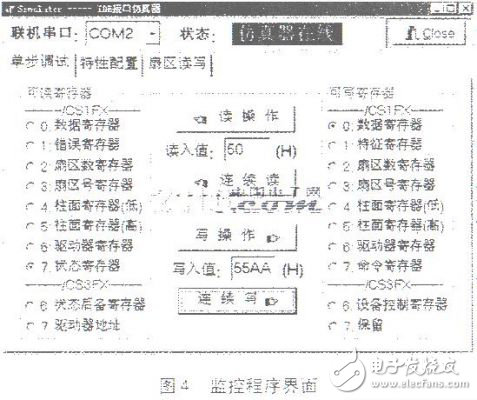

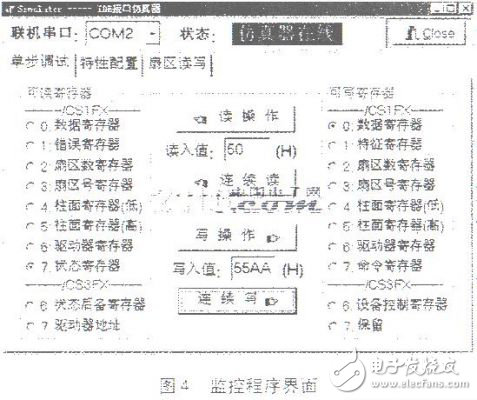

众所周知,IDE/ATA接口是16位总线,映像在主机的I/O空间,由主机对接口内的2组寄存器操作来完成“海量存储”。这些寄存器仅由2根片选(CS1FX、CS3FX)和3根地址线(A2、A1、A0)寻址。仿真器硬件只要能在监控程序的控制下产生对应控制信号,便能真实地仿真IDE调试所需的环境。需要仿真处理的主要信号如表1所列。信号方向以仿真器为参照,输出(Output)方向由仿真器驱动,输入(Input)信号由IDE设备驱动。 表1 主要仿真处理的信号 信号名方 向有效电平功 能 HDRST O(输出) L(低)复位IDE设备 CS1FX O(输出) L(低)第一组寄存器片选 CS3FX O(输出) L(低)第二组寄存器片选 A2~A0 O(输出)组合值接口内寄存器偏移地址 IOR O(输出) L(低)寄存器读信号 IOW O(输出) L(低)寄存器写信号 D15D0 I/O(双向)组合值数据总线,写时由仿真器驱动,读时由IDE设备驱动 DRQ I(输入) H(高) DMA请求 IRQ I(输入) H(高)中断请求 IDE接口的读写时序和一般CPU外设时序波形相似,其读取周期为70ns,具体波形不再给出。使用TI公司的TMS320F240(以下简称F240)可以方便地仿真出IDE的时序波形。只要使用外部READY信号,把I/O周期延长到70ns以上,就可以保证仿真数据读写可靠。以F240为核心,仿真器硬件设计真数据读写可靠。以F240为核心,仿真器硬件设计就非常简练。其全部硬件电路如图1、图2和图3所示。除去初期调试和驱动芯片外,整个核心就是F240和GAL16V8,已经仿真全部的IDE时序波形,图1是仿真器自身调试仿真监控程序时电路。使用2片CY7C199,组成32K%26;#215;16位的片外RAM程序存储器空间。当程序调试完成后,断开H1,将监控程序通过JTAG口直接烧入F240,就可以拔去2片外部程序存储器CY7C199。 图1 调试时的程序存储器配置 当仿真监控程序调试完成后,正式定型的仿真核心电路如图2所示。电路设计总的原则是简练实用,所以复位采用普通的RC电路,外加手工复位开关SW保证仿真器自身复位;利用RS232和主机之间通信,减少硬件额外开销;IDE接口的中断请求HIRQ直接接F240的外部中断XINT1(因为HIRQ高电平有效,所以将蓁不用的外部断XINT2等接地,保证蓁中断源不产生中断请求,减少软件中断响应多重判断环节);将F240的PB端口设置为输出端口,DMA请求HDRQ接到PB端口的最低位PB0,可以直接由硬件检测DRQ状态即可,并不真正需要DMA控制器;将F240的PC端口设置为输出端品,最高位PC7为复位IDE端口信号,当该位设置为0(低电平)时,产生复位IDE设备信号HDRST,该位设置为1时结束复位。其复位时间可由软件控制。IDE设备的寄存器映像在F240的I/O空间从0000H开始的16位地址。外部I/O只有IDE接口,不必采用全译码,直接由I/O片选IS和地址A3区分产生CFIFX和CS3FX即可。接口内偏移地址直接由A2~A0提供。F240的写信号WR可以直接作为接口写信号。但是F240的读信号是状态信号,在连续读操作中保持低电平,并无上升沿,所以需要专门产生读信号。PC主机通过串口和仿真器通信,监控仿真器,从而驱动调试的IDE设备。仿真器和IDE设备通过标准的硬盘电缆连接。为提高信号的抗干扰能力,这些信号经过总线驱动器驱动。图3是驱动和接口电路。 数据通路用16路驱动的IDT74LS16245实现,开门信号直接由I/O片选信号IS控制,方向端由写信号WR控制。而单向提供给IDE设备的其它信号,都经过54F244驱动。所有控制信号由GAL16V8实现。以下是其控制逻辑代码,信号名称和功能可参见 。 图2 核心仿真控制电路 …… EQUATIONS !HRST=!POR#!HRST;//RC上电复位和F240设置复位都产生IDE复位 !CS1FX=!IS%26;amp;!A3; //A3=0;产生第一组寄存器片选CS1FX=!IS %26;amp; A3; //A3=1:产生第二组寄存器片选CS3FX !IOR=!IS %26;amp; !RD; //*专门产生寄存器读信号。 [Q1,Q0].CLK=CPUCLK; [Q1,Q0].OE=!OE; [Q1,Q0].AR=!POR; //复位 //============================================== //F240系统控制状态机 //时钟20MHz,每一拍50ns //程序存储器CY7C199读写周期≤35ns,无需等待 //IDE接口寄存器读写周期≥70ns,等待2拍 //=============================================== State_Diagram [Q1,Q0]; State S0: //空闲状态 READY=H; //支持CY7C199访问 if(!IS)then //要访问IDE接口寄存器 S1 with {READY240=L;} State S1: //开始等待 READY240=L; Goto S2; State S2: READY240=L; Goto S3; State3: //时间到 READY240=H; Goto S0; //F240对READY信号只采样一次 END 仿真硬件的核心只有1片F240和1片GAL16V8。 驱动与接口电路 2 仿真器监控软件设计 软件设计包括驻留F240的监控程序和PC宿主机的监控程序,两者之间通过串口配合工作。这当然降低了IDE接口的数据吞吐率,但在逻辑仿真调试时不是主要焦点。为简约起见,避免复杂的词法分析,主从之间采用单字符监控命令。其串口监控命令通信帧定义如下: 0 1 2…n-2 n-1 帧标志(AAH)命令字符(Cmd)参数项校验和CheckSum 其校验和为前n-1个字节代数和的补码,即 CheckSum=-∑Bi(i=0,1…n-1) 下面介绍几个主要命令和程序实现方法,其中寄存器名称和地址可参考图4界面。

(1)1命令:读IDE寄存器 当监控程序识别出1命令后,根据参数提供的寄存器索引,映射为对应的I/O地址。F240的输入/输出命令与x86系列不同,它在指令中必须直接给出地址。 … LACC Reg BZ IsDatReg ;0号索引,即读数据寄存器 SUB #1 BZ IsError ;/*号索引,即读错误类型寄存器 … BZ IsAltReg ;8号索引,即读后备状态寄存器 SUB #1 BZ IsDrvAddrReg ;9号索引,即读驱动器地址寄存器 … IsDatReg IN Value,DatReg ;读数据寄存器 RET IsAltReg: IN Value,DevAddrReg;读驱动器地址寄存器 RET 当I命令执行完毕后,应该将寄存器读入值回送PC主机。

(2)0命令:写IDE寄存器 寄存器输出命令参数需要提供寄存器索引和映射为对应的I/O地址。

(3)H命令:硬件复位IDE设备 硬件复位时应将F240的IOPC7引脚设置为低电平10ms以上。 LDP #00E1h ;DP=00E1H:708H~70FFH的页址 LACL #8000H ;D15=1:IOPC7:作输出 D7=0;设置IOPC7=0 SACL PCDATDIR ;写PC端口,设置HRST信号为低电平 CALL Delay 10ms ;保持复位信号10ms的低电平 LACL #8080H ;D15=1:IOPC7:作输出 ;D7=1:设置IOPC7=1 SACL PCDATDIR ;恢复HRST信号为高电平 类似地,监测DMA请求HDRQ状态时,可以设置端为输入属性,然后读入IOPB0。监测中断请求HIRQ时,可以直接读XINT1状态,即读7070H处的XINT1CR寄存器。

(4)S命令:软件复位IDE设备 软件复位时可以向IDE接口的DevCtrlReg(设备控制寄存器)写入适当值实现。 LDP #0 ;指向.bss变量区 SPLK=#000EH,Value ;D2=SW Rst=1:软件强制复位 ;D1=/IEn=1:禁止IDE发中断 OUT Value,DevCtrlReg ;复位IDE设备 CALL Delay 10ms ;保持复位状态10ms SPLK #000AH,Value ;D2=SW Rst=0:结束复位状态 OUT Value,DevCtrlReg CALL Delay 10ms SPLK #000EH,Value ;D6=LBA=1:采用逻辑块寻址模式 OUT Value,DrvHeadReg ;设置驱动器寄存器

(5)C命令:读取IDE设备ID号和相关配置 IDE设备内的相关配置对其它操作影响较大,主机应该掌握这些参数。诸如柱面数、磁头数、每个磁道的扇区数以及最大扇区号等。这段程序稍微复杂一些。 CALL WaitRDY ;读状态寄存器,等待D6=1,亦即IDE设备完成上次命令 SPLK#000EH,Value OUT Value,DrvHeadReg ;选择主从驱动器 SPLK #00ECH,Value OUT Value,CmdReg ;发命令,读取配置参数 CALL WaitDRQ ;读状态寄存器,等待D6=1并且D3=1,亦即RDY并发出DRQ请求 MAR *,AR1 ;AR1:当前辅助寄存器 LAR AR1,#BufSADDR ;AR1→扇区缓冲区开始地址 RPT #0FFh ;循环次数=FFH+1=256 IN *+,DatReg ;读入配置数据 读出配置参数后,再把它送给PC机的监控程序,从中再细分出具体参数。 类似地,读一个扇区或写一个扇区的命令与这个命令相似。只是在发命令前应该设置柱面扇区等寄存器定位到具体的扇区。

(6)PC宿主机监控程序功能 PC宿主机监控程序主要通过串口监控仿真器。在底层通信中,应该为每一个监控命令建立对应函数。在应用层,可以将几个简单命令有机组合,完成复杂功能,减小仿真器驻留监控难度。例如,在读取配置参数命令中,分解缓冲数据。在读写扇区命令中,将LBA逻辑扇区地址分解成驱动器号、扇区号、柱面号等。 重要的是为用户提供一个Windows环境下特别容易操作的接口界面,贴近硬件调试,产生所需信号波形,用示波器捕获分析。图4是宿主机的一个界面,具体方法细节不再讨论。 结语 随着航空电子新系统研制的智能化和接口标准化,硬件调试对仿真设备和环境要求也越来越高。鉴于成本和上市时间的限制,采用嵌入式CPU研制一些简单实用的仿真设备,是解决矛盾的一条重要途径。本文所介绍的IDE接口仿真器硬件简练、软件精巧,在多个型号的Flash Disk研制中发挥了重要作用。

介绍以TMS320F240为核心,设计IDE接口仿零点器的硬件和软件设计方法。突出特点是硬件设计简练实用,监控软件精巧灵活。在设计嵌入式系统调试工具中具有典型性和实用性,对其它系统的调试也借鉴作用。 关键词:仿真器 监控程序 硬件调试 IDE接口 随着航空电子系统数字化的发展,机载嵌入式计算机逐步摆脱了“纯粹嵌入”时代,开始以主要控制角色而显露头脚。其存储系统也和地面计算机系统一样,提出了“海量存储”的要求。借鉴和使用IDE接品时一条重要途径。但在调试时一般缺乏IDE接口主方(Host)控制器。PC机虽然带有两个标准的集成在主板上的IDE接口,但在目前的Widows系统下却是透明的,无法在硬件调试级进行控制驱动。“工欲善其事,必先利其器”。为解决调试工具,笔者在此前自己动手,设计了一个IDE接口仿真器。硬件极其简练实用,软件精巧灵活。介绍出来,与大家切磋。

1 仿真器硬件设计

众所周知,IDE/ATA接口是16位总线,映像在主机的I/O空间,由主机对接口内的2组寄存器操作来完成“海量存储”。这些寄存器仅由2根片选(CS1FX、CS3FX)和3根地址线(A2、A1、A0)寻址。仿真器硬件只要能在监控程序的控制下产生对应控制信号,便能真实地仿真IDE调试所需的环境。需要仿真处理的主要信号如表1所列。信号方向以仿真器为参照,输出(Output)方向由仿真器驱动,输入(Input)信号由IDE设备驱动。 表1 主要仿真处理的信号 信号名方 向有效电平功 能 HDRST O(输出) L(低)复位IDE设备 CS1FX O(输出) L(低)第一组寄存器片选 CS3FX O(输出) L(低)第二组寄存器片选 A2~A0 O(输出)组合值接口内寄存器偏移地址 IOR O(输出) L(低)寄存器读信号 IOW O(输出) L(低)寄存器写信号 D15D0 I/O(双向)组合值数据总线,写时由仿真器驱动,读时由IDE设备驱动 DRQ I(输入) H(高) DMA请求 IRQ I(输入) H(高)中断请求 IDE接口的读写时序和一般CPU外设时序波形相似,其读取周期为70ns,具体波形不再给出。使用TI公司的TMS320F240(以下简称F240)可以方便地仿真出IDE的时序波形。只要使用外部READY信号,把I/O周期延长到70ns以上,就可以保证仿真数据读写可靠。以F240为核心,仿真器硬件设计真数据读写可靠。以F240为核心,仿真器硬件设计就非常简练。其全部硬件电路如图1、图2和图3所示。除去初期调试和驱动芯片外,整个核心就是F240和GAL16V8,已经仿真全部的IDE时序波形,图1是仿真器自身调试仿真监控程序时电路。使用2片CY7C199,组成32K%26;#215;16位的片外RAM程序存储器空间。当程序调试完成后,断开H1,将监控程序通过JTAG口直接烧入F240,就可以拔去2片外部程序存储器CY7C199。 图1 调试时的程序存储器配置 当仿真监控程序调试完成后,正式定型的仿真核心电路如图2所示。电路设计总的原则是简练实用,所以复位采用普通的RC电路,外加手工复位开关SW保证仿真器自身复位;利用RS232和主机之间通信,减少硬件额外开销;IDE接口的中断请求HIRQ直接接F240的外部中断XINT1(因为HIRQ高电平有效,所以将蓁不用的外部断XINT2等接地,保证蓁中断源不产生中断请求,减少软件中断响应多重判断环节);将F240的PB端口设置为输出端口,DMA请求HDRQ接到PB端口的最低位PB0,可以直接由硬件检测DRQ状态即可,并不真正需要DMA控制器;将F240的PC端口设置为输出端品,最高位PC7为复位IDE端口信号,当该位设置为0(低电平)时,产生复位IDE设备信号HDRST,该位设置为1时结束复位。其复位时间可由软件控制。IDE设备的寄存器映像在F240的I/O空间从0000H开始的16位地址。外部I/O只有IDE接口,不必采用全译码,直接由I/O片选IS和地址A3区分产生CFIFX和CS3FX即可。接口内偏移地址直接由A2~A0提供。F240的写信号WR可以直接作为接口写信号。但是F240的读信号是状态信号,在连续读操作中保持低电平,并无上升沿,所以需要专门产生读信号。PC主机通过串口和仿真器通信,监控仿真器,从而驱动调试的IDE设备。仿真器和IDE设备通过标准的硬盘电缆连接。为提高信号的抗干扰能力,这些信号经过总线驱动器驱动。图3是驱动和接口电路。 数据通路用16路驱动的IDT74LS16245实现,开门信号直接由I/O片选信号IS控制,方向端由写信号WR控制。而单向提供给IDE设备的其它信号,都经过54F244驱动。所有控制信号由GAL16V8实现。以下是其控制逻辑代码,信号名称和功能可参见 。 图2 核心仿真控制电路 …… EQUATIONS !HRST=!POR#!HRST;//RC上电复位和F240设置复位都产生IDE复位 !CS1FX=!IS%26;amp;!A3; //A3=0;产生第一组寄存器片选CS1FX=!IS %26;amp; A3; //A3=1:产生第二组寄存器片选CS3FX !IOR=!IS %26;amp; !RD; //*专门产生寄存器读信号。 [Q1,Q0].CLK=CPUCLK; [Q1,Q0].OE=!OE; [Q1,Q0].AR=!POR; //复位 //============================================== //F240系统控制状态机 //时钟20MHz,每一拍50ns //程序存储器CY7C199读写周期≤35ns,无需等待 //IDE接口寄存器读写周期≥70ns,等待2拍 //=============================================== State_Diagram [Q1,Q0]; State S0: //空闲状态 READY=H; //支持CY7C199访问 if(!IS)then //要访问IDE接口寄存器 S1 with {READY240=L;} State S1: //开始等待 READY240=L; Goto S2; State S2: READY240=L; Goto S3; State3: //时间到 READY240=H; Goto S0; //F240对READY信号只采样一次 END 仿真硬件的核心只有1片F240和1片GAL16V8。 驱动与接口电路 2 仿真器监控软件设计 软件设计包括驻留F240的监控程序和PC宿主机的监控程序,两者之间通过串口配合工作。这当然降低了IDE接口的数据吞吐率,但在逻辑仿真调试时不是主要焦点。为简约起见,避免复杂的词法分析,主从之间采用单字符监控命令。其串口监控命令通信帧定义如下: 0 1 2…n-2 n-1 帧标志(AAH)命令字符(Cmd)参数项校验和CheckSum 其校验和为前n-1个字节代数和的补码,即 CheckSum=-∑Bi(i=0,1…n-1) 下面介绍几个主要命令和程序实现方法,其中寄存器名称和地址可参考图4界面。

(1)1命令:读IDE寄存器 当监控程序识别出1命令后,根据参数提供的寄存器索引,映射为对应的I/O地址。F240的输入/输出命令与x86系列不同,它在指令中必须直接给出地址。 … LACC Reg BZ IsDatReg ;0号索引,即读数据寄存器 SUB #1 BZ IsError ;/*号索引,即读错误类型寄存器 … BZ IsAltReg ;8号索引,即读后备状态寄存器 SUB #1 BZ IsDrvAddrReg ;9号索引,即读驱动器地址寄存器 … IsDatReg IN Value,DatReg ;读数据寄存器 RET IsAltReg: IN Value,DevAddrReg;读驱动器地址寄存器 RET 当I命令执行完毕后,应该将寄存器读入值回送PC主机。

(2)0命令:写IDE寄存器 寄存器输出命令参数需要提供寄存器索引和映射为对应的I/O地址。

(3)H命令:硬件复位IDE设备 硬件复位时应将F240的IOPC7引脚设置为低电平10ms以上。 LDP #00E1h ;DP=00E1H:708H~70FFH的页址 LACL #8000H ;D15=1:IOPC7:作输出 D7=0;设置IOPC7=0 SACL PCDATDIR ;写PC端口,设置HRST信号为低电平 CALL Delay 10ms ;保持复位信号10ms的低电平 LACL #8080H ;D15=1:IOPC7:作输出 ;D7=1:设置IOPC7=1 SACL PCDATDIR ;恢复HRST信号为高电平 类似地,监测DMA请求HDRQ状态时,可以设置端为输入属性,然后读入IOPB0。监测中断请求HIRQ时,可以直接读XINT1状态,即读7070H处的XINT1CR寄存器。

(4)S命令:软件复位IDE设备 软件复位时可以向IDE接口的DevCtrlReg(设备控制寄存器)写入适当值实现。 LDP #0 ;指向.bss变量区 SPLK=#000EH,Value ;D2=SW Rst=1:软件强制复位 ;D1=/IEn=1:禁止IDE发中断 OUT Value,DevCtrlReg ;复位IDE设备 CALL Delay 10ms ;保持复位状态10ms SPLK #000AH,Value ;D2=SW Rst=0:结束复位状态 OUT Value,DevCtrlReg CALL Delay 10ms SPLK #000EH,Value ;D6=LBA=1:采用逻辑块寻址模式 OUT Value,DrvHeadReg ;设置驱动器寄存器

(5)C命令:读取IDE设备ID号和相关配置 IDE设备内的相关配置对其它操作影响较大,主机应该掌握这些参数。诸如柱面数、磁头数、每个磁道的扇区数以及最大扇区号等。这段程序稍微复杂一些。 CALL WaitRDY ;读状态寄存器,等待D6=1,亦即IDE设备完成上次命令 SPLK#000EH,Value OUT Value,DrvHeadReg ;选择主从驱动器 SPLK #00ECH,Value OUT Value,CmdReg ;发命令,读取配置参数 CALL WaitDRQ ;读状态寄存器,等待D6=1并且D3=1,亦即RDY并发出DRQ请求 MAR *,AR1 ;AR1:当前辅助寄存器 LAR AR1,#BufSADDR ;AR1→扇区缓冲区开始地址 RPT #0FFh ;循环次数=FFH+1=256 IN *+,DatReg ;读入配置数据 读出配置参数后,再把它送给PC机的监控程序,从中再细分出具体参数。 类似地,读一个扇区或写一个扇区的命令与这个命令相似。只是在发命令前应该设置柱面扇区等寄存器定位到具体的扇区。

(6)PC宿主机监控程序功能 PC宿主机监控程序主要通过串口监控仿真器。在底层通信中,应该为每一个监控命令建立对应函数。在应用层,可以将几个简单命令有机组合,完成复杂功能,减小仿真器驻留监控难度。例如,在读取配置参数命令中,分解缓冲数据。在读写扇区命令中,将LBA逻辑扇区地址分解成驱动器号、扇区号、柱面号等。 重要的是为用户提供一个Windows环境下特别容易操作的接口界面,贴近硬件调试,产生所需信号波形,用示波器捕获分析。图4是宿主机的一个界面,具体方法细节不再讨论。 结语 随着航空电子新系统研制的智能化和接口标准化,硬件调试对仿真设备和环境要求也越来越高。鉴于成本和上市时间的限制,采用嵌入式CPU研制一些简单实用的仿真设备,是解决矛盾的一条重要途径。本文所介绍的IDE接口仿真器硬件简练、软件精巧,在多个型号的Flash Disk研制中发挥了重要作用。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章