资料下载

×

Builder数字信号处理器的FPGA设计

消耗积分:1 |

格式:rar |

大小:0.5 MB |

2017-10-31

DSP技术广泛应用于各个领域,但传统的数字信号处理器由于以顺序方式工作使得数据处理速度较低,且在功能重构及应用目标的修改方面缺乏灵活性。而使用具有并行处理特性的FPGA实现数字信号处理系统,具有很强的实时性和灵活性,因此利用FPGA实现数字信号处理成为数字信号处理领域的一种新的趋势。

以往基于FPGA的数字信号处理系统的模型及算法采用VHDL或VerilogHDL等硬件描述语言描述。但这些硬件描述语言往往比较复杂,而采用Altera公司推出的专门针对数字信号处理器设计工具DSP BuildIer则可大大简化设计过程,提高设计效率。

1 基于DSP Builder的数字信号处理器设计流程

DSP Builder是一个系统级(或者说算法级)设计工具,它架构在多个软件工具之上,并连接系统级的算法仿真建模和RTL级的硬件实现两个设计领域的设计工具,最大程度地发挥了这两种工具的优势。

DSP Builder依赖于Math-Works公司的数学分析工具Matlab/Simulink,以Simulink的Blockset出现,可在simulink中进行图形化设计和仿真,同时又通过signal Compiler把Maltlab/Simulink/DSP Builder的设计文件转成相应的VHDL设计文件,以及用控制综合与编译的tcl脚本。而对后者的处理可以由FPGA/CPLD开发工具QuartusⅡ完成。其设计流程如下:

Step1:在Simulink环境中调用Altera DSP库(非MATLAB自带的DSP库)中的块,进行数学模型设计。

Step2:在MATLAB中进行纯数学上的仿真、验证及修改。

Step3:当仿真符合设计要求后,再加入并运行Signal Compiler模块,将.mdl文件自动转成.vhd文件,进行RTL级的功能仿真和逻辑综合。

Step4:在QuartusⅡ中进行编译设计并进行时序仿真。

Step5:下载到一个硬件开发板上并测试。

2 设计实例

FIR和IIR滤波器是当前数字信号处理巾最常用的2种滤波器,其中FIR因其具有精确的线性相位特性而得到广泛应用。下面以截止频率为5 kHz,采样频率为32 kHz,输入序列位宽为9位(最高位为符号位)的12阶FIR低通数字滤波器为例,阐述基于DSP Builder的数字信号处理器设计方案。

2.1 FIR数字滤波器结构模型

对于N阶FIR数字滤波系统,其冲击响应总是有限长的,系统函数为:

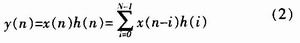

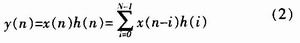

滤波器的差分方程为:

式中,x(n)是输入采样序列,h(n)是滤波器系数,N是滤波器的阶数,y(n)表示滤波器的输出序列。

设计滤波器的任务就是寻找一个因果、物理上可实现的系统函数H(z),使其频率响应满足所希望的频域指标。图1为阶FIR数字滤波器的结构图。可见,FIR的数字滤波过程就是一个信号逐级延迟的过程,将各级的延迟输出加权累计,即得到FIR的输出。

以往基于FPGA的数字信号处理系统的模型及算法采用VHDL或VerilogHDL等硬件描述语言描述。但这些硬件描述语言往往比较复杂,而采用Altera公司推出的专门针对数字信号处理器设计工具DSP BuildIer则可大大简化设计过程,提高设计效率。

1 基于DSP Builder的数字信号处理器设计流程

DSP Builder是一个系统级(或者说算法级)设计工具,它架构在多个软件工具之上,并连接系统级的算法仿真建模和RTL级的硬件实现两个设计领域的设计工具,最大程度地发挥了这两种工具的优势。

DSP Builder依赖于Math-Works公司的数学分析工具Matlab/Simulink,以Simulink的Blockset出现,可在simulink中进行图形化设计和仿真,同时又通过signal Compiler把Maltlab/Simulink/DSP Builder的设计文件转成相应的VHDL设计文件,以及用控制综合与编译的tcl脚本。而对后者的处理可以由FPGA/CPLD开发工具QuartusⅡ完成。其设计流程如下:

Step1:在Simulink环境中调用Altera DSP库(非MATLAB自带的DSP库)中的块,进行数学模型设计。

Step2:在MATLAB中进行纯数学上的仿真、验证及修改。

Step3:当仿真符合设计要求后,再加入并运行Signal Compiler模块,将.mdl文件自动转成.vhd文件,进行RTL级的功能仿真和逻辑综合。

Step4:在QuartusⅡ中进行编译设计并进行时序仿真。

Step5:下载到一个硬件开发板上并测试。

2 设计实例

FIR和IIR滤波器是当前数字信号处理巾最常用的2种滤波器,其中FIR因其具有精确的线性相位特性而得到广泛应用。下面以截止频率为5 kHz,采样频率为32 kHz,输入序列位宽为9位(最高位为符号位)的12阶FIR低通数字滤波器为例,阐述基于DSP Builder的数字信号处理器设计方案。

2.1 FIR数字滤波器结构模型

对于N阶FIR数字滤波系统,其冲击响应总是有限长的,系统函数为:

滤波器的差分方程为:

式中,x(n)是输入采样序列,h(n)是滤波器系数,N是滤波器的阶数,y(n)表示滤波器的输出序列。

设计滤波器的任务就是寻找一个因果、物理上可实现的系统函数H(z),使其频率响应满足所希望的频域指标。图1为阶FIR数字滤波器的结构图。可见,FIR的数字滤波过程就是一个信号逐级延迟的过程,将各级的延迟输出加权累计,即得到FIR的输出。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章