资料下载

×

如何预测直接数字频率合成器(DDS)输出频谱中主相位截断杂散的频率和幅度

消耗积分:1 |

格式:rar |

大小:0.4 MB |

2017-11-10

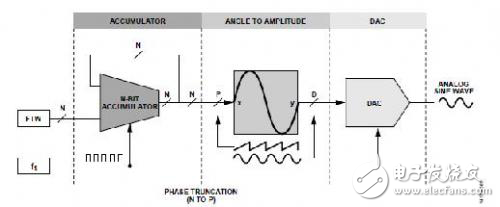

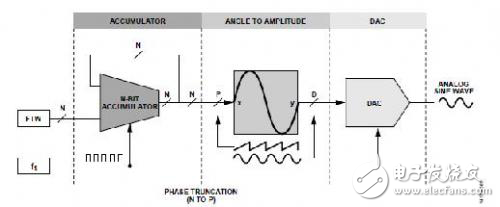

现代直接数字频率合成器(DDS)通常利用累加器和数字频率调谐字(FTW)在累加器输出端产生周期性的N位数字斜坡(见图1)。 此数字斜坡可依据公式1定义DDS的输出频率(fO),其中fS为DDS采样速率(或系统时钟频率)。

(1)

(1)

DDS给定时,组成FTW的位数(N)定义了fO的最小可能变化,这发生在FTW值仅更改最低有效位(LSB)时。 也就是说,FTW中的1 LSB变化定义了DDS的调谐分辨率。 例如,N = 32的DDS的调谐分辨率高于N = 24的DDS。为了证实DDS的极佳调谐能力,以AD9912为例,N = 48产生的调谐分辨率为1/248(即1/281,474,976,710,656)。 事实上,fS = 1 GHz时,AD9912产生的频率调谐分辨率约为3.6 µHz (0.0000036 Hz)。

若DDS的FTW为N位,细看图1可知,累加器输出端的位数(N)和角度转幅度模块输入端的位数(P)之间存在明显的差异,即P ≤ N。这种差异会导致DDS输出频谱中出现相位截断杂散。

知道给定DDS的P值对预测相位截断杂散非常重要。 本应用笔记介绍了一种用于计算特定相位截断杂散的频率和幅度的方法,尤其适合给定FTW的主相位截断(PPT)。

图1. DDS功能框图

相位截断

累加器和FTW组成DDS的频率控制元件。 但是,除了频率控制元件外,DDS还具有将N位累加器输出从相位值转换为幅度值的角度转幅度模块。 角度转幅度模块占据了DDS数字电路的很大一部分。 因此,通过增大N来提高DDS的调谐分辨率会大幅增加角度转幅度模块所需的电路数。 同样,将所有N位相位信息转换为幅度不太实际。 如图1所示,实际DDS使用累加器位的子集进行相位幅度转换,即P最高有效位(MSB)。 这种位截断会大幅减少角度转幅度模块所需的电路数。 但代价是需要在DDS输出端引入可能的频谱伪像(具体而言就是相位截断杂散)。

相位截断杂散

根据定义,按P = N设计的DDS没有相位截断。 因此,其输出频谱中没有相位截断杂散。 但是在实际DDS中,P 《 N,这会产生相位截断。

有三类相位截断杂散: 一阶、二阶和三阶。 这几个分类源于DDS中相位幅度转换器和数模转换器(DAC)的级联组合的频谱特性。 图2结合图形说明将傅里叶变换技术应用于角度转幅度模块(带P位相位输入)和呈现谐波失真的非理想DAC所产生的谱线。

(1)

(1)DDS给定时,组成FTW的位数(N)定义了fO的最小可能变化,这发生在FTW值仅更改最低有效位(LSB)时。 也就是说,FTW中的1 LSB变化定义了DDS的调谐分辨率。 例如,N = 32的DDS的调谐分辨率高于N = 24的DDS。为了证实DDS的极佳调谐能力,以AD9912为例,N = 48产生的调谐分辨率为1/248(即1/281,474,976,710,656)。 事实上,fS = 1 GHz时,AD9912产生的频率调谐分辨率约为3.6 µHz (0.0000036 Hz)。

若DDS的FTW为N位,细看图1可知,累加器输出端的位数(N)和角度转幅度模块输入端的位数(P)之间存在明显的差异,即P ≤ N。这种差异会导致DDS输出频谱中出现相位截断杂散。

知道给定DDS的P值对预测相位截断杂散非常重要。 本应用笔记介绍了一种用于计算特定相位截断杂散的频率和幅度的方法,尤其适合给定FTW的主相位截断(PPT)。

图1. DDS功能框图

相位截断

累加器和FTW组成DDS的频率控制元件。 但是,除了频率控制元件外,DDS还具有将N位累加器输出从相位值转换为幅度值的角度转幅度模块。 角度转幅度模块占据了DDS数字电路的很大一部分。 因此,通过增大N来提高DDS的调谐分辨率会大幅增加角度转幅度模块所需的电路数。 同样,将所有N位相位信息转换为幅度不太实际。 如图1所示,实际DDS使用累加器位的子集进行相位幅度转换,即P最高有效位(MSB)。 这种位截断会大幅减少角度转幅度模块所需的电路数。 但代价是需要在DDS输出端引入可能的频谱伪像(具体而言就是相位截断杂散)。

相位截断杂散

根据定义,按P = N设计的DDS没有相位截断。 因此,其输出频谱中没有相位截断杂散。 但是在实际DDS中,P 《 N,这会产生相位截断。

有三类相位截断杂散: 一阶、二阶和三阶。 这几个分类源于DDS中相位幅度转换器和数模转换器(DAC)的级联组合的频谱特性。 图2结合图形说明将傅里叶变换技术应用于角度转幅度模块(带P位相位输入)和呈现谐波失真的非理想DAC所产生的谱线。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章