资料下载

×

IEEE1588同步原理及其在PTN网中的实现

消耗积分:0 |

格式:rar |

大小:1 MB |

2017-11-16

详细分析了IEEE1588时钟同步的基本原理,介绍了阿尔卡特朗讯TSS-5产品中实现IEEE1588时钟同步系统的方案,给出具体的硬件架构框图以及系统功能框图,最后列出TSS-5网元在实验室做的时间性能实验、实验结果表明TSS-5时钟同步具有稳定的性能,同步精度达到亚微秒级,可满足PTN产品高精度时钟同步的要求。

1 IEEE1588同步原理

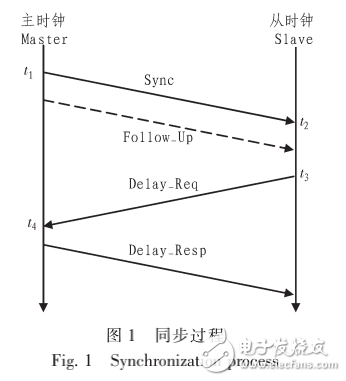

IEEE 1588通过交换报文来确定主时钟(Master)和从时钟( Slave)之间的时间偏差及报文传输的网络延迟。网l为IEEE 1588同步原理图。Master端发Syne消息给Slave,SYnc消息中包括其离开Master时的时间tl,Slave接收后记录该消息到达时间t2;Slave发Delay_Req消息给Master,并记录Delay_Req的离开时刻如;Maste端记录Delay_Req到达时间t4,并通过Delay_Resp把t4发回给Slave。Slave根据fl,£2,屯,t4来计算主从时间偏差及传输的网络延迟。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章