资料下载

×

基于FPGA+DSP的智能车全景视觉系统解析

消耗积分:1 |

格式:rar |

大小:0.3 MB |

2017-11-30

基于单相机的全景视觉系统是利用凸面镜反射四周图像进行定位,在计算资源有限时是一种较好的选择,且视觉导航等方向的应用也成为一种最实用的方法[1-2],这种方案虽然视野开阔,但获取的信息有限,真实的系统中很难应用。随着芯片计算能力的不断提高,基于多通道的全景视觉系统已逐渐成为可能。本文介绍的智能车多通道全景视觉是指以观测点为中心,多个相机可同时观测车辆的前中、前左、前右、后左、后右和顶上6个方向的景物。该系统中的6台数字相机中5台分布在车辆的侧面,1台在顶部,可以得到车辆周围全景360°的图像。该系统每个相机的分辨率为百万像素,即1 280×1 024,帧率为30 f/s,即便图像为8 bit单色,系统的总数据率也高达200 MB/s以上。同时,6个相机图像需要预处理,投影到同一坐标系,或者拼接成单幅完整图像才能满足智能车导航系统的要求,这些涉及到大量复杂计算。针对这些要求,该系统的硬件处理部分利用了DSP和FPGA芯片各自的特长,选用高速DSP+FPGA[3-6]的方案,而DSP方案也是海量图像处理中普遍应用的[7]。高性能通用C6416 DSP芯片,配合FPGA进行高度并行数据处理,可实现高速实时的视觉图像处理。这种方案的优点在于,不仅可以利用DSP的高速处理能力,同时利用FPGA的控制能力和在高度并行化数据处理方面的优势,相比其他方案更容易满足全景视觉系统所需要的高度实时处理。

1 系统总体方案设计

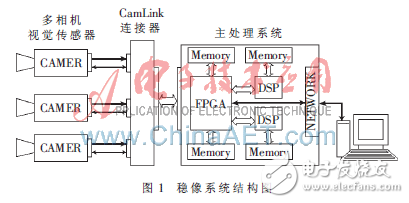

为适合高速图像采集,本系统选用CMOS传感器,CMOS的一个优点是数据读取速度快。系统由高速CMOS相机、基于CamLink技术的图像读取、FPGA+DSP的图像处理三部分构成,如图1所示。从图1可以看出,该系统有两片FPGA,图像读取模块中的FPGA1负责从CMOS相机抓图和通讯控制,FPGA2则辅助两片DSP进行高速图像处理,实现同时对6个相机图像的实时处理。

逻辑控制芯片FPGA1选用XILINX公司的XC3S1000LFG456作为视频数据采集控制芯片,该芯片是Spartan3低功耗系列的一种,具有1 M个逻辑门,24个18×18乘法器及丰富的片上存储空间,足够进行视频采集的同步逻辑控制。并行计算FPGA选用XILINX公司Virtex-4系列中的XC4VFX60-FF1152,内部有4 Mbit RAM,56 880个逻辑门和128个XtremeDSP模块,足够进行大量高速数据处理,特别是片上18 KRAM模块工作在500 MHz,支持真正的双端口读写同步操作,为该芯片作为芯片间高速数据交互提供了资源。2个协处理DSP芯片为TI公司高性能C6416,拥有8个并行处理单元,工作频率为600 Hz,最高处理速度可达4 800 兆指令/秒(MFLOPS)。

系统设计采集图像大小为1 280×1 024像素,最高速度可达每相机60 f/s的实时采集。6路摄像头输出的数字视频信号经过FPGA1进行同步分离后,进入输入端高速数据缓冲区。系统采用两片ZBT SRAM进行乒乓数据采集,当一帧图像采集完,FPGA1通知FPGA2进行数据转移,FPGA2将数据预处理后由DSP经EDMA保存到SRAM后等待进一步处理。

1 系统总体方案设计

为适合高速图像采集,本系统选用CMOS传感器,CMOS的一个优点是数据读取速度快。系统由高速CMOS相机、基于CamLink技术的图像读取、FPGA+DSP的图像处理三部分构成,如图1所示。从图1可以看出,该系统有两片FPGA,图像读取模块中的FPGA1负责从CMOS相机抓图和通讯控制,FPGA2则辅助两片DSP进行高速图像处理,实现同时对6个相机图像的实时处理。

逻辑控制芯片FPGA1选用XILINX公司的XC3S1000LFG456作为视频数据采集控制芯片,该芯片是Spartan3低功耗系列的一种,具有1 M个逻辑门,24个18×18乘法器及丰富的片上存储空间,足够进行视频采集的同步逻辑控制。并行计算FPGA选用XILINX公司Virtex-4系列中的XC4VFX60-FF1152,内部有4 Mbit RAM,56 880个逻辑门和128个XtremeDSP模块,足够进行大量高速数据处理,特别是片上18 KRAM模块工作在500 MHz,支持真正的双端口读写同步操作,为该芯片作为芯片间高速数据交互提供了资源。2个协处理DSP芯片为TI公司高性能C6416,拥有8个并行处理单元,工作频率为600 Hz,最高处理速度可达4 800 兆指令/秒(MFLOPS)。

系统设计采集图像大小为1 280×1 024像素,最高速度可达每相机60 f/s的实时采集。6路摄像头输出的数字视频信号经过FPGA1进行同步分离后,进入输入端高速数据缓冲区。系统采用两片ZBT SRAM进行乒乓数据采集,当一帧图像采集完,FPGA1通知FPGA2进行数据转移,FPGA2将数据预处理后由DSP经EDMA保存到SRAM后等待进一步处理。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章