资料下载

×

基于PCIe的多路传输系统的DMA控制器设计

消耗积分:3 |

格式:rar |

大小:0.78 MB |

2017-12-05

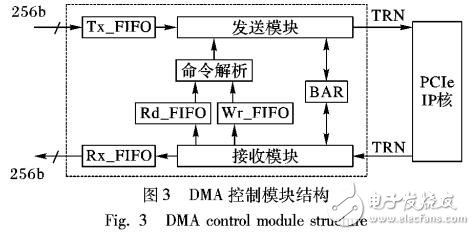

为了避免PCIe传输过程中PIO写延时、主机与嵌入式处理系统交互次数过多等问题对于传输带宽的影响,设计了一种基于命令缓冲机制的直接存储访问( DMA)控制器以提高传输带宽利用率。采用FPGA端内部设置命令缓冲区的方式,使得DMA控制器可以缓存PC端的数据传输请求,FPGA根据自身需求动态地访问PC端存储空间,增强了传输灵活性;同时,提出一种动态拼接的DMA调度方法,通过合并相邻存储区访问请求的方式,进一步减少主机与硬件的交互次数和中断产生次数。系统传输速率测试实验中,DMA写最高速率可达1 631 MB/s,DMA读最高速率可达1582 MB/s,带宽最大值可达PCIe总线理论带宽值的85. 4qo;与传统PIO方式的DMA传输方法相比,DMA读带宽提升58%,DMA写带宽提升36%。实验结果表明,本设计能够有效提升DMA传输效率,明显优于PIO方式。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章