资料下载

×

插入式短波预失真器的设计与实现

消耗积分:3 |

格式:rar |

大小:1.77 MB |

2018-01-18

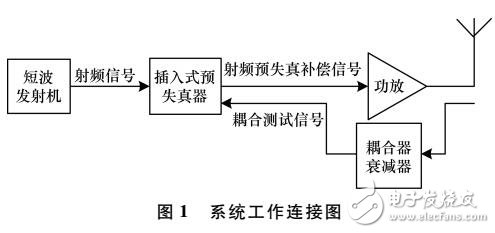

在已有带预失真的短波发信系统中,预失真处理通常与激励器基带信号处理部分高度融合,无法直接应用于已有的短波通信系统,或者需要对已有系统进行大幅修改。针对该问题,提出一种插入式预失真技术,并利用DSP+ FPGA硬件平台,设计一种插入式短波预失真器。插入式短波预失真器级联在激励器与功放之间,DSP控制整个系统以及预失真算法部分。FPGA完成正常通信与测量2种模式下的数字混频数字滤波以及预失真补偿,利用ARM控制板集成的以太网功能实现PC与插入式短波预失真器的网口通信。实验结果表明,该插入式短波预失真器可有效改善功放互调失真指标,由仅1/3频点达标改善为全频段抑制至-36 dB以下,达到了预设指标要求。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章