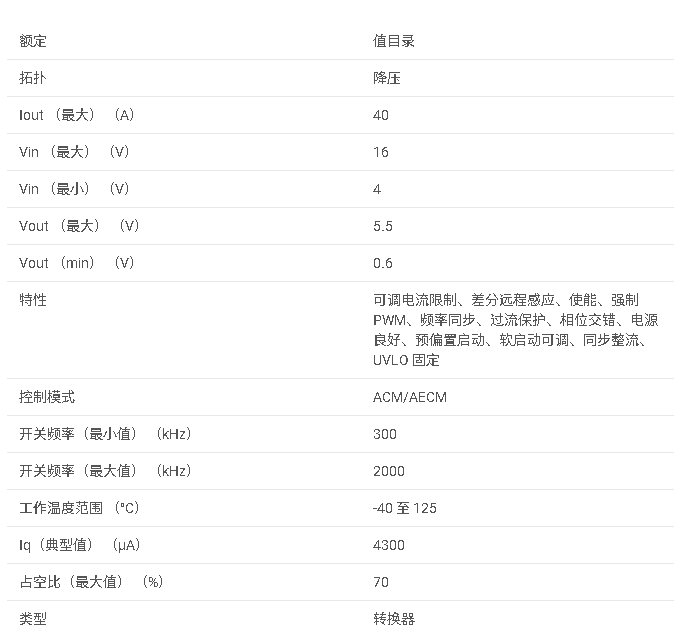

TPS543C20A 具有自适应内部补偿的 4V 至 16V、40A 同步 SWIFT™ 降压转换器数据手册

描述

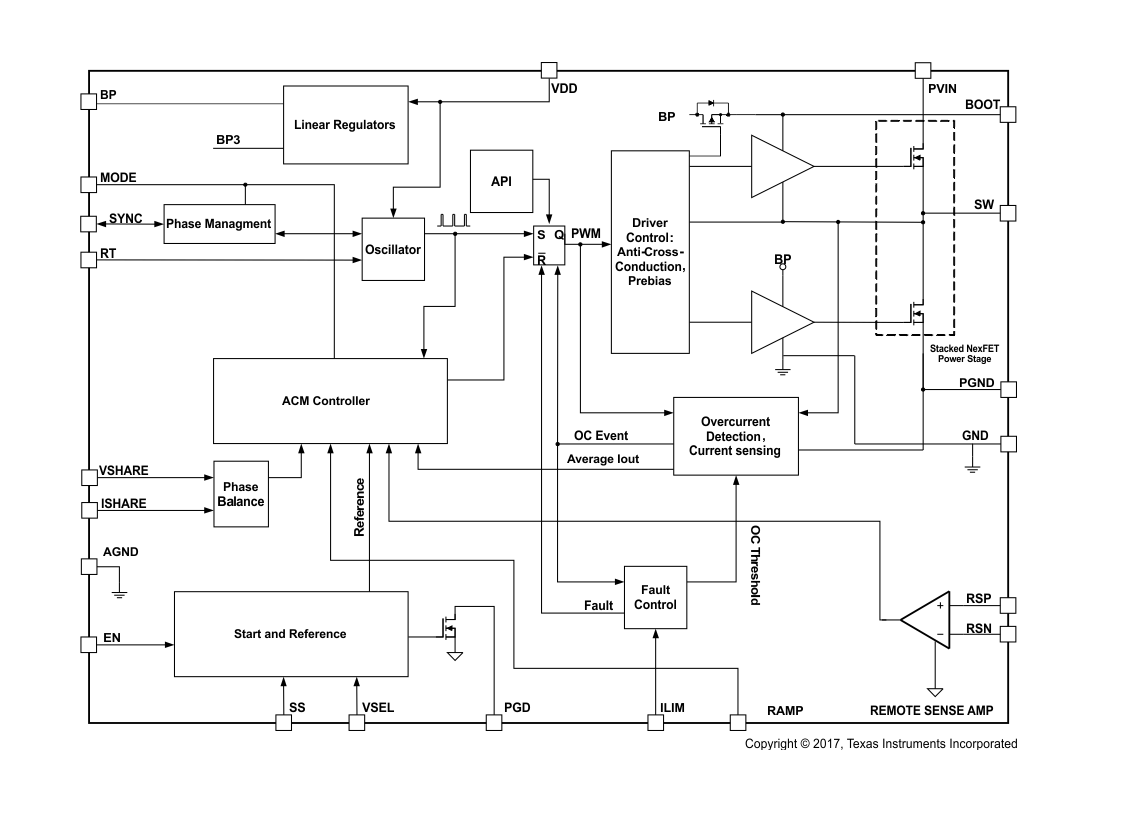

TPS543C20A 使用内部补偿的仿真峰值电流模式控制,以及用于 EMI 敏感型 POL 的时钟同步固定频率调制器。内部积分器和直接放大斜坡跟踪环路消除了在宽频率范围内进行外部补偿的需求,从而使系统设计灵活、密集和简单。可选的 API 和体制动分别通过显著减少下冲和过冲来帮助改善瞬态性能。具有低损耗开关功能的集成 NexFET™ MOSFET 有助于提高效率,并在 5 mm × 7 mm PowerStack™ 封装中提供高达 40 A 的电流,并带有布局友好的导热垫。两个 TPS543C20A 器件可以堆叠在一起,以提供高达 80A 的负载点。

*附件:tps543c20a.pdf

特性

- 内部补偿高级电流模式控制 40A POL

- 输入电压范围:4 V 至 16 V

- 输出电压范围:0.6 V 至 5.5 V

- 具有无损低侧电流感应的集成 3.4/0.9mΩ 堆叠式 NexFET™ 功率级

- 固定频率 - 与外部时钟同步和/或同步输出

- 引脚搭接可编程开关频率

- 300 kHz 至 2 MHz(独立)

- 300 kHz 至 1 MHz,可堆叠

- 堆栈 2× 电流共享、电压共享和 CLK 同步,电流共享电流高达 80 A

- 引脚搭接可编程基准电压范围为 0.6V 至 1.1V,精度为 0.5%

- 差分遥感

- 安全启动至预偏置输出

- 高精度打嗝电流限制

- 异步脉冲注入 (API) 和车身制动

- 具有 0.5mm 间距和单个导热垫的 40 引脚、5mm × 7mm LQFN 封装

参数

方框图

概述

TPS543C20A是一款高性能、40A同步降压SWIFT™转换器,适用于无线和有线通信基础设施设备、企业服务器、交换机、路由器、企业存储SSD以及ASIC、SoC、FPGA、DSP核心和I/O电源轨等应用。该转换器采用内部补偿的高级电流模式控制,具有固定频率、同步外部时钟和/或同步输出、可编程开关频率、电流共享、电压共享和时钟同步等功能。

主要特性

- 输入电压范围:4V至16V

- 输出电压范围:0.6V至5.5V

- 最大输出电流:40A(可堆叠至80A)

- 集成功率级:3.4/0.9mΩ堆叠NexFET™功率级,具有无损低侧电流感应

- 固定频率:可同步至外部时钟,300kHz至2MHz(独立),300kHz至1MHz(堆叠)

- 可编程开关频率:通过引脚配置实现

- 可编程参考电压:0.6V至1.1V,精度0.5%

- 差分远程感应

- 安全启动至预偏置输出

- 高精度打嗝电流限制

- 异步脉冲注入(API)和体二极管制动

- 40引脚LQFN封装

功能描述

- 内部补偿:采用内部集成器和直接放大的斜坡跟踪环,无需外部补偿,设计灵活、密集且简单。

- API和体二极管制动:分别通过显著减少下冲和过冲来改善瞬态性能。

- NexFET™ MOSFETs:低损耗开关,促进高效率,并在5mm x 7mm PowerStack™封装中提供高达40A的电流。

- 软启动:可编程软启动时间,控制启动时的涌入电流。

- 输入和VDD欠压锁定(UVLO)保护:具有固定阈值和迟滞,无需特定的上电顺序。

- 功率正常和使能:功率正常输出在输出电压达到目标时指示逻辑高,使能引脚控制转换器的开关。

- 电压参考:通过VSEL引脚配置初始启动电压值,范围为0.6V至1.1V。

- 内部斜坡发生器:通过MODE引脚配置内部斜坡幅度,优化控制环。

- 同步和堆叠配置:支持主从同步,实现相位交错,提高系统性能。

- API/体二极管制动:在负载阶跃上升时减少下冲,在负载阶跃下降时减少过冲。

- 过流保护:包括低侧和高侧MOSFET过流保护,确保系统安全。

- 过热保护:内部温度传感器防止热失控,具有自动恢复功能。

- 远程感应:RSP和RSN引脚用于远程感应,提高输出电压精度。

典型应用

- 独立设备:详细描述了4.5V至16V输入、1V输出、40A转换器的设计过程和组件选择。

- 堆叠配置:支持两台TPS543C20A设备堆叠,提供高达80A的点负载电流,同时实现电流共享、电压共享和时钟同步。

布局指南

- 热连接:所有GND引脚(包括AGND、GND和PGND)必须通过迹线或直接连接到器件下方的热焊盘。

- 电源组件布局:将电源组件(包括输入/输出电容、输出电感和TPS543C20A器件)放置在PCB的一侧(焊接侧)。

- 旁路电容:在VIN、VDD和BP引脚附近放置旁路电容,以最小化噪声。

- 敏感信号布局:将敏感模拟迹线和数字迹线分开,避免相互干扰。

设计资源

- WEBENCH® Power Designer:提供定制设计工具,帮助工程师快速设计满足需求的电源电路。

- 相关文档:包括应用报告、白皮书、用户指南等,提供详细的设计指导和参考。

封装和订单信息

- 封装类型:40引脚LQFN-CLIP封装

- 订单信息:提供了可订购的部件号、封装类型、引脚数、载带和卷盘尺寸等信息。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

TPS543C20 具有自适应内部补偿的 4V 至 14V、40A 同步 SWIFT™ 降压转换器数据手册2025-06-18 804

-

TPS543C20A SWIFT™降压转换器评估模块用户指南2024-11-24 429

-

具有自适应内部补偿功能的TPS543C20 4VIN至14VIN、40A可堆叠同步降压SWIFT™ 转换器数据表2024-04-25 363

-

具有内部补偿高级电流模式控制功能的4V至18V输入、3A同步 SWIFT™ 降压转换器TPS543320数据表2024-04-10 430

-

2.95V至16V、40A、高达4×可堆叠、PMBus® 降压转换器TPS546D24A数据表2024-04-03 499

-

具备自适应内部补偿功能的TPS543C20A4 VIN至16 VIN、40A可堆叠、同步降压SWIFT™ 转换器数据表2024-04-02 384

-

具有内部补偿高级电流模式控制功能的4V至18V输入、25A 同步SWIFT™ 降压转换器TPS543B25数据表2024-03-29 412

-

具有差分遥感功能的4V至16V输入、40A同步降压转换器TPS548D26数据表2024-03-26 508

-

具有内部补偿高级电流模式控制功能的4V至18V输入、16A同步SWIFT™ 降压转换器TPS543A26数据表2024-03-25 435

-

具有差分遥感的4V至16V输入、35A同步降压转换器TPS548C26数据表2024-03-21 473

-

TPS543C20A 具有自适应内部补偿功能的 4-16V 输入电压、40A、可堆叠同步降压 SWIFT™ 转换器2019-01-08 487

全部0条评论

快来发表一下你的评论吧 !