浮思特 | SiC MOSFET 封装散热优化与开尔文源极结构

描述

本文探讨了近期在碳化硅 (SiC) MOSFET 器件封装与设计方面的进展,重点关注顶部冷却封装方案及其在提升热性能、降低开关损耗方面的作用,以及开尔文源极连接结构对高频应用效率的优化效果。同时分析了新一代 SiC MOSFET 器件在平衡特定导通电阻 (Rsp) 与短路耐受时间 (SCWT) 方面的结构设计思路。

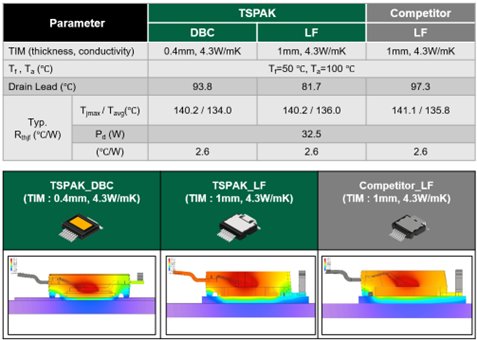

Power Master 扩展了其增强型碳化硅 (eSiC) MOSFET 产品系列,新增了符合 AEC-Q101 标准的高性能顶部冷却封装选项。这些封装包括 TSPAK DBC 版本和 LF 版本,主要面向汽车和工业应用。

这些器件采用 14mm x 18.58mm 的行业标准尺寸,并集成了开尔文源极连接设计,该设计有助于提升热性能并降低栅极噪声。这一方案降低了导通损耗,从而支持更高的功率密度和更高频率的运行。

图1

图1

该封装方案结合其新一代 1200V eSiC MOSFET (Gen2) 技术,优化了特定导通电阻 (Rsp) 与短路耐受时间 (SCWT) 之间的权衡关系。与前代产品相比,新型 1200V eSiC MOSFET 的开关损耗降低了 45%,导通电阻 (RDS(ON)) 降低了 20%,短路耐受时间 (SCWT) 提高了 15%。

顶部冷却封装方案

其开发的顶部冷却封装旨在满足高压应用的严格要求。为实现 3.6kV 的隔离电压和所需的宽爬电距离,设计中采用了如细长凹槽形状等方案。

Power Master 总监崔元硕 (Wonsuk Choi) 表示,经过设计优化,该封装的实际隔离电压超过 5kV,为安全性和可靠性提供了裕量。这些方案在紧凑设计中兼顾了绝缘和安全需求,提升了产品性能。

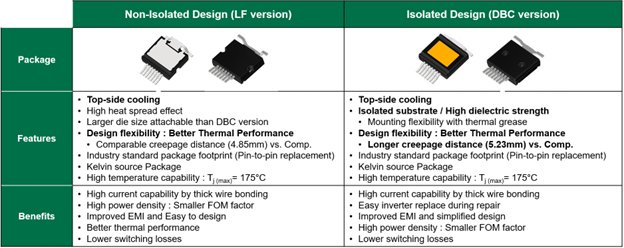

图2

图2

第二代 1200V eSiC MOSFET

新一代 1200V eSiC MOSFET 在器件性能上有所提升,特别是在特定导通电阻 (RDS(on)) 和短路耐受时间 (SCWT) 方面。这些改进通过一种新的器件结构实现,该结构平衡了 SiC 技术中固有的权衡关系。

崔元硕解释道:“沟道电阻是 RDS(on) 的主要来源,可通过缩小元胞间距来有效降低。然而,缩小元胞间距通常需要减小 JFET 区宽度,这又会因电流路径变窄而增加 JFET 电阻。新结构采用特定的掺杂分布,使得在较窄的 JFET 宽度下也能实现较低的 JFET 电阻。同时,缩窄 JFET 宽度还能通过限制高漏极偏压下的饱和电流来提升短路耐受能力。”

这种方法旨在提升器件在常见热应力和机械应力的严苛汽车环境中的效率和耐用性。

崔元硕提到:“新型 1200V eSiC M2 MOSFET 采用新的器件结构,在降低特定导通电阻 (Rsp) 的同时,也提高了短路耐受时间 (SCWT)。”

TSPAK 封装中的开尔文源极连接

TSPAK 封装为车载充电器 (OBC)、DC-DC 转换器和电动压缩机等多种汽车应用提供了良好的热性能、效率、功率密度和可靠性。

专为车载充电器 (OBC) 和 DC-DC 转换器等高频应用设计,TSPAK 封装集成了开尔文源极连接,通过降低导通损耗来优化效率。

崔元硕说明:“在用于 OBC 的图腾柱功率因数校正 (TP-PFC) 等拓扑中,开尔文源极连接有助于提升性能。对于开关频率较低但 EMI 要求严格的电机驱动应用,TSPAK 的开尔文源极连接能提供更纯净的栅源驱动电压信号,通过降低源极电感的影响,便于满足栅极电压限制要求。这使得 TSPAK 能适应不同应用场景,兼顾 EMI 性能和效率。”

据崔元硕介绍,TSPAK 的目标应用既包括开关频率较低、导通损耗为主的电机驱动(如电动压缩机),也包括开关频率较高、开关损耗为主的车载充电器 (OBC)。

扩展能力与规划

鉴于工业电源转换和电动汽车对 800V 系统的需求增长,Power Master 正在提升其制造能力。

顶部冷却封装技术与开尔文源极配置的结合,为 SiC MOSFET 在高频、高功率密度应用中的热管理和开关损耗控制提供了有效解决方案。

同时,新一代 SiC MOSFET 器件通过精细的元胞和 JFET 区结构优化,在降低 RDS(on) 和提升 SCWT 这一对矛盾指标上取得了平衡。这些技术进步共同推动了 SiC 功率器件在电动汽车电驱系统、车载充电、DC-DC 转换及工业电源等领域的更广泛应用。

-

浮思特|NMB散热风扇是什么品牌?为什么会被广泛使用?2025-09-18 1861

-

浮思特|SiC MOSFET与普通MOSFET的区别及应用分析2025-09-04 1044

-

SiC MOSFET 开关模块RC缓冲吸收电路的参数优化设计2025-04-23 1875

-

SiC MOSFET:桥式结构中栅极-源极间电压的动作2023-12-07 1373

-

如何使用电流源极驱动器BM60059FV-C驱动SiC MOSFET和IGBT?2023-02-21 10174

-

SiC MOSFET:桥式结构中栅极-源极间电压的动作-前言2023-02-08 1024

-

SiC-MOSFET器件结构和特征2023-02-07 1577

-

测量SiC MOSFET栅-源电压时的注意事项2022-09-20 20044

-

桥式结构中低边SiC MOSFET关断时的行为2022-07-06 2475

-

SiC功率器件SiC-MOSFET的特点2019-05-07 5705

-

用于C2M1000170J SiC MOSFET的辅助电源评估板CRD-060DD17P-22019-04-29 3661

-

SiC-MOSFET有什么优点2019-04-09 4694

-

沟槽结构SiC-MOSFET与实际产品2018-12-05 4853

-

SiC-MOSFET体二极管特性2018-11-27 10825

全部0条评论

快来发表一下你的评论吧 !