资料下载

×

如何通过3个方面来提高ADC优化时钟信号的转换速率概述

消耗积分:0 |

格式:rar |

大小:1.44 MB |

2018-05-24

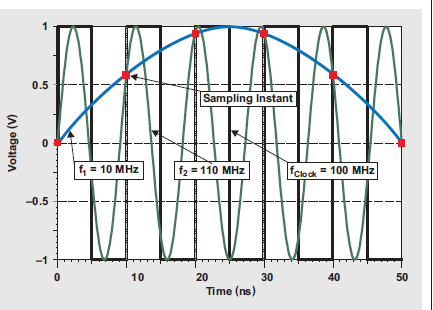

新的高速ADC配备了一个大的模拟输入带宽(约三至六倍的最大采样频率),因此它们可以用于欠采样应用。ADC设计的最新进展显著地扩展了可用的输入范围,使得系统设计者可以消除至少一个中频级,这降低了成本和功耗。在欠采样接收机的设计中,必须特别注意采样时钟,因为在较高的输入频率下,时钟的抖动成为限制信噪比(SNR)的主导因素。

这三部分文章系列的第1部分着重于如何准确地估计时钟源的抖动,并将其与ADC的孔径抖动相结合。在第2部分中,该组合抖动将用于计算ADC的SNR,然后将其与实际测量进行比较。第3部分将展示如何通过改善ADC的孔径抖动来进一步提高ADC的SNR,重点是优化时钟信号的转换速率。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章