资料下载

×

为什么高速ADC会有这么多的电源轨和电源域

消耗积分:3 |

格式:pdf |

大小:0.53 MB |

2020-11-24

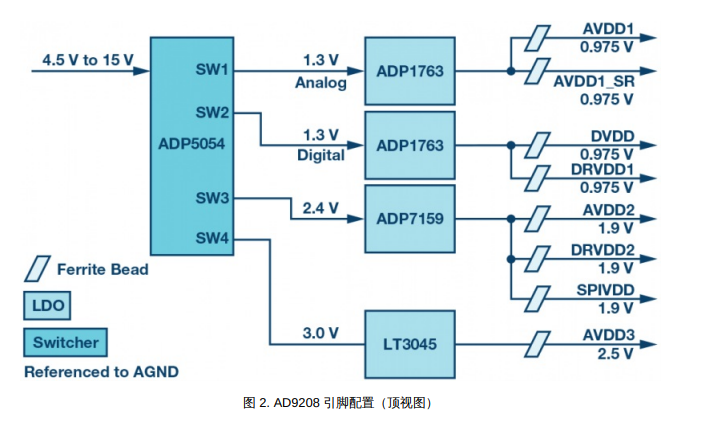

在采样速率和可用带宽方面,当今的射频模数转换器(RF ADC)已有长足的发展。其中还纳入了大量数字处理功能,电源方面的复杂性也有提高。那么,当今的 RF ADC 为什么有如此多不同的电源轨和电源域?为了解电源域和电源的增长情况,我们需要追溯 ADC 的历史脉络。早在 ADC 不过尔尔的时候,采样速度很慢,大约在数十 MHz 内,而数字内容很少,几乎不存在。电路的数字部分主要涉及如何将数据传输到数字接收逻辑——专用集成电路 (ASIC) 或现场可编程门阵列 (FPGA)。用于制造这些电路的工艺节点几何尺寸较大,约在 180 nm 或更大。使用单电压轨(1.8 V )和两个不同的域(AVDD 和 DVDD,分别用于模拟域和数字域),便可获得足够好的性能。随着硅处理技术的改进,晶体管的几何尺寸不断减小,意味着每 mm2 面积上可以容纳更多的晶体管(即特征)。但是,人们仍然希望 ADC 实现与其前一代器件相同(或更好)的性能。现在,ADC 的设计采取了多层面方法,其中: 1. 采样速度和模拟带宽必须得到改善; 2. 性能必须与前一代相同或更好; 3. 纳入更多片内数字处理功能来辅助数字接收逻辑。下面将进一步讨论上述各方面特性以及它们对芯片设计构成怎样的挑战。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章