奇异摩尔Die-to-Die片内互联方案持续升级

描述

当AI大模型参数规模突破万亿级别,传统单芯片设计遭遇物理极限。芯粒技术通过模块化组合突破瓶颈,而芯片间互联带宽成为决定性因素之一。近期,UCIe 3.0规范将数据传输速率从UCIe 2.0的32 GT/s提升至48 GT/s和64 GT/s两档,实现带宽密度翻倍增长。这对常受限于芯片面积内连接数量的芯片间通信至关重要。作为UCIe联盟的首批中国成员,奇异摩尔将积极参与并践行升级后的UCIe 标准,为客户带来更高性能、更具灵活性和可靠性的片内互联解决方案,为推动整个芯粒生态系统的发展贡献更多力量。

“芯粒时代”真正到来之前,产业界需要先解决一个根本问题:如何让不同工艺、不同厂商、不同功能的小芯片在封装里像乐高一样自由拼接,同时还能跑得快、功耗低、成本可控。

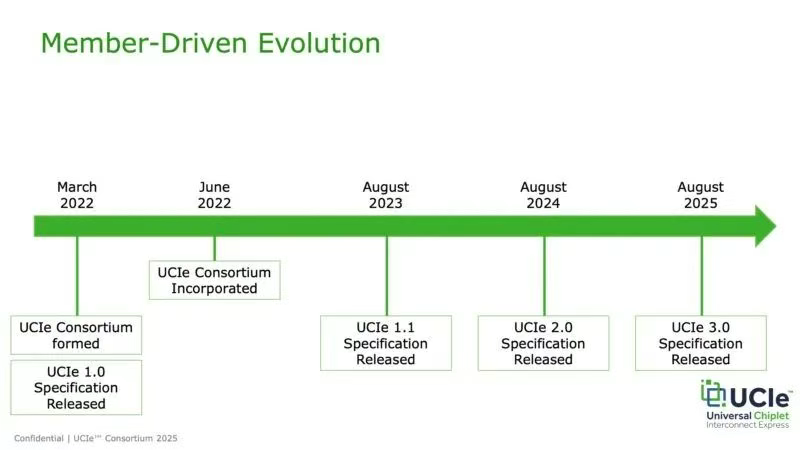

2022 年,英特尔、AMD、台积电、高通、谷歌、微软、Meta等 120 余家上下游企业共同成立 UCIe(Universal Chiplet Interconnect Express)联盟,目的就是给这个“乐高世界”制定统一的“接口语言”,实现来自不同供应商、在不同晶圆厂生产且具备不同功能的芯片,能够无缝集成到一个统一且可用的封装中,从而进一步提升系统的灵活性、效率和定制能力。同期,UCIe-Express 1.0规范正式发布。

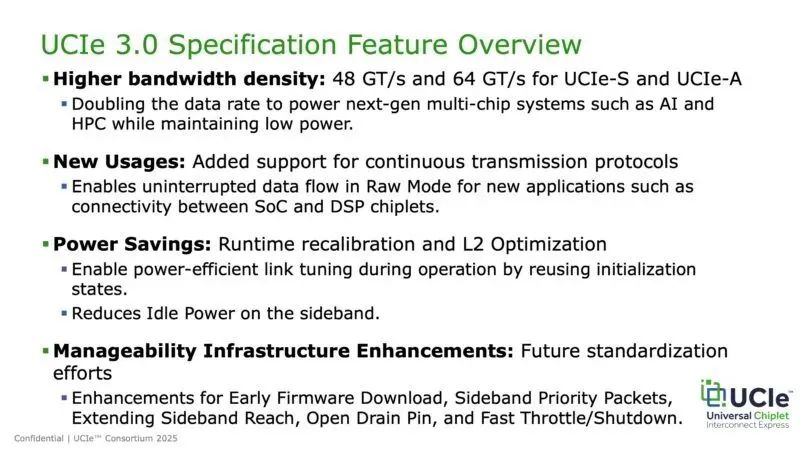

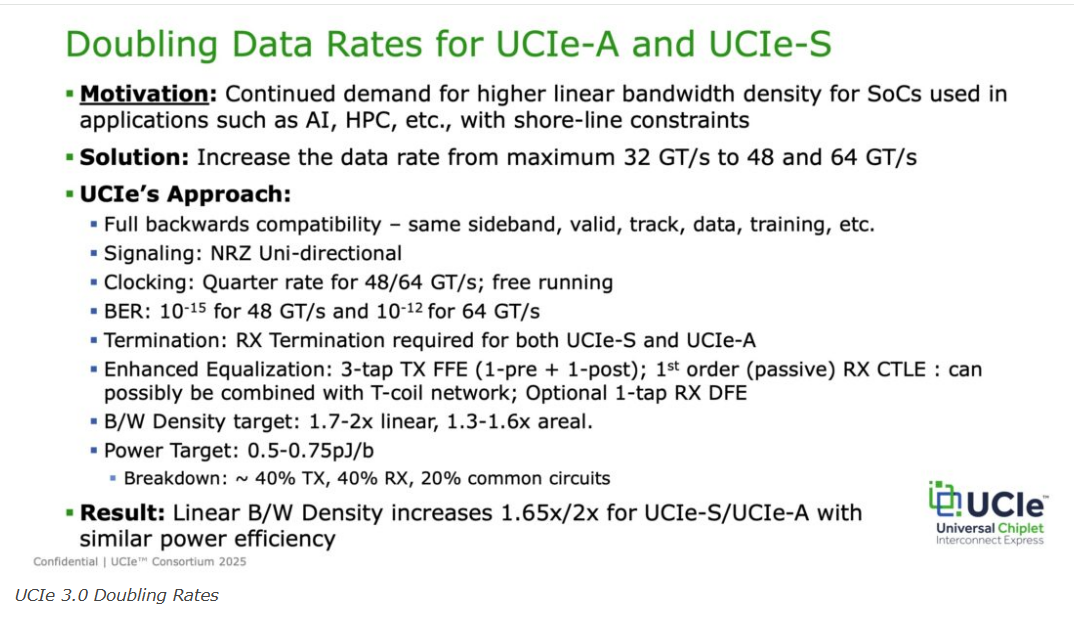

近日,UCIe-Express联盟(现已拥有超过140名成员)推出了开放式标准的3.0版本。新版本在能效、管理以及持续的向后兼容性方面进行了全面增强。其中,最引人注目的改进在于性能的大幅提升。新规范支持高达48 GT/s(每秒千兆传输)和64 GT/s的数据速率,是前一年推出的UCIe-Express 2.0规范所提供32 GT/s带宽的两倍。

这一性能飞跃有效应对了联盟所指出的对更高带宽“永不满足的需求”,特别是在人工智能、高性能计算和数据分析等快速发展的领域,这些领域高度受限于芯片间连接的物理空间。英特尔高级研究员兼UCIe-Express联盟主席Debendra Das Sharma表示:“这类限制在人工智能和高性能计算领域尤为明显。你需要在给定的空间内提供更多的带宽,但芯片尺寸不会仅仅因为需要更多带宽而改变。这就是我们提升数据速率的原因。”

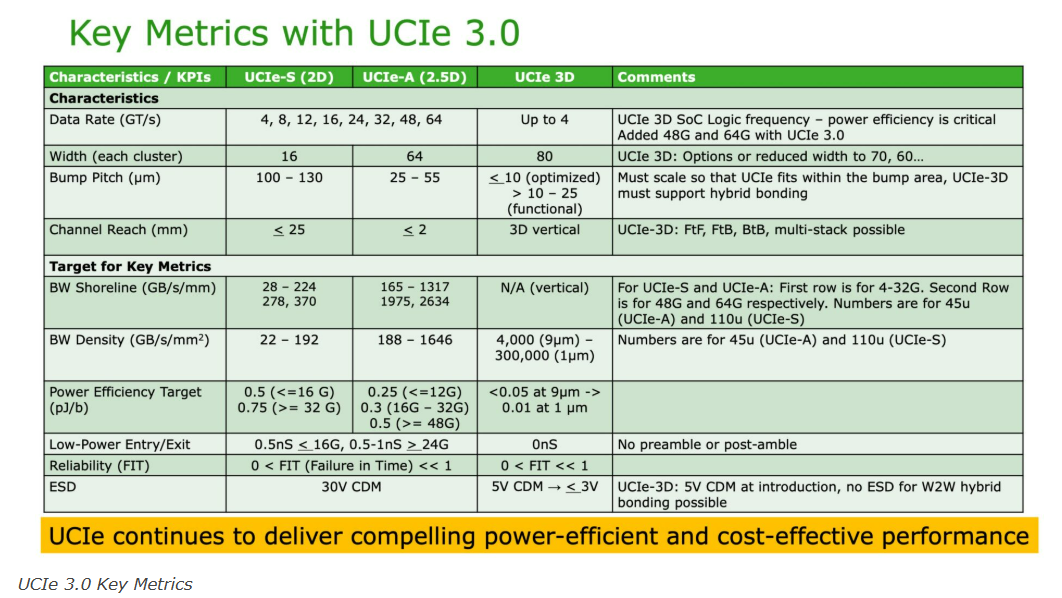

数据传输速率的翻倍提升同时适用于UCIe-Express-S(2D标准封装)和UCIe-Express-A(2.5D高级封装)设计。Das Sharma指出,3D设计方面并未进行改动。他解释道:“3D设计仍采用较低频率,原因是其采用的微凸点技术已能提供极高带宽——每平方毫米数百TB的带宽,甚至超出了当前需求,因此3D领域无需升级。而2D和2.5D方面需要在固定空间内提供更高的带宽。”

3.0版本的关键优势在于保持与旧版本的向后兼容性。联盟在一份白皮书中强调:“这是一个至关重要的考虑因素,因为它确保了现有系统和基础设施能够与新标准无缝集成,为系统设计人员和开发人员提供平滑过渡,同时确保了与按照前几代规范设计的旧芯片的互操作性。”

Das Sharma表示:“UCIe无处不在,我们将其视为与PCIe相当的标准,是一种板级互连技术,应用范围从手持设备一直延伸到数据中心,例如,UCI-Express A可能更适合高端小芯片,如人工智能芯片,因为手持设备不需要这种级别的带宽需求。正因如此,我们保留了2D版本。可以说,我们希望构建一个覆盖整个计算领域的连续标准。这个标准覆盖范围还包括数字信号处理器、无线基础设施和雷达系统等应用,以及人工智能、高性能计算、数据中心等所有领域。”

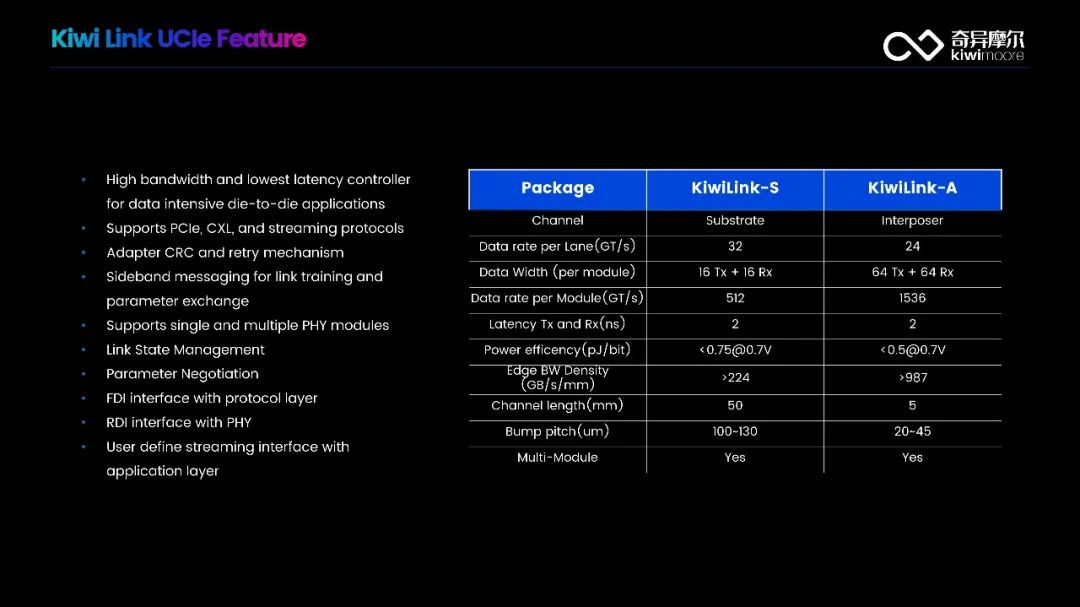

值得一提的是,奇异摩尔是国内最早一批加入UCIe 联盟的成员之一,深度参与到芯粒生态系统的建设与发展中。奇异摩尔提供完整的UCIe Die-to-Die IP解决方案,包括Controller,PHY和验证完成的IP。该款IP Standard版本以16-32Gbps的速度运行,实现芯粒之间的超高速互联通信,同时保持完全符合UCIe 1.1版本规范。

奇异摩尔的UCIe Die-to-Die IP包含基于了UCIe标准的低时延Controller(控制器),它包括Die-to-Die Adapter 和Protocol Layer 负责Sideband信息的收发实现Link bring up和Link magement,负责Mainband数据的发送和接收。UCIe Controller内部Die-to-Die Adapter和Protocol Layer之间支持FDI接口, UCIe Controller与PHY之间支持RDI接口。

奇异摩尔UCIe Die-to-Die IP提供了卓越的高带宽、极低延迟和较高的可兼容性。为了确保链路传输的可靠性,该IP支持CRC(循环冗余码)检查和重传机制。其设计适用于单模块和多模块配置,并能够应用于多种封装形式,包括标准封装及先进封装。其特点如下:

- 高带宽-16~32 GT/s 传输速率

- 低延时-ns级传输延迟

- 多协议-PCIe、CXL和Streaming等

- 国际标准-全系列支持UCIe标准

- 支持xPU间的Chip-to-Chip互联

此外奇异摩尔Kiwi Central IO Die 及Kiwi G2G-IOD 产品系列均基于UCIe协议设计,旨在打造规范且开源的芯粒互联互通系统。

UCIe 3.0 规范的发布为半导体行业带来了新的发展机遇和变革动力。未来,奇异摩尔将紧跟行业发展趋势,积极参与并践行升级后的UCIe 标准。凭借在AI互联领域的深厚技术积累和对 UCIe 标准的深刻理解,奇异摩尔有信心通过升级产品,充分发挥 UCIe 规范的优势,为客户带来更高性能、更具灵活性和可靠性的互联解决方案,为推动整个芯粒生态系统的发展贡献更多力量。

关于我们

AI网络全栈式互联架构产品及解决方案提供商

奇异摩尔,成立于2021年初,是一家行业领先的AI网络全栈式互联产品及解决方案提供商。公司依托于先进的高性能RDMA 和Chiplet技术,创新性地构建了统一互联架构——Kiwi Fabric,专为超大规模AI计算平台量身打造,以满足其对高性能互联的严苛需求。我们的产品线丰富而全面,涵盖了面向不同层次互联需求的关键产品,如面向北向Scale-out网络的AI原生超级网卡、面向南向Scale-up网络的GPU片间互联芯粒、以及面向芯片内算力扩展的2.5D/3D IO Die和UCIe Die2Die IP等。这些产品共同构成了全链路互联解决方案,为AI计算提供了坚实的支撑。

-

新思科技UCIe IP解决方案实现片上网络互连2025-08-04 2937

-

利用新思科技Multi-Die解决方案加快创新速度2025-02-25 1711

-

新思科技全新40G UCIe IP解决方案助力Multi-Die设计2025-02-18 1265

-

奇异摩尔32GT/s Kiwi Link Die-to-Die IP全面上市2024-12-10 2576

-

最新Chiplet互联案例解析 UCIe 2.0最新标准解读2024-11-05 3793

-

DDR4的单、双DIE兼容,不做仿真行不行?2024-08-05 1278

-

芯砺智能Chiplet Die-to-Die互连IP芯片成功回片2024-01-18 2205

-

Multi-Die系统验证很难吗?Multi-Die系统验证的三大挑战2023-12-12 2676

-

如何使用Die-to-Die PHY IP 对系统级封装 (SiP) 进行高效的量产测试?2020-10-25 3716

-

选择合适的 IP 实现 Die-to-Die 连接2020-05-18 8172

-

TPS40007-DIE 低输入、高效同步降压控制器,TPS40007-DIE2019-04-18 500

全部0条评论

快来发表一下你的评论吧 !