TSV封装是什么?整体封装的3D IC技术

制造/封装

描述

3D IC技术蓬勃发展的背后推动力来自消费市场采用越来越复杂的互连技术连接硅片和晶圆。这些晶圆包含线宽越来越窄的芯片。

为了按比例缩小半导体IC,需要在300mm的晶圆上生成更精细的线条。据市场研究机构VLSI Research(图1)预测,虽然目前大多数量产的IC是基于55nm或55nm以下的设计节点,但这些设计规则将缩小至38nm或更小,到2013年甚至会缩小到27nm。

这些尺寸缩小了的IC设计促进了人们对高密度、高成本效益的制造与封装技术的需求,进而不断挑战IC制造商尽可能地减少越来越高的固定设备投资成本。

许多3D应用仍使用传统的球栅阵列(BGA)、方形扁平无引线(QFN)、引线栅格阵列(LGA)和小外形晶体管(SOT)封装。不过,更多应用正在转向两种主要技术:扇出晶圆级芯片尺寸封装(WLCSP)和嵌入式裸片封装。

目前,扇出WLCSP主要用于采用BGA的多引脚数(超过120个引脚)应用。嵌入式裸片封装技术适合用于引脚数较少的应用,这些应用将芯片和分立元件嵌入PCB基板,并采用微机电系统(MEMS)IC(图2)。

图2:IC、MEMS器件和其它元件将采用了WLCSP和硅通孔(TSV)技术的无源器件组合在一起。

德州仪器(TI)的研究人员认为,WLCSP正在向标准化的封装结构发展。WLCSP可以包含WLCSP IC、MEMS IC和无源器件的组合,并且这些器件通过硅通孔(TSV)技术互连。TSV的底层可以是一个有源WLCSP器件、仅一个中介层或一个集成式无源中介层。顶层可以是一个IC、一个MEMS器件或一个分立器件(图3)。

但不管是哪种封装类型,随着引脚数量和信号频率的增加,预先规划封装选项的需求变得越来越重要。例如,带有许多连接的引线键合封装可能由于高感应系数而要求在芯片上提供更多的电源缓冲器。焊接凸点类型、焊盘以及焊球的放置也会极大地影响信号完整性。

TSV:言过其实还是事实?

TSV技术本质上并不是一种封装技术方案,而只是一种重要的工具,它允许半导体裸片和晶圆以较高的密度互连在一起。基于这个原因,TSV在大型IC封装领域中是一个重要的步骤。但TSV不是推动3D封装技术进步的唯一方法。它们仅代表众多材料、工艺和封装开发的一个部分。

事实上,采用TSV互连的3D芯片还没有为大批量生产作好准备。尽管取得了一些进步,但它们仍主要限用于CMOS图像传感器、一些MEMS器件以及功率放大器。超过90%的IC芯片使用经过验证的引线键合方法进行封装。

TI公司策略封装研究和外协部门经理Mario A.Bolanos在今年的ConFab会议上指出,在3D芯片中使用TSV面临许多挑战。这些挑战包括:缺少电子设计自动化(EDA)工具,需要极具成本效益的制造设备和工艺,与热问题、电迁移和热机械可靠性相关的良率和可靠性数据不达标,以及复合良率损失及已知合格芯片(KDG)数据等。

与在750μm厚的硅晶圆上制造的传统IC不同,3D IC要求晶圆非常薄,厚度通常约100μm甚至更薄。鉴于这种超薄晶圆的脆弱性,迫切需要极其专业的临时键合和解键合设备,以确保晶圆结构的完整性,特别是在蚀刻和镀金工艺期间的高处理温度和应力下。在键合完成后,晶圆要执行一个TSV背面工艺,然后进行解键合步骤。这些典型步骤可产生更高的良率水平,从而支持更具成本效益的批量生产。

目前,在键合和工艺温度及相关可靠性方面还缺少TSV标准。晶圆位置的TSV分配标准化也是如此。如果有足够多的IC制造商来研究这些问题,那么在扩展TSV的互连作用方面还可以取得更大的进展。超过200℃至300℃的高工艺温度对于TSV的经济实现来说是不可行的。

提供3D集成技术的知识产权(IP)的Ziptronix公司将直接邦定互连(DBI)技术授权给了Raytheon Vision Systems公司。据Ziptronix公司介绍,低温氧化物邦定DBI技术是3D IC(图4)的一种高成本效益解决方案。

但是,许多半导体IC专家认为半导体行业正处于选择2D(平面)和3D设计的十字路口。考虑到制造、设计、工艺和掩膜成本,他们发现在从45nm设计节点转向32nm和28nm设计时,成本会增加三倍至四倍。在蚀刻和化学蒸气抛光以及处理应力效应问题等方面还需很多改进,这使得3D封装挑战愈加严峻。而这正是TSV技术的合适切入点。

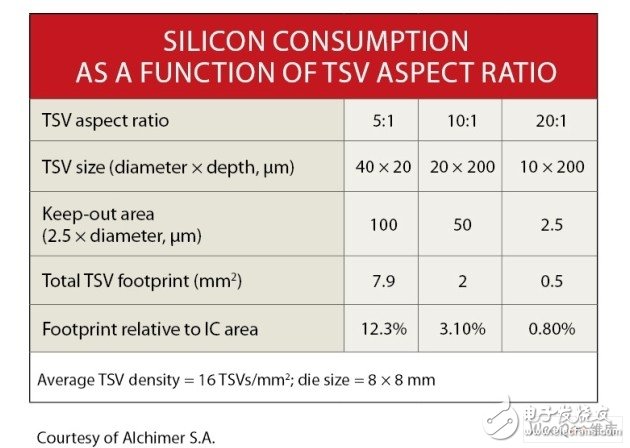

法国的Alchimer S.A.是一家提供用于半导体IC互连的纳米沉积薄膜的厂商,该公司已经验证,与高宽比为5:1(见表)的TSV相比,高宽比为20:1的TSV可以为IC芯片制造商每300mm晶圆节省超过700美元。这是通过减少互连所需的裸片面积实现的。

Alchimer公司利用现有面向移动应用的3D堆栈对TSV的成本和空间消耗建模。这个堆栈包括一个低功耗微处理器、一个NAND存储器芯片和一个65nm工艺节点上制造的DRAM芯片。芯片通过约1000个TSV互连,并对高宽比5:1、10:1和20:1下的处理器裸片进行了计算。

IBM、瑞士的école Polytechnique Fédérale de Lausanne(EPFL)和瑞士联邦理工学院(ETH)正在借助微流体MEMS技术(图5)联合开发面向3D IC(使用TSV)的微冷却技术。这项被称为CMOSAIC的合作正在探讨一种多核3D堆栈架构,其互连密度范围为100到10000个连接/mm2。

图5:未来的3D堆栈可能包含处理器、存储器、逻辑和模拟及RF电路,所有这些都通过TVS互连。流体通过MEMS微通道实现冷却。

IBM/瑞士团队计划用单相流体和两相冷却系统设计微通道。纳米表面将在几个毫米的芯片中用管道输送包括水和环保的制冷剂在内的冷却液,从而达到吸引热量和散热的目的。一旦流体以蒸气形式离开电路,冷凝器会使蒸气回复液体状态,然后再泵回芯片用于冷却。

引线键合和倒装芯片

引线键合和倒装芯片(flip-chip)互连技术当然不会坐以待毙。许多倒装芯片晶圆凸点技术取得了很大的进步,包括使用共熔倒装芯片泵、铜柱和无铅焊接。最新的封装发展包括使用封装上封装(PoP)方法、系统级封装(SiP)、无引线(QFN)封装以及它们的衍生技术。

3D结构已经享誉封装领域多年。在带有引线键合的堆叠式裸片结构中使用BGA封装已经近十年了。例如在2003年,意法半导体展示了一款采用BGA的10片堆叠结构,这在当时是创了记录的。

对于高密度和功能强的手持产品来说,像PoP概念这样的3D方法一定会引起人们的特别关注。设计工程师必须仔细考虑两个问题:热循环和跌落测试可靠性。两者都是封装材料质量和可靠性的函数。当PoP结构的底层互连间距从0.5mm变为0.4mm、顶层互连间距从0.4mm变为0.5mm时,这将变得更加重要。

三星电子(Samsung Electronics)发布了一款0.6mm高、多裸片、8芯片的封装,主要用于高密度存储器应用。据该公司透露,这种封装最初是为32GB存储器设计的,厚度只有传统8芯片存储器栈的一半,能为高密度多媒体手机和其它移动设备提供厚度和重量均缩减40%的存储器解决方案。

这种封装的重要创新之处是使用了30nm NAND闪存芯片,每颗芯片的厚度只有15 μm。三星公司设计了一种超薄技术来克服传统技术的局限性,即厚度在30μm以下时IC芯片抵抗外部压力的限制。此外,这种新的封装技术可以被应用于其它多芯片封装(MCP),如SiP和PoP。

“这一封装技术的发展为在目前的移动产品设计中整合更高密度和更多功能提供了最佳解决方案,从而使设计工程师能更自由地创造富有吸引力的设计,以满足当今用户对不同风格以及超薄喜好的需求。”三星公司封装开发部门副总裁Tae Gyeong Chung表示。

市场发展也在影响QFN封装领域。德国的Fraunhofer IZM公司开发出了一种聚合物内埋置芯片(chip-in-polymer)工艺,将冲击和震动保护嵌进芯片中,并使其互连距离缩短,从而增强芯片性能。这种工艺先使芯片变薄,然后将其粘附到很薄的基板上。

再用带树脂涂覆的铜全部覆盖表面(树脂层厚约80μm,铜表面厚5μm)。树脂被固化,互连过孔通过激光钻孔至连接焊盘,并用金属电镀。然后顶层上的再分配层被蚀刻掉铜。

这种工艺已经在QFN等标准封装的商业化生产中得到优化,而无需专门的设备或其它延迟。采用聚合体嵌入式QFN(其本质上是引线被芯片底面的焊盘取代的无引线方形封装)是HERMES项目的一部分。

HERMES由Fraunhofer公司和另外10家欧洲工业和学术机构组成,其目标是推进芯片和有源与无源器件的嵌入,以实现更多功能的集成和更高的密度。该技术基于PCB制造和装配实践的采用以及标准化的硅裸片,强调精细间距互连、大功率性能和高频兼容性。

选择QFN封装是因为它在包含微控制器IC的小型超薄设备中比较常见。Fraunhofer的研究人员相信,QFN将接管由其它类型封装控制的许多利基应用领域。嵌入式QFN包含一个厚度仅50μm左右的5x5mm大小芯片。封装本身的尺寸是100x100mm。芯片上的84个I/O引脚之间的间距是100μm(封装上为400μm)。

马来西亚的Unisem Berhad公司也发布了一种高密度引线框(leadframe)技术:引线框栅格阵列(LFGA),它能提供与BGA相当的密度。该公司表示,该技术为两层FPGA封装提供了高成本效益的替代方案。与QFN封装相比,它有更短的引线键合长度。此外,它能在5.5mm2的面积中容纳10x10mm、72引线的QFN封装。

“这种封装能提供更好的外形尺寸,同时具有更高的I/O密度和更好的热性能与电气性能。而且它更薄,最重要的是,能在前端装配中提供高得多的良率。”封装开发人员T.L.Li表示。

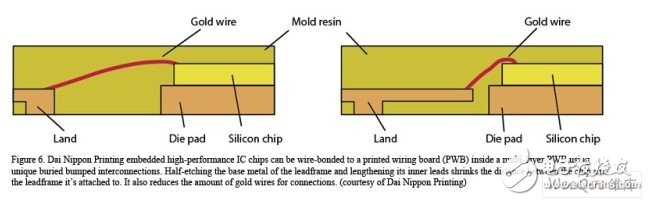

正在研究将芯片嵌入进各种介质的其它公司还包括Dai Nippon Printing。该公司成功地将引线键合至印刷线路板(PWB)的高性能IC芯片嵌入多层PWB中,其成功之处在于独特的埋入式凸出互连技术。PWB可在任意层间互连(通过孔连接),焊凸点则由通过丝网印刷术形成的高导电性锡膏生成。

对引线框的基础金属进行半蚀刻并使其内部引线变长将大幅缩短芯片与其连接的引线框之间的距离,同时显著减少用于连接的金线数量,最终降低制造成本(图6)。PWB内包含超过700个引脚的IC将在今年开始批量生产。有源和无源器件可以同时量产。

开发环氧助焊剂材料的工作还在进行,这种材料能改善传统锡银铜(SnAgCu)的热循环和跌落试验可靠性缺陷。开发这种材料将有助于提升采用PoP的3D IC技术。虽然PoP制造采用常用的锡铅(SnPb)焊接合金(比SnAgCu材料更具优势),但仍需要一种无铅化合物来处理面向消费电子产品的大型高密度3D PoP结构。

Henkel公司最新开发的多核LF620是一种无铅助焊剂,可用于大范围的封装应用。这种免清洗的无卤化物、无铅材料采用新的化学活性剂构成。因此,它通过焊盘内连接尽可能降低了CSP的空洞率,具有良好的接合性能,并在大量表面处理工艺下实现了卓越的可焊接性。

-

先进封装之TSV及TGV技术初探2023-05-23 5712

-

3D封装技术能否成为国产芯片的希望?#芯片封装面包车 2022-08-10

-

3D 模型封装2013-12-27 4243

-

3d封装2015-06-22 2751

-

3D PCB封装库2015-08-06 15083

-

altium designer 3D封装库2015-11-07 4015

-

带有3D的封装2015-11-27 4497

-

3D封装与硅通孔(TSV)工艺技术2011-12-07 2804

-

3D元件封装库2016-03-21 2684

-

什么是TSV封装?TSV封装有哪些应用领域?2018-08-14 92798

-

台积电完成全球首颗3D IC封装技术2019-05-04 2828

-

3D封装正当时!2023-06-21 1097

-

3D封装结构与2.5D封装有何不同?3D IC封装主流产品介绍2023-08-01 5254

-

2.5D和3D封装技术介绍2025-01-14 2784

-

3D封装架构的分类和定义2025-10-16 1483

全部0条评论

快来发表一下你的评论吧 !