资料下载

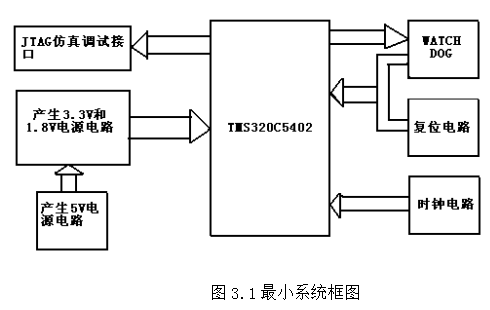

基于TMS320VC5402的DSP最小系统的详细资料介绍

DSP(Digital Signal Processor)是一种独特的微处理器,是以数字信号来处理大量信息的器件。其工作原理是接收模拟信号,转换为0或1的数字信号。再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。它不仅具有可编程性,而且其实时运行速度可达每秒数以千万条复杂指令程序,远远超过通用微处理器,是数字化电子世界中日益重要的电脑芯片。它的强大数据处理能力和高运行速度,是最值得称道的两大特色。

1.2 DSP的特点

DSP 芯片是模拟信号变换成数字信号以后进行高速实时处理的专用微处理器,其处理速度比最快的 CPU 还快 10-50 倍,具有处理速度高、功能强、性能价格比好以及速度功耗比高等特点,被广泛应用于具有实时处理要求的场合。

DSP 系统以 DSP 芯片为基础,具有以下优点。

1.高速性,DSP 运行速度高达 1000MIPS 以上

2.编程方便,可编程DSP 可使设计人员在开发过程中灵活方便的对软件进行修改和升级。

3.稳定性好,DSP 系统以数字处理为基础,受环境温度及噪声的影响比较小,可靠性高。

4.可重复性好,数字系统的性能基本上不受元器件参数性能的影响,便于测试、调试和大规模生产。

5.集成方便,DSP 系统中的数字部件有高度的规范性,便于大规模集成。

6.性价比高

2 TMS320VC5402 的硬件资源

TMS320VC5402 是 TI 的第七代 DSP 产品之一,它具有优化的 CPU 结构,内部有 1 个 40 位的算术逻辑单元(包括一个 40 位的桶式移位寄存器和 2 个独立的 40 位累加器),一个 17×17 的乘法器和一个 40 位专用加法器,16K 字 RAM 空间和 4K×16bit ROM 空间。共 20 根地址线,可寻址 64K 字数据区和 1M 字程序区,具有 64K I/O 空间。处理速度为 l00M IPS ,速度高、功耗低。

TMS320VC5402 采用修正的哈佛结构和 8 总线结构(4 条程序/数据总线和 4条地址总线),以提高运算速度和灵活性。在严格的哈佛结构中,程序存储器和数据存储器分别设在两个存储空间,这样,就允许取址和执行操作完全重叠。修正的哈佛结构中,允许在程序和数据空间之间传送数据,从而使处理器具有在单个周期内同时执行算术运算、逻辑运算、位操作、乘法累加运算以及访问程序和数据存储器的强大功能。与修正的哈佛结构相配合, TMS320VC5402 还采用了一个 6 级深度的指令流水线,每条流水线之间彼此独立,在任何一个机器周期内可以有 1 至 6 条不同的指令在同时工作,每条指令工作在不同的流水线上,使指令的执行时间减小到最小和增大处理器的吞吐量。

TMS320VC5402 的硬件结构具有硬件乘法器、8 总线结构、功能强大的片内存储器配置和低功耗设计的特点。因此,可以进行高速并行处理,同时,集成度高可节省硬件开销,提高系统抗干扰性。它除了完成数字信号处理任务外,还可以兼顾通用单片机的操作任务,因此,它是集数字信号处理与通用控制电路于一体的多功能低功耗微处理器。

综上所述 VC5402 的 CPU 结构特征如下。

(1)具有高性能的改进的哈佛总线结构,即具有三条独立的 16bit 数据存储器总线和一条 16bit 的程序存储器总线。

(2)具有一个 40bit 的算术逻辑单元,包括一个 40bit 的筒形移位器和两个独立的加法器。

(3)17×17bit 的并行乘法器与专用的 40bit 加法器相结合。

(4)具有专用于 Viter bi 蝶形算法的比较、选择、和存储单元(CSSU)。

(5)指数译码器可以在一个指令周期内求一个 40bit 累加数的指数值,这里的指数定义为累加器中没有数据占用的位数的个数减去 8。

(6)两个地址发生器、八个辅助寄存器和两个辅助寄存器算术单元(ARAU)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章