资料下载

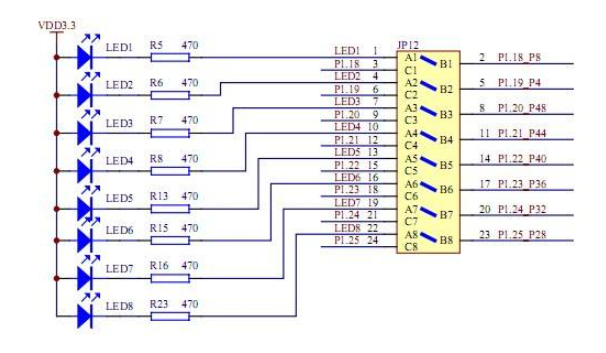

如何使用GPIO输出控制LED的亮灭详细资料和程序免费下载

1、CC2530的IO口概述

CC2530芯片有21 个数字输入/输出引脚,可以配置为通用数字I/O 或外设I/O 信号,配置为连接到ADC、定时器或USART外设。这些I/O 口的用途可以通过一系列寄存器配置,由用户软件加以实现。

I/O 端口具备如下重要特性:

21 个数字I/O 引脚

可以配置为通用I/O 或外部设备I/O

输入口具备上拉或下拉能力

具有外部中断能力。

21 个I/O 引脚都可以用作于外部中断源输入口。因此如果需要外部设备可以产生中断。外部中断功能也可以从睡眠模式唤醒设备。

2、未使用的I/O 引脚处理

未使用的I/O 引脚电平是确定的,不能悬空。一个方法是使引脚不连接,配置引脚为具有上拉电阻的通用I/O输入。这也是所有引脚复位后的状态(除了P1.0 和P1.1 没有上拉/下拉功能)。或者引脚可以配置为通用I/O输出。这两种情况下引脚都不能直接连接到VDD 或GND,以避免过多的功耗。

3、低I/O 电压

在数字I/O 电压引脚DVDD1 和DVDD2 低于2.6V 的应用中,寄存器位PICTL.PADSC 应设置为1,以获得DC 特性表中所述的输出DC 特性。

4、通用I/O

用作通用I/O 时,引脚可以组成3 个8 位端口,端口0、端口1 和端口2,表示为P0、P1 和P2。其中,P0和P1 是完全的8 位端口,而P2 仅有5 位可用。所有的端口均可以通过SFR 寄存器P0、P1 和P2 位寻址和字节寻址。每个端口引脚都可以单独设置为通用I/O 或外部设备I/O。(驱动电流很重要,有时候和MOS管电路、上拉电阻的选择等密切相关)除了两个高驱动输出口P1.0 和P1.1 各具备20 mA 的输出驱动能力之外,所有的输出均具备4 mA 的驱动能力。寄存器PxSEL(选择为通用IO模式还是外设IO信号),其中x 为端口的标号0~2,用来设置端口的每个引脚为通用I/O 或者是外部设备I/O 信号。作为缺省的情况,每当复位之后,所有的数字输入/输出引脚都设置为通用输入引脚。在任何时候,要改变一个端口引脚的方向,就使用寄存器PxDIR(选择输入或输出)来设置每个端口引脚为输入或输出。因此只要设置PxDIR 中的指定位为1,其对应的引脚口就被设置为输出了。当读取端口寄存器P0、P1 和P2 的值,不管引脚配置如何,输入引脚上的逻辑值都被返回。这在执行读-修改-写指令期间不适用。读-修改-写指令是: ANL,ORL,XRL,JBC,CPL,INC,DEC,DJNZ,MOV,CLR和SETB。在一个端口寄存器上操作,以下是正确的:当目标是端口寄存器P0、P1 或P2 中一个独立的位,寄存器的值,而不是引脚上的值,被读取、修改并写回端口寄存器。用作输入时,通用I/O 端口引脚可以设置为上拉、下拉或三态操作模式。作为缺省的情况,复位之后,所有的端口均设置为带上拉的输入。要取消输入的上拉或下拉功能,就要将PxINP(输入上拉、下拉、三态模式选择)中的对应位设置为1。I/O 端口引脚P1.0 和P1.1 没有上拉/下拉功能。注意配置为外设I/O 信号的引脚没有上拉/下拉功能,即使外设功能是一个输入。在电源模式PM1、PM2 和PM3 下I/O 引脚保留当进入PM1/PM2/PM3 时设置的I/O 模式和输出值(如果可用的话)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章